ADS仿真微带型lange耦合器学习笔记

ADS仿真微带型lange耦合器学习笔记

文章目录

- ADS仿真微带型lange耦合器学习笔记

-

- 一、 基本工作原理

- 二、 基本指标

-

-

- 耦合度

- 隔离度

- 定向度

- 插入损耗

-

- 三、ADS仿真设计实例

-

- 3.1 设计要求:

- 3.2 仿真流程和步骤:

-

- 1、新建一个工程

- 2、设计原理图

- 3、设计完成

- 4、微带基板的参数设置

- 5、lange耦合器的参数设置

- 6、原理图仿真

- 7、查看结果

- 8、添加VAR变量W,T和S

- 9、添加控件“Optim“和“Goal”到原理图中

- 10、双击“Optim“控件进行设置

- 11、进行优化

- 12、优化后的结果是满足要求的。

- 13、生成版图,进行仿真

- 14、添加端口,设置基材,扫频设置

- 15、查看结果

一、 基本工作原理

Lange耦合器结构如图,输入端口①的输入功率一部分直接传送给直通端口②,另外一部分耦合到耦合端口③,在理想的定向耦合器中,没有功率传送到隔离端口④。Lange耦合器的直通端口②与耦合端口③之间有90°的相位差,可见Lange耦合器是正交耦合器。Z0为输入输出微带线阻抗,W为微带线的宽度,S为微带线之间的间距,λ/4为工作带宽中心频点处的四分之一波长。

Lange耦合器的耦合系数常用C表示,影响耦合系数C的参数如下:

a) 线宽W

b) 缝隙宽度S

c) 基板介电常数

d) 导体厚度T

缝隙宽度S、微带线宽W和导体厚度T对耦合系数C有较大影响,而基板介电常数主要对特性阻抗有影响。

二、 基本指标

-

耦合度

耦合端口的输出功率对输入端口的功率的比值

-

隔离度

隔离端口的输出功率对输入端口的功率的比值

-

定向度

耦合端口的输出功率对隔离端口的输出功率的比值

-

插入损耗

直通端口的输出功率对输入端口的输入功率的比值

三、ADS仿真设计实例

(以ADS2016版本进行仿真设计,其他版本设置和仿真可能会不一致)

3.1 设计要求:

频率范围:0~20GHz;

中心频率fc:12GHz

在8~16GHz的输入驻波比:<1.2

在中心频点fc:12GHz的插损和耦合度:2.9dB < IL = C <3.1dB

在8~16GHz的定向度:D > 17dB

在8~16GHz的隔离度:I > 20dB

3.2 仿真流程和步骤:

1、新建一个工程

命名为“lange_coupler“,新建一个原理图cell,并命名为“lange_coupler”,一切采取默认设置即可。

2、设计原理图

加入微带lange耦合器和微带基片MSUB(在TLines-Microstrip中),并插入S_Params模板,并另外添加两个端口Term,用线连接起来,如图所示

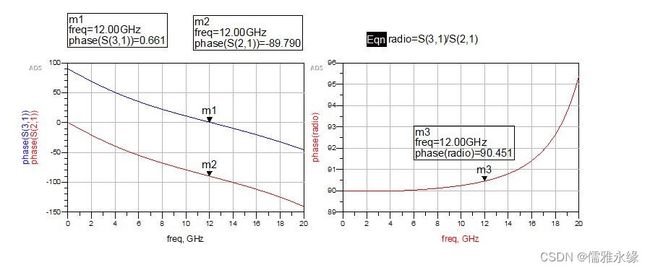

小技巧:在Simulation-S_Params中,可以插入等式控件,”MeasEqn”,在栏中输入“Radio =S(2,1)/S(3,1)“,如图所示。

3、设计完成

1端口为输入端,2端口为直通端,3端口为耦合端,4端口为隔离端,Radio为直通端口和耦合端口之间的相位差。

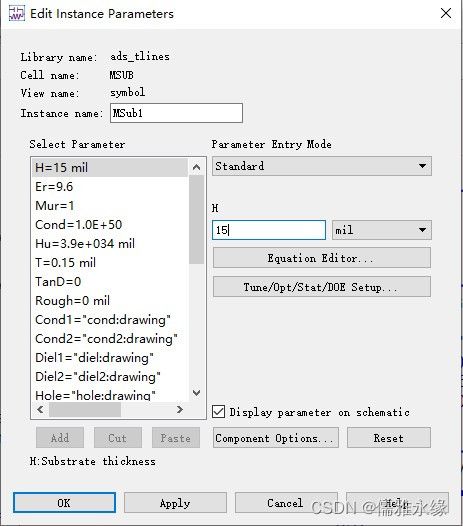

4、微带基板的参数设置

采用氧化铝作为微带线的介质基板,设置如图所示:

5、lange耦合器的参数设置

使用介电常数为9.6氧化铝基板制作3dB Lange耦合器有以下的经验公式:

W/H = 0.107, 其中W是微带线宽

S/H = 0.071,S为微带线之间的间距,H为微带线基板的厚度

L = λ/4,工作带宽中心频点处的四分之一波长。

计算得到 W = 1.605mil,S = 1.065mil,L = 100mil,设置参数如图:

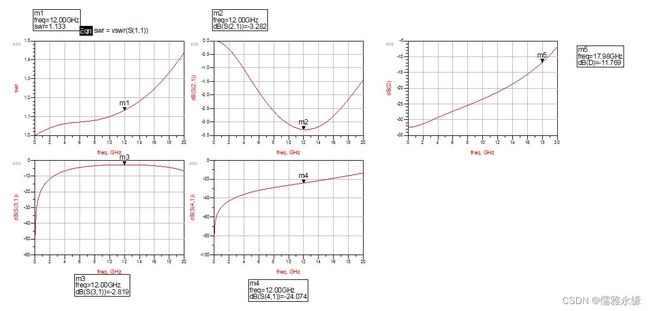

6、原理图仿真

扫频范围:0.01GHz~20GHz,step:0.01GHz,点击仿真,查看结果,可以将S(1,1)转换成VSWR,设置如下:

7、查看结果

结果明显不满足设计要求,接下来进行参数优化。

通过理论分析,微带线宽W,微带线间距S和导体厚度T对耦合系数C产生影响。

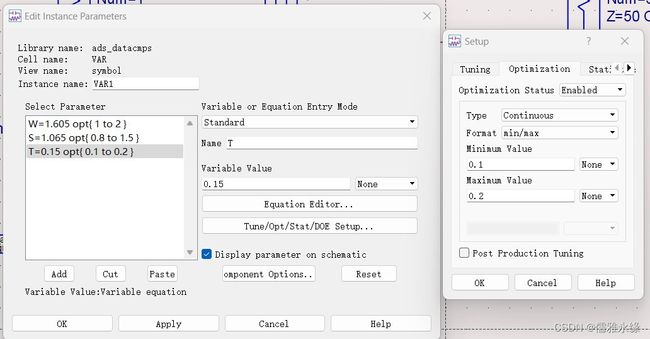

8、添加VAR变量W,T和S

W优化范围1-2,S优化范围0.8-1.5,T的优化范围为0.1~0.2(可以自行设置范围,如果没有达到条件可以适当加宽范围进行优化)

9、添加控件“Optim“和“Goal”到原理图中

(在“Optim/Stat/Yield/DOE“元器件库)

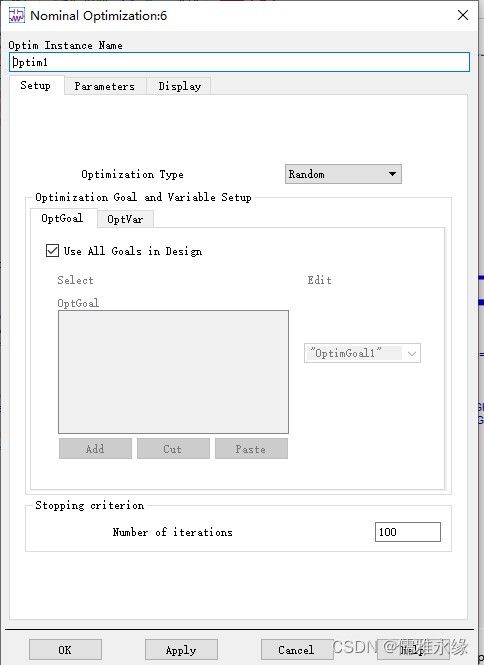

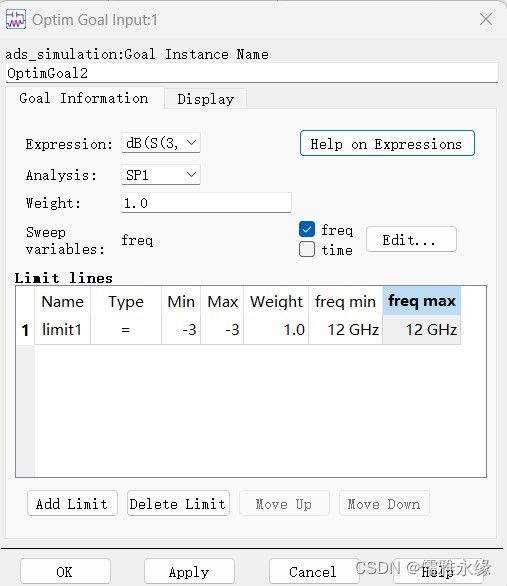

10、双击“Optim“控件进行设置

在“Optimization Type”栏中选择“Random”项,在Number of iterations 栏中数字为100。常用的优化方法有Random(随机),和Gradient(梯度)等。其中,随机法通常用于大范围搜索,梯度法则用于局部收敛。

11、进行优化

优化完成后查看各个指标是否满足要求,如果不满足在进行优化,记得把参数更新到原理图中,update design。

12、优化后的结果是满足要求的。

(注意:优化后查看结果发现之前的结果都是空白无效的,这时候就需要把参数更新到原理图中,重新仿真一下结果就出来了。)

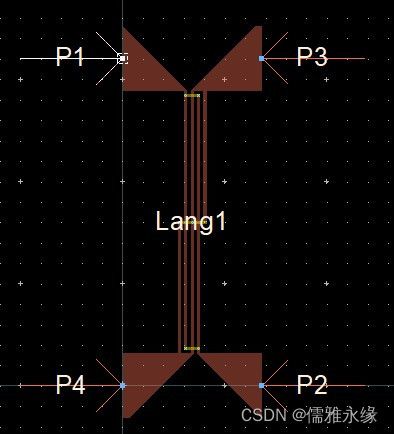

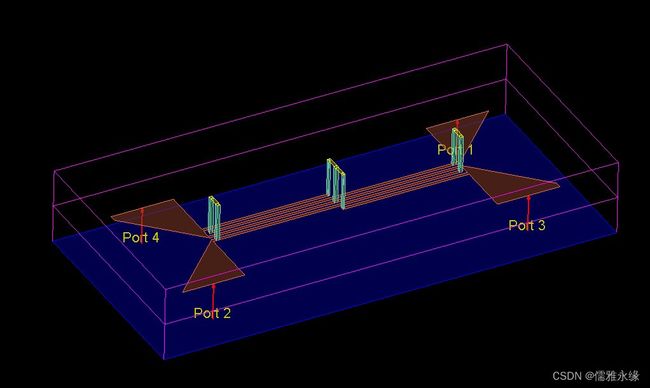

13、生成版图,进行仿真

将无关的器件进行失效,执行菜单命令Layout—Generate/update layout,如图所示

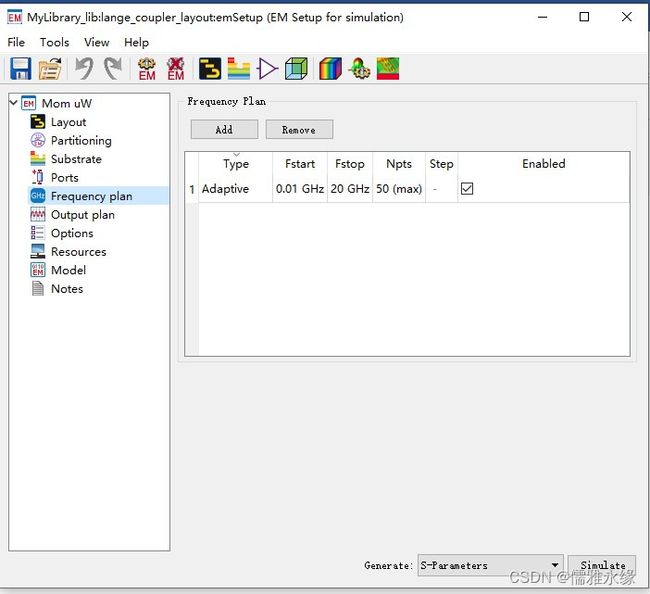

14、添加端口,设置基材,扫频设置

基材从原理图中导入进来的

这里不知道怎么修改的话,可以查看一下3D preview

15、查看结果

结果是有些恶化,需要在原理图重新进行优化,在进行版图仿真,这里不做进一步的优化。