Verilog学习笔记(三)-- 数字电路的逻辑运算

文章目录

- 前言

- 一、基本运算的真值表

- 二. 算数运算

-

- 2.1 加减乘除

- 2.2常数位移

- 三.关系操作

-

- 3.1 关系操作

- 四.位拼接与选取

- 4.1拼接

-

- 4.2 数据对齐要处理

- 4.3 数据选择

前言

一、基本运算的真值表

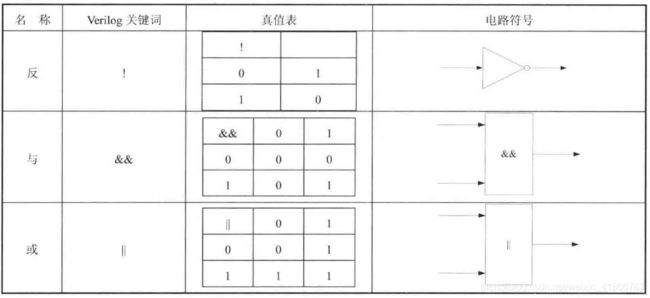

标量运算的逻辑运算(与或非)有以下几种:

1.逻辑取反(!):对1个操作数进行逻辑取反,如果这个操作数为0,则结果为1;如果这个操作数不为0,则结果为0。

2.逻辑与(&&):对2个操作数进行逻辑与,如果两者同为1或同不为0,则结果为1,否则为0。

3.逻辑或(I):对2个操作数进行逻辑或,如果两者其中至少有一个不为0,则

结果为1,否则为0.

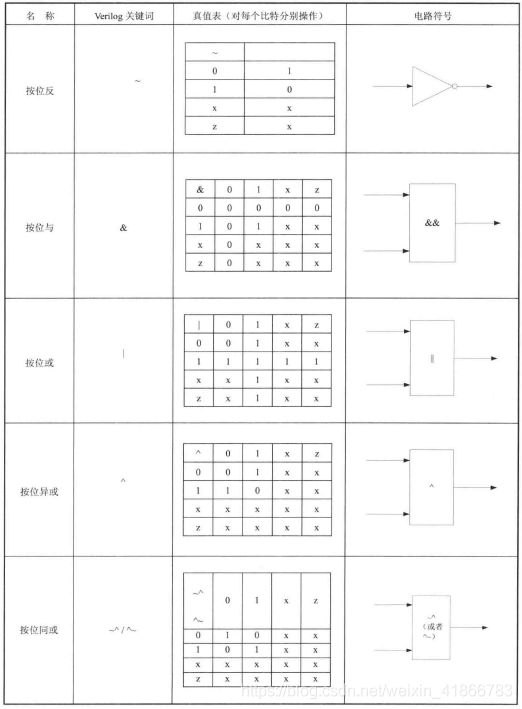

按位操作有以下几种:

1.按位取反(~):

1个多位操作数按位取反。例如,a=4b1011,则~a的结果为4b0100。

2.按位与(&):

2个多位操作数按位进行与运算,各位的结果按顺序组成一个新的多位数。例如,a=2bl0,b=2b11,则a&b的结果为2bl0。

3.按位或(|):

2个多位操作数按位进行或运算,各位的结果按顺序组成一个新的多位数。例如,a=2b10,b=2"b11,则ab的结果为2b1l。

4.按位异或(^):

2个多位操作数按位进行异或运算,各位的结果按顺序组成个新的多位数。例如,a=2"b10,b=2b11,则a^b的结果为2b01

5.按位同或(^或^):

2个多位操作数按位进行同或运算,各位的结果按顺序组成一个新的多位数。例如,a=2b10,b=2bl1,则a~^b的结果为2b10。

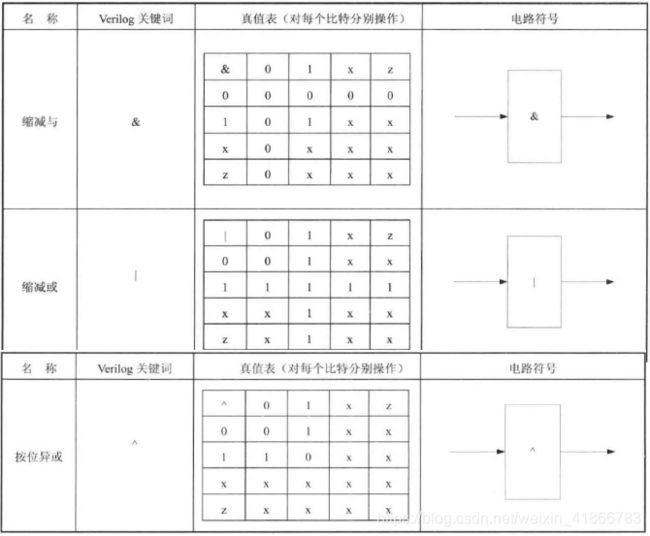

缩减操作:

1.缩减与(&):对一个多位操作数进行缩减与操作,先将它的最高位与次高位进行与操作,其结果再与第二次高位进行与操作,直到最低位。例如,&(4b1011)的结果为0。

2.缩减与非(~&):

对一个多位操作数进行缩减与非操作,先将它的最高位与次高位进行与非操作,其结果再与第二次高位进行与非操作,直到最低位。例如,~&(4b1011)的结果为1.

3.缩减或(|):对一个多位操作数进行缩减或操作,先将它的最高位与次高位进行或操作,其结果再与第二次高位进行或操作,直到最低位。例如,(4b101)的结果为1。

4.缩减或非(~):

对一个多位操作数进行缩减或非操作,先将它的最高位与次高位进行或非操作,其结果再与第二次高位进行或非操作,直到最低位。例如,~(4b1011) 的结果为0。

5.缩减异或(^):

对一个多位操作数进行缩减异或操作,先将它的最高位与次高位进行异或操作,其结果再与第二次高位进行异或操作,直到最低位。例如,^(4b1011)的结果为1。

6.缩减同或(~^ or ^~):

对一个多位操作数进行缩减同或操作,先将它的最高位与次高位进行同或操作,其结果再与第二次高位进行同或操作,直到最低位例如,~^(4b1011)的结果为0。

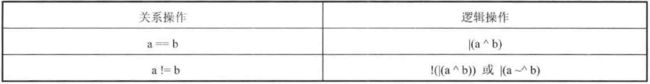

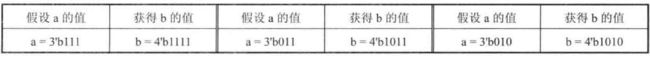

一些关系操作举例:

二. 算数运算

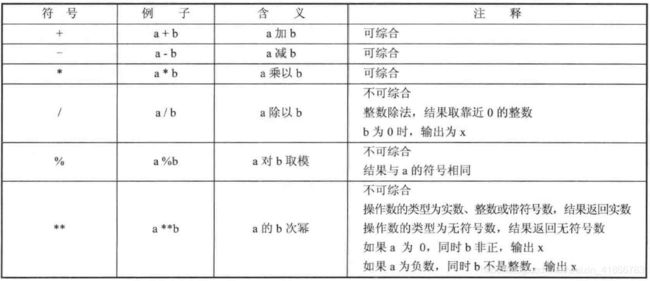

2.1 加减乘除

算数运算符如下:

注:除法运算在FPGA里可以实现,但实现起来很复杂,尽量避免使用。

2.2常数位移

移位操作主要有以下几种:

1.逻辑右移(>>):1个操作数向右移位,产生的空位用0填充。

2.逻辑左移(<<):1个操作数向左移位,产生的空位用0填充。

3.算术右移(>>):1个操作数向右移位。如果是无符号数,则产生的空位用0填充;有符号数则用其符号位填充。

4.算术左移(<<<):1个操作数向左移位,产生的空位用0填充。

注:在verilog中移位的数必须是常数,否则无法综合。

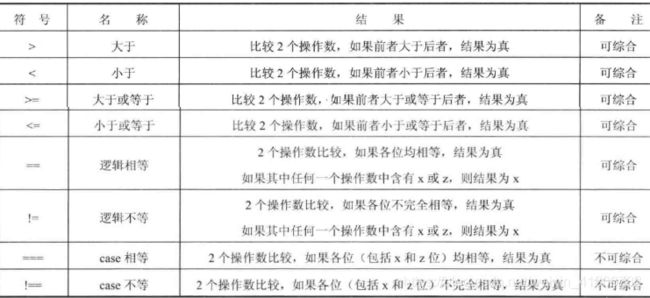

三.关系操作

3.1 关系操作

四.位拼接与选取

4.1拼接

拼接的操作符是大括号“{}”。一般格式为:

{signal1, signal2,....}

其中,信号(signal)既可以是常数也可以是变量,但位宽必须已知且不变。

例子:

wire [2:0] a;

wire [3;0] b;

assign b = {1'b1, a[2:0]}; #每个数必须指定位宽

拼接操作可以代替位移操作,甚至可以完成所谓的循环位移操作。例如:

4.2 数据对齐要处理

拼接操作可以把信号放入一个集合,一般把逻辑上有联系的信号放在一起。例:

Control_Bus = {enable, wr_enable, rd_enable, configure_enable}

#定义完后可以使用如下的操作

module bus_module(Control_Bus, Date_Bus, ...)

#在模块中可去如下提取元素

wr_enable_from_bus = Control_Bus[2]

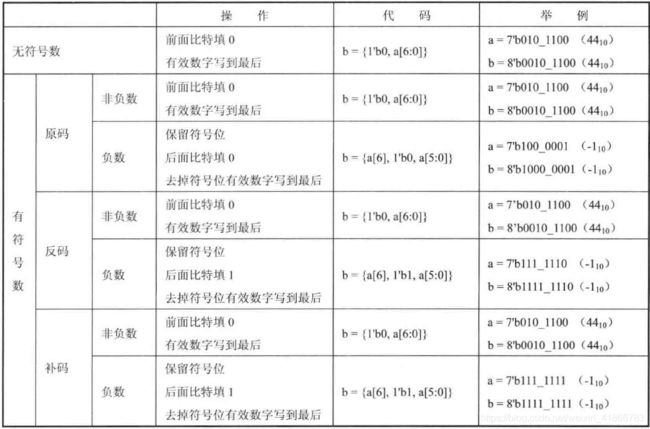

数值对齐采用“就高不就低”,数值的比特位扩展:

在不影响精度的情况下,数据可以截断:

注:对于有符号数的反码和补码,截位不是都向零取整的。

4.3 数据选择

一般的选择形式:

当condition为真时,输出value1。当condition为假时输出Value2.