微机原理与接口技术 学习笔记(三) 中断系统与8259A(DMA待添加)

文章目录

- 一,中断

-

-

- 1.0 中断概述

-

-

- 1.0.1 中断概念(略)

- 1.0.2中断系统作用:

-

- 1.1 中断处理系统

-

-

- 1.2.1 中断源识别(略)

- 1.2.2 中断优先级判断

- 1.2.3 中断嵌套管理(略)

- 1.2.4 中断处理过程

-

- 1.2 8086 中断系统

-

-

- 1.2.1 中断源的类型

-

- 外部中断(硬件中断)(真~中断)

- 内部中断(软件中断)(也叫异常)

- 1.2.2 中断源的优先级

- 1.2.3 中断类型号 和 中断向量表

-

- 中断类型号

- 中断向量

- 中断向量表

-

- 1.3 中断控制器 Intel 8259A

-

-

- 1.3.1 8259A的引脚信号

- 1.3.2 8259A 内部结构

-

- (1)数据总线缓冲器

- (2)读 / 写控制逻辑

- (3)级联缓冲/比较器

- (4)中断请求寄存器 IRR

- (5)中断服务寄存器 ISR

- (6)中断屏蔽寄存器 IMR

- (7)优先权比较器 PR(裁决器)

- (8)中断控制逻辑

- 1.3.3 8259A 的工作方式

-

- (1)中断请求方式(三种)

- (2)中断屏蔽方式(2种)

- (3)中断嵌套方式(2种)

- (4)优先级循环方式(2种)

- (5)中断结束方式(2种)

- (6)读 8259A 的状态:

- 1.3.4 8259A 的编程

-

- 初始化编程 (初始化命令字: I C W 1 ICW_1 ICW1~ I C W 4 ICW_4 ICW4)

- 工作方式编程 (操作命令字: O C W 1 OCW_1 OCW1~ O C W 3 OCW_3 OCW3)

- 常用编程

-

- 初始化 8259A

- 放中断服务地址

-

-

一,中断

1.0 中断概述

1.0.1 中断概念(略)

1.0.2中断系统作用:

- 能实现并行处理

- 能实现实时处理

- 能实现故障处理

1.1 中断处理系统

一个完整的中断处理系统必须实现以下功能:

- 中断源识别

- 中断优先级判断

- 中断嵌套管理

- CPU 的中断响应

- 中断服务

- 中断返回

1.2.1 中断源识别(略)

引起程序中断的事件称为中断源

1.2.2 中断优先级判断

先响应优先级别最高的中断申请

具体方法:

- 软件查询

- 硬件排队

- 专用中断控制器

1.2.3 中断嵌套管理(略)

1.2.4 中断处理过程

基本过程应包括5个基本阶段:

- 中断请求

- 中断优先级判断

- 中断响应

- 中断服务

- 中断返回

1.2 8086 中断系统

- 8086的中断系统采用向量中断机制

- 能够处理256个中断,用中断向量号0 - 255区别

- 可屏蔽中断还需要借助专用中断控制器Intel 8259A实现优先权管理

- 256 个中断,对应256个中断源,对应256个中断服务程序,对应256个中断向量,对应256个中断类型号,对应256个向量号

1.2.1 中断源的类型

外部中断(硬件中断)(真~中断)

8086提供两条外部中断请求线,和一条与中断有关的控制线:NMI,INTR, INTA(中断响应)。

- 非屏蔽中断(不可屏蔽中断)向量号:2

非屏蔽中断请求信号为NMI - 可屏蔽中断

8088的可屏蔽中断请求和响应信号分别是INTR和INTA*;由IF标志控制可屏蔽中断是否允许响应;向量号来自外部中断控制器

见8259就明白了

内部中断(软件中断)(也叫异常)

- 单步中断 向量号:1 (单步调试)

- 除法出错中断 向量号:0

- 断点中断 向量号:3

- 溢出中断 向量号:4

- 指令中断,就是 INT n 软件弄出任意向量号的中断

1.2.2 中断源的优先级

由高到低:

- 除法出错中断

- 软件中断 INT n

- 溢出中断 INTO

- 非屏蔽中断 NMI

- 可屏蔽中断 INTR

- 单步中断

1.2.3 中断类型号 和 中断向量表

中断类型号

8086用0-255来区分256个不同中断源,并对应给出中断向量。

0~4: 5个内部中断,有固定的定义和处理功能;

5~31:系统保留,用户一般不应使用

32~255:用户使用作为硬件或软件中断,也可不用,作为数据存储区。

中断向量

8086/8088系统支持最多256个中断,对应每一个中断,都有一个中断服务程序,该中断服务程序的入口地址称为中断向量。

每个中断向量占用4个字节,前两个字节(低位)为服务程序的IP(偏移量),后两个字节(高位)为服务程序的CS(段地址)。低字节在低位,高字节在高位。

中断向量表

256中断向量构成一个中断向量表,放在(内存的最低区域)0段的0~3FFH区域内,每个占4个字节

存放中断向量的位置=中断类型号×4(0段)开始的4个内存单元。

!!!用户在使用中断服务程序之前,必须采取一定的方法,将中断服务程序的入口地址送到与中断类型相应地中断向量表中。(中断服务程序是自己定义的)

1.3 中断控制器 Intel 8259A

中断申请管理接口的主要功能:

- 向CPU的引脚INTR发中断申请信号

当有多个外设同时发出中断请求时,

能按照一定的优先级顺序,向CPU发出中断申请,

使CPU能优先响应优先级最高的外部设备的中断申请。 - 送中断类型号

在CPU中断响应周期,针对不同外设的中断请求,

向CPU传送不同的中断类型号,

使CPU执行相应的中断子程。

可编程中断控制器 8259A 是专门用于微型计算机系统中断管理的大规模集成电路芯片。用于管理Intel 8080/8085、8086/8088、80286/80386的可屏蔽中断。

8259A的基本功能

- 一片8259A可以管理8级中断,可扩展至64级(级联扩展)

- 每一级中断都可单独被屏蔽或允许

- 在中断响应周期,可提供相应的中断向量号

- 可通过编程选择8259A的多种工作方式,及任意设定中断类型号。

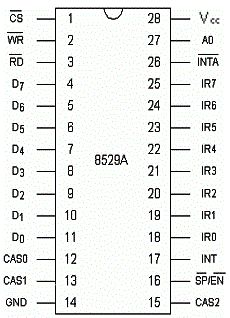

1.3.1 8259A的引脚信号

- D0~D7: 8条数据线,与CPU数据总线相连,进行数据交换,写入控制字或送出类型号。(双向,三态)

- INT:中断请求,与CPU INTR相连发出中断申请。(输出)

- I N T A ‾ \overline {INTA} INTA::接收来自CPU的响应信号,一般两个负脉冲。(输入)

- R D ‾ \overline {RD} RD:读信号,使8259A将要输出的内容送到数据总线上。(输入)

- W R ‾ \overline {WR} WR:写信号,使8259A从数据总线上接受数据。(输入)。

- C S ‾ \overline {CS} CS: 片选信号(输入)

- A 0 A_0 A0:1片8259A占用两个端口地址,一个偶地址(A0=0),一个奇地址(A0=1)。

- I R 0 {IR}_0 IR0 ~ I R 7 {IR}_7 IR7: 分别接8个外设中断请求或从片中断请求(电平触发或边沿触发)。(输入)

- C A S 0 {CAS}_0 CAS0 ~ C A S 2 {CAS}_2 CAS2:主从结构,实现级联(双向)

- S P ‾ \overline {SP} SP/ E N ‾ \overline {EN} EN: 双向线,(由初始化命令字设置)

非缓冲方式:输入 S P ‾ \overline {SP} SP=1本片主片, S P ‾ \overline {SP} SP=0本片主片(输入)

缓冲方式:输出 E N ‾ \overline {EN} EN=0有效,数据从8259传向8086时,启动数据总线驱动器 (输出)

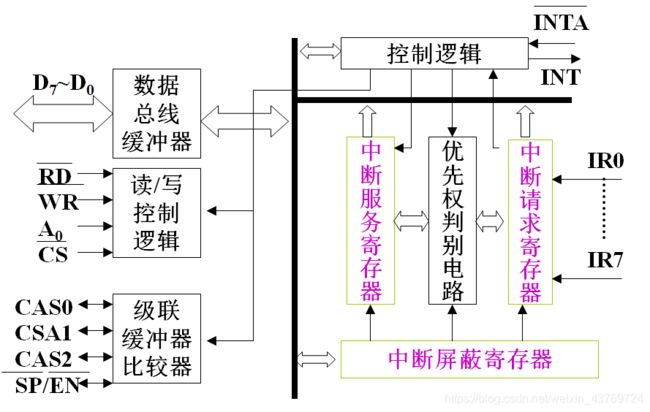

1.3.2 8259A 内部结构

(1)数据总线缓冲器

8位三态双向缓冲器,常与 8086 低8位数据总线 D 0 D_0 D0~ D 7 D_7 D7 相连,相应将CPU地址总线的 A 1 A_1 A1 和 8259A 的 A 0 A_0 A0相连?

(2)读 / 写控制逻辑

读 / 写控制逻辑用于接收 CPU 的读/写命令 R D ‾ \overline {RD} RD, W R ‾ \overline {WR} WR,以及片选信号 C S ‾ \overline {CS} CS 和 端口选择信号 A 0 A_0 A0:。

- 写,把来自 CPU 的初始化命令字 ICW 和操作命令字 OCW 存入8259A 内部相应的端口寄存器,以规定 8259A 的工作方式和控制模式。

- 读,可使CPU通过它读取 8259A 内部有关端口寄存器的状态信息。

(3)级联缓冲/比较器

I R 0 {IR}_0 IR0 ~ I R 7 {IR}_7 IR7

扩展中断级,最多至64级。多片连接时,一片为主片,其余为从片。

(4)中断请求寄存器 IRR

- IRR 是一个8位的具有锁存功能的寄存器。

- 保存8条外界中断请求信号IR0~IR7的请求状态

- Di位为1表示IRi引脚有中断请求;为0表示无请求

(5)中断服务寄存器 ISR

- ISR 是一个8位寄存器,用于寄存当前所有正在被服务的中断级。

- 在中断响应的第一个 INTA 周期将 ISR 的相应位置“1”。

- ISR 的复位由8259A 中断结束方式决定:

- 若是自动结束方式:则由 CPU 在第二个INTA 周期后沿将其复位。

- 若是非自动结束方式:则由 CPU 发送的中断结束命令将其复位。

- 允许多重中断时,ISR 有多位同时被置成“1”。

(6)中断屏蔽寄存器 IMR

- IMR 是一个8位寄存器,用于寄存要屏蔽的中断级。

- 对应位为“1”,表示屏蔽该级中断请求; 对应位为“0”,表示开放该级中断请求。

- 该寄存器内容可以同构屏蔽命令由软件设置。

- 较高优先级的屏蔽不影响低级中断,即 各级屏蔽位是是独立的。

(7)优先权比较器 PR(裁决器)

用以比较正在处理的中断和刚刚进入的中断请求之间的优先级别,以决定是否产生多重中断或中断嵌套。

(8)中断控制逻辑

控制逻辑是8259A 的内部控制器。

根据中断请求寄存器IRR 和 中断屏蔽寄存器IMR 通过 优先权比较器PR判断优先级,向 8259A 内部及其他部件发出控制信号,并向 CPU 发出中断请求信号 INT 和接收 CPU的中断请求信号 I N T A ‾ \overline {INTA} INTA,使中断服务寄存器 ISR 相应位置“1”,并使中断请求寄存器 IRR 相位复“0”。

当CPU 的第二个 I N T A ‾ \overline {INTA} INTA 信号到来,控制 8259A 送出中断类型号,使CPU 转入中断服务子程序。

若是中断结束方式为自动结束方式,则在第二个INTA 周期后沿将中断服务寄存器ISR复位。

1.3.3 8259A 的工作方式

8259A 有 6 种工作方式:

- 中断请求方式

- 中断源屏蔽方式

- 中断嵌套方式

- 优先级循环方式

- 中断结束方式

- 读8259A 状态方式

这些工作方式都是通过 8259A 的初始化命令字( I C W 1 {ICW}_1 ICW1~ I C W 4 {ICW}_4 ICW4)和操作命令字( O C W 1 {OCW}_1 OCW1~ O C W 4 {OCW}_4 OCW4)来设定。

(1)中断请求方式(三种)

-

边沿触发器方式(中断请求输入端出现上升沿触发信号)

-

电平触发方式(只有中断请求输入端出现高电平信号才能实现中断请求)

-

中断查询方式 (8259A向CPU发送INT信号,但是CPU可以不理(关中断IF),而是靠CPU不断查询8259A)

查询时:系统先关中断,然后将查询方式命令字 O C W 3 {OCW}_3 OCW3送到8259A,再对8259A执行一条输入指令,8259A 便将查询字送上数据总线。查询字格式如下:7 D6 D5 D4 D3 D2 D1 D0 W2 W1 W0 I=1表示 有中断请求

W2W1W0 表示当前中断源请求的最高优先级。

(2)中断屏蔽方式(2种)

- 普通屏蔽方式

通过编程将中断屏蔽字写入 IMR 实现。写“1”屏蔽,写“0”开放。 - 特殊屏蔽方式

为了使进行某较高级中断时,能够开放较低级的中断请求。

设置特殊屏蔽方式后,用屏蔽字对IMR 中某位置“1”时,同时将 ISR 中对应位清“0”。

注意顺序:先设置特殊屏蔽方式,再建立屏蔽

中断服务程序结束时应退出特殊屏蔽方式

(3)中断嵌套方式(2种)

全嵌套方式 和 特殊嵌套方式。

- 全嵌套方式:

是8259A进行初始化以后的默认工作方式。

特点是:中断优先级管理为固定方式, I R 0 {IR}_0 IR0优先级最高, I R 7 {IR}_7 IR7优先级最低。

执行中断服务时,禁止响应同级或低级中断请求。只能响应比当前服务中断级别高的。 - 特殊全嵌套方式:

级联的情况下需采用特殊全嵌套方式。

与全嵌套基本相同,区别是允许同级中断请求响应。

主片特殊全嵌套,从片普通嵌套

(4)优先级循环方式(2种)

改变优先级的方式

-

优先级自动循环方式:

设置成该模式后,自动规定 I R 0 {IR}_0 IR0优先级最高, I R 7 {IR}_7 IR7优先级最低。

当某一中断请求 I R i {IR}_i IRi中断服务结束后,其优先级自动降级为最低,紧跟其后的 I R i + 1 {IR}_{i+1} IRi+1优先级变为最高,其余类推:由高到低为: I R i {IR}_{i} IRi, I R i + 2 {IR}_{i+2} IRi+2 … I R 7 {IR}_{7} IR7… I R 0 {IR}_{0} IR0,. I R 1 {IR}_{1} IR1… I R i {IR}_{i} IRi

例: I R 4 {IR}_{4} IR4 中断服务完后: I R 5 {IR}_{5} IR5, I R 6 {IR}_{6} IR6, I R 7 {IR}_{7} IR7, I R 0 {IR}_{0} IR0, I R 1 {IR}_{1} IR1, I R 2 {IR}_{2} IR2, I R 3 {IR}_{3} IR3, I R 4 {IR}_{4} IR4 -

优先级特殊循环方式:

与优先级自动循环方式区别在于:优先级特殊循环方式设置完后,由编程来指定最低优先级(最高优先级也确定了,例指定 I R 4 {IR}_{4} IR4为最低,则 I R 5 {IR}_{5} IR5为最高)

(5)中断结束方式(2种)

其实就是对 ISR对应位的 复“0” 处理。

-

中断自动结束方式(AEOI)

该结束方式的设置是在 8259A 初始化时实现。

CPU 进入中断响应周期,并在发出第二个 I N T A ‾ \overline {INTA} INTA脉冲后自动将 ISR对应位清“0”。

只有一片8259A 且多个中断不会嵌套的情况下才会使用该结束方。否则优先级混乱出错。 -

中断非自动结束方式(EOI)(2种)

- 1)普通 EOI 结束方式

主要用在全嵌套工作方式下,因为该模式下ISR可以确定哪一级中断是最后响应和处理的,只要 CPU 向8259A 传送 EOI 结束命令字,就会自动将ISR中级别最高的“1”复“0”(一定对应即将结束的中断)

!!!注意:EOI 结束命令字应放在返回指令 IRET 前(紧靠着),否则出错。 - 2)特殊 EOI 结束方式

主要用在非全嵌套工作方式(级联)下,因为该模式下ISR不能确定哪一级中断是最后响应和处理的。

特殊EOI结束命令字中将当前要清除的中断级别传给了8259A,然后ISR在对位清“0”。

在任何情况下都能使用。

两种EOI结束命令都是在8259A的操作命令中实现的。

- 1)普通 EOI 结束方式

(6)读 8259A 的状态:

IRR 和 ISR 用 O C W 3 OCW_3 OCW3来读

IMR 用 端口 A 0 A_0 A0为0的地址来读( O C W 1 OCW_1 OCW1?)

1.3.4 8259A 的编程

初始化编程 (初始化命令字: I C W 1 ICW_1 ICW1~ I C W 4 ICW_4 ICW4)

初始化设置 中断有效触发方式,是否级联及嵌套方式,中断结束方式,缓冲器

(1)芯片控制初始化命令字 I C W 1 ICW_1 ICW1 格式:

| D 7 D_7 D7 | D 6 D_6 D6 | D 5 D_5 D5 | D 4 D_4 D4 | D 3 D_3 D3 | D 2 D_2 D2 | D 1 D_1 D1 | D 0 D_0 D0 | … | A 0 A_0 A0 |

|---|---|---|---|---|---|---|---|---|---|

| / | / | / | 1 | LTIM | ADI | SNGL | I C 4 IC_4 IC4 | … | 0 |

I C W 1 ICW_1 ICW1 初始命令字写入条件: A 0 A_0 A0=0,命令字特征位 D 4 D_4 D4=1。

I C 4 IC_4 IC4:初始化过程中是否写入 I C W 4 ICW_4 ICW4 。

LTIM:指出中断信号的有效触发方式:

- LTIM=0:上升沿触发

- LTIM=1:高电平触发

SNGL:指出是否为多片级联。1为单片,0为多片。意味着要写 I C W 3 ICW_3 ICW3

其余只在8080/8085微机中有效。

(2)中断类型初始化命令字 I C W 2 ICW_2 ICW2 格式:

| D 7 D_7 D7 | D 6 D_6 D6 | D 5 D_5 D5 | D 4 D_4 D4 | D 3 D_3 D3 | D 2 D_2 D2 | D 1 D_1 D1 | D 0 D_0 D0 | … | A 0 A_0 A0 |

|---|---|---|---|---|---|---|---|---|---|

| T 7 T_7 T7 | T 6 T_6 T6 | T 5 T_5 T5 | T 4 T_4 T4 | T 3 T_3 T3 | I D 2 ID_2 ID2 | I D 1 ID_1 ID1 | I D 0 ID_0 ID0 | … | 1 |

I C W 2 ICW_2 ICW2 初始命令字写入条件: A 0 A_0 A0=1,且必须紧跟着 I C W 1 ICW_1 ICW1写入。

I D 2 ID_2 ID2~ I D 0 ID_0 ID0:系统自动填入 I R i {IR}_{i} IRi的编码

T 7 T_7 T7~ T 3 T_3 T3: I R i {IR}_{i} IRi的中断类型号高5位。

I C W 2 ICW_2 ICW2写入的可以理解成是 I R 0 {IR}_{0} IR0的中断级别, I R i {IR}_{i} IRi一次递增。

(3)主/从片 初始化命令字 I C W 3 ICW_3 ICW3 格式:

主片:

| D 7 D_7 D7 | D 6 D_6 D6 | D 5 D_5 D5 | D 4 D_4 D4 | D 3 D_3 D3 | D 2 D_2 D2 | D 1 D_1 D1 | D 0 D_0 D0 | … | A 0 A_0 A0 |

|---|---|---|---|---|---|---|---|---|---|

| S 7 S_7 S7 | S 6 S_6 S6 | S 5 S_5 S5 | S 4 S_4 S4 | S 3 S_3 S3 | S 2 S_2 S2 | S 1 S_1 S1 | S 0 S_0 S0 | … | 1 |

从片:

| D 7 D_7 D7 | D 6 D_6 D6 | D 5 D_5 D5 | D 4 D_4 D4 | D 3 D_3 D3 | D 2 D_2 D2 | D 1 D_1 D1 | D 0 D_0 D0 | … | A 0 A_0 A0 |

|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | I D 2 ID_2 ID2 | I D 1 ID_1 ID1 | I D 0 ID_0 ID0 | … | 1 |

I C W 3 ICW_3 ICW3 初始命令字写入条件: A 0 A_0 A0=1,且仅当 多片8259A级联时,主片从片都必须写入 I C W 3 ICW_3 ICW3。

主片: S 7 S_7 S7~ S 0 S_0 S0 分别表示 I R 7 IR_7 IR7~ I R 0 IR_0 IR0上是否有从片,为1表示有

从片: I D 2 ID_2 ID2~ I D 0 ID_0 ID0 对应 I R i IR_i IRi的编码 i 。

(4)方式控制初始化命令字 I C W 4 ICW_4 ICW4 格式:

| D 7 D_7 D7 | D 6 D_6 D6 | D 5 D_5 D5 | D 4 D_4 D4 | D 3 D_3 D3 | D 2 D_2 D2 | D 1 D_1 D1 | D 0 D_0 D0 | … | A 0 A_0 A0 |

|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | SFNM | BUF | M/S | AEOI | uPM | … | 1 |

I C W 4 ICW_4 ICW4 初始命令字写入条件:仅当 I C W 4 ICW_4 ICW4 中 D 0 D_0 D0 ( I C 4 IC_4 IC4 )为1时才需要写入 I C W 4 ICW_4 ICW4,且 A 0 A_0 A0为1。

uPM( D 0 D_0 D0):设置微处理器类型,8259A连接到80x86 时,该位必须为“1”。

AEOI( D 1 D_1 D1):设置中断结束方式,AEOI=1,表示该中断自动结束;AEOI=0表示非自动结束,具体哪种非自动结束由中断方式命令字 O C W 2 OCW_2 OCW2控制。

BUF ( D 3 D_3 D3)+ M/S( D 2 D_2 D2) :设置缓冲器。BUF=0表示非缓冲方式,说明本片8259A 和系统数据总线之间没有缓冲器;当 D 3 D_3 D3 D 2 D_2 D2=10时,本片为缓冲方式且是从片;当 D 3 D_3 D3 D 2 D_2 D2=11时,本片为缓冲方式且是主片。

SFNM( D 4 D_4 D4):设置嵌套方式,SFNM=1时,表示8259A处于多片中断控制系统中,采用特殊全嵌套方式;SFNM=0时,采用全嵌套方式。

其余位不用,一般为0。

工作方式编程 (操作命令字: O C W 1 OCW_1 OCW1~ O C W 3 OCW_3 OCW3)

(1)屏蔽操作命令字 O C W 1 OCW_1 OCW1( A 0 A_0 A0=1)

| D 7 D_7 D7 | D 6 D_6 D6 | D 5 D_5 D5 | D 4 D_4 D4 | D 3 D_3 D3 | D 2 D_2 D2 | D 1 D_1 D1 | D 0 D_0 D0 | … | A 0 A_0 A0 |

|---|---|---|---|---|---|---|---|---|---|

| M 7 M_7 M7 | M 6 M_6 M6 | M 5 M_5 M5 | M 4 M_4 M4 | M 3 M_3 M3 | M 2 M_2 M2 | M 1 M_1 M1 | M 0 M_0 M0 | … | 1 |

设置条件: A 0 A_0 A0=1

M i M_i Mi 为 1 ,表示对应的中断屏蔽 I R i IR_i IRi被屏蔽;为0则开放。

屏蔽是指不会向CPU发出 INT信号。

读IMR:RD活跃且 A 0 A_0 A0=1

(2)中断方式命令字 O C W 2 OCW_2 OCW2( A 0 A_0 A0=0 且 D 4 D_4 D4 D 3 D_3 D3=00)

| D 7 D_7 D7 | D 6 D_6 D6 | D 5 D_5 D5 | D 4 D_4 D4 | D 3 D_3 D3 | D 2 D_2 D2 | D 1 D_1 D1 | D 0 D_0 D0 | … | A 0 A_0 A0 |

|---|---|---|---|---|---|---|---|---|---|

| R | SL | EOI | 0 | 0 | L 2 L_2 L2 | L 1 L_1 L1 | L 0 L_0 L0 | … | 1 |

设置条件: A 0 A_0 A0=0 且 D 4 D_4 D4 D 3 D_3 D3=00

R( D 7 D_7 D7):循环方式设置,R=1,则表示采用优先级循环方式;若R=0,则为非循环方式。

EOI( D 5 D_5 D5):EOI=1, 表示 O C W 2 OCW_2 OCW2的作用之一是作为结束中断命令EOI,应在IRET之前,若 EOI=0,则不作为中断命令。

SL( D 6 D_6 D6):低三位是否有效。若SL=1,则末尾低三位有效。否则无效。(若是特殊的中断结束命令,即特殊非自动结束方式,该位指出要结束的中断,要清除的ISR)

特殊优先循环的设置最低优先级命令用 D 7 D_7 D7 D 6 D_6 D6 D 5 D_5 D5 =110的 O C W 2 OCW_2 OCW2。

(3)状态操作命令字 O C W 3 OCW_3 OCW3( A 0 A_0 A0=0 且 D 4 D_4 D4 D 3 D_3 D3=01)

| D 7 D_7 D7 | D 6 D_6 D6 | D 5 D_5 D5 | D 4 D_4 D4 | D 3 D_3 D3 | D 2 D_2 D2 | D 1 D_1 D1 | D 0 D_0 D0 | … | A 0 A_0 A0 |

|---|---|---|---|---|---|---|---|---|---|

| / | ESMM | SMM | 0 | 1 | P | RR | RIS | … | 1 |

设置条件: A 0 A_0 A0=0 且 D 4 D_4 D4 D 3 D_3 D3=01

P( D 2 D_2 D2):设置查询方式。P=1,表面 8259A 采用中断查询方式,可用CPU随时查询IRR。

ESMM,SMM( D 6 D_6 D6 D 5 D_5 D5):设置或撤销特殊屏蔽方式。 D 6 D_6 D6 D 5 D_5 D5=11,进入特殊屏蔽方式, D 6 D_6 D6 D 5 D_5 D5=10,返回正常屏蔽方式

RR,RIS( D 1 D_1 D1 D 0 D_0 D0):读8259A内部寄存器的状态:RR=1表示要读了,RIS=0表示读IRR;RIS=1表示要读ISR。把 O C W 3 OCW_3 OCW3送给8259A,然后用输入指令 IN 读出就行。

端口分配及读/写操作功能 表:

| C S ‾ \overline {CS} CS | W R ‾ \overline {WR} WR | R D ‾ \overline {RD} RD | A 0 A_0 A0 | 功能 |

|---|---|---|---|---|

| 0 | 0 | 1 | 0 | 写 I C W 1 ICW_1 ICW1 |

| 0 | 0 | 1 | 1 | 写 I C W 2 ICW_2 ICW2或 I C W 3 ICW_3 ICW3或 I C W 4 ICW_4 ICW4 |

| 0 | 0 | 1 | 1 | 写 O C W 1 OCW_1 OCW1 |

| 0 | 0 | 1 | 0 | 写 O C W 2 OCW_2 OCW2或 O C W 3 OCW_3 OCW3 |

| 0 | 0 | 1 | 0 | 读 IRR 或 ISR(由 O C W 3 OCW_3 OCW3决定) |

| 0 | 1 | 0 | 1 | 读 IMR |

| 0 | 1 | 0 | 1 | 读 状态? |

注意!8259 要用了OCW1开中断!

常会用到 ICW4 01H

常用编程

!!! 74138:A B C端口 C是高位!

初始化 8259A

MOV AL,13H ;ICW1:13H 边沿触发 单片 写ICW4

OUT 地址0,AL

MOV AL,前五位地址+000 ;ICW2

OUT 地址1,AL

;ICW3 用于多片 基本不用

MOV AL,01H ;ICW4 ;非自动结束,8086模式

MOV AL, NOT 开中断位 ;开中断

OUT 地址1,AL

!!! 非自动结束方式一定要在中断服务最后发出OCW2,发出中断结束命令!

中断服务程序

现场保护

PUSH...

MOV AL,20H

OUT 地址0,AL

do sth...

POP ...

IRET

放中断服务地址

;设中断服务标号为 INTPROC

MOV AX,0

MOV DS,AX

MOV BX,中断类型号*4

MOV AX,OFFSET INTPROC

MOV [BX],AX

MOV AX,SEG INTPROC

MOV [BX+2],AX