DDR与PCIe:高性能SoC的双引擎

SoC芯片无处不在,小到家电控制的MCU,大到手机芯片,我们都会接触到。如今大部分芯片设计公司都在开发SoC芯片,一颗SoC芯片可以集成越来越多的功能,俨然它已成为IC设计业界的焦点。

高性能、高速、高带宽的互联和存储的性能需求日渐占据主流。掌握PCle协议和DDR协议可以有效地提升SoC的设计验证、FPGA的设计、亦或是系统级的开发效率。

今天移知小编就带大家了解一下高性能SoC的“双引擎”——DDR与PCIe。

一、何为SoC

1、 SoC概念与传统的FPGA/MCU单片机的优势

SoC是一种集成电路设计,将计算机系统的各个功能组件集成在一块芯片上。传统的FPGA和MCU单片机也是集成电路,但SoC在功能上更加复杂、完整。与传统的FPGA/MCU相比,SoC的优势在于它将CPU、GPU、NPU、IO接口、存储器控制器等功能模块集成在一颗芯片上,形成一个高度集成、高性能的计算平台。

SoC芯片让电子设备变得更加智能,使人们的生活变得更加便捷。

2、SoC包含哪些功能模块

SoC集成了多个功能模块,常见的包括:

● 中央处理器(CPU):执行计算任务和控制任务的核心处理单元。

● 图形处理器(GPU):专门用于图形和图像处理,加速图形渲染、计算和加速深度学习等任务。

● 神经网络处理单元(NPU):专门用于加速人工智能和深度学习任务。

● 存储器控制器:管理内存和外部存储器的读写操作。

● 输入/输出接口(IO):用于与外部设备通信,如USB、Ethernet、HDMI等接口。

● 电源管理单元(PMU):管理芯片的电源供应和功耗控制。

● 安全单元:提供芯片级别的安全功能,保护数据和系统免受攻击。

二、SoC高性能体现在哪里?

高性能SoC在多个方面体现出卓越的表现:

● 计算能力:SoC集成了强大的CPU和GPU,能够处理复杂的计算任务和图形渲染,满足高性能应用的要求。

● AI加速:通过集成专用的NPU,SoC能够在处理人工智能和深度学习任务时加速运算,提升效率。

● 数据处理速度:SoC内部的高速总线和存储器控制器使得数据访问速度更快,减少数据处理瓶颈。

● 低功耗:虽然拥有强大性能,但高性能SoC也注重功耗的优化,以延长电池寿命和降低能源消耗。

三、SoC高性能是如何实现的?

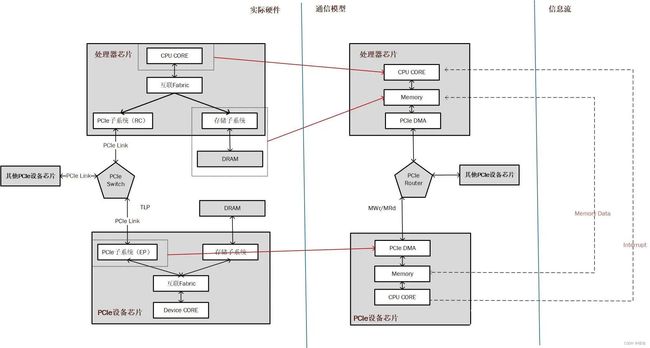

1、更快的数据处理来源于高速接口PCIe

PCIe(Peripheral Component Interconnect Express)芯片是高性能SoC中的重要组成部分。它是一种高速传输接口,连接计算机内部的各种硬件组件,如CPU、GPU、存储器、网络接口等。PCIe具有高速传输和可靠性的特点,使得数据在各个组件之间的传输更加快速和稳定。这使得高性能计算、数据中心和企业级应用等领域得到极大的受益,加快了数据处理速度,提升了整体系统性能。

在数字IC工程师的职业生涯中,了解PCle还可以为他们提供更多的职业发展机会。掌握PCle技术可以使数字IC工程师在芯片设计、系统架构、嵌入式系统等领域中有更广泛的应用。掌握PCIe协议不管是对SoC的设计验证,FPGA的设计,还是系统级的开发都提升效率,掌握PCIe协议更是成为芯片设计、验证工程师、SoC的求职加分项,PCIe并没有想象中那么容易掌握。

● PCIe的协议难以掌握?

国外的参考文献的理解难易度,没有实际项目纸上谈兵的学习;空有公开协议,没有结合案例理解上手,哪怕是已经翻译的中文教材,也容易导致无从下手。

移知教育特邀资深工程师精心打磨《PCIe协议全面解析》本课程介绍了PCle总线协议的方方面面,包括系统架构、设备互联、分层结构等,让大家深刻理解PCle的高带宽、低延时的特性。

从形象到抽象,让学习PCIe不再晦涩难懂,讲解最新Spec的协议特性和演进,通过协议分析仪实际抓取的数据包,生动介绍PCIe设备上的电、枚举、及工作过程。

● PCIe设计的各种层级问题如何理解,如何解决?

PCIe 协议测试在物理层、数据链路层和传输层上都需要进行协议确认测试。链路训练和状态机(LTSSM)是协议测试里面的一个关键方面。链路训练可以确保数据包在链路伙伴之间可靠地传输。协议分析和训练器工具可以确定PCIe 器件是否能与其链接伙伴成功通信。

随着数据速率的提升,高速串行数据链路的设计变得非常复杂。通道拓扑越来越复杂多变。

PCIe 互连测试通道是 PCIe 系统中最关键的元素之一快速确认测试PCIe 设计的参数,确保它们符合 PCIe 规范定义的性能要求,这是测试过程的一个重要环节。

● 向下兼容的难,各个版本迭代的兼容问题

各个版本的迭代兼容处理,实际的公司业务场景处理。

移知教育 新课升级《PCIe IP之UVM验证实战》,一课搞定设计和验证,本课程以可流片的PCIe代码为基础,介绍了PCIe理论以及PCIe实战的内容,目标是大家能在实际的PCIe项目中可以上手干活。共22个章节,理论和实战相结合,从验证环境的搭建,到DUT data path的梳理,学完即可上手做PCIe RTL设计以及验证工作。

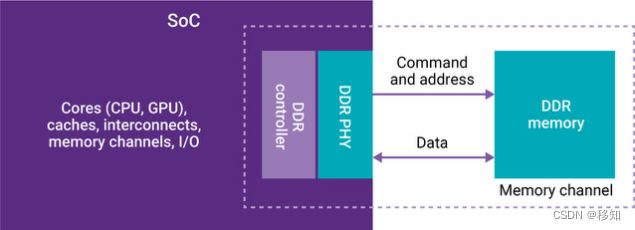

2、连接计算和存储两个体系的桥梁 -DDR

在高性能SoC中,计算和存储是两个重要的体系,它们之间的连接和协调对于整个系统性能至关重要。冯·诺依曼架构是当今SoC常用的计算架构,但在高性能SoC中,内存和互联带宽常常成为性能瓶颈。

为了解决这一问题,新一代的高带宽存储技术应运而生。其中,DDR、LPDDR、GDDR等技术作为连接计算和存储两个体系的桥梁,有效地突破了“内存墙”。

高性能 SoC 通常具有多个存储器通道。图示显示的简化 DDR 存储器可以是上述任何 DDR 类别的 DRAM 存储器。

SoC 中的存储器通道框图

大型SoC芯片不能没有DDR,就像大战役中离不开军火库一样,如果你想涉猎SoC芯片领域,了解或掌握DDR技术,对你来说是必不可少的,可以这么说,CPU+总线+DDR+一些简单外设就可以组成一个SoC系统,可见DDR的地位不言而喻。

移知教育《DDR3全面解析》带你掌握SoC的核心技术:memory子系统。

通过课程的学习,你可以在 1-2 个月内快速从零基础起 ,学会 DDR3的协议,掌握DDR控制器的设计原理,了解DDR PHY的功能以及training过程,知道如何验证DDR的控制器及其效率,并能从模块和系统的角度对DDR的效率进行分析,同时你可以站在前辈的肩膀上去分析和解决问题,并在通往DDR设计成功之路的最后也最难一站上汲取必不可少的营养。

高性能SoC作为连接计算和存储的桥梁,在计算能力、AI加速和数据处理速度等方面展现出优越的性能。通过采用高速接口PCIe和最新的高带宽存储技术,高性能SoC能够满足越来越复杂的计算需求,推动着计算领域的不断发展和创新。

掌握PCle协议和DDR协议可以有效地提升SoC的设计验证、FPGA的设计、亦或是系统级的开发效率。移知的目标是希望通过契合实际学习情况的难点进行针对性讲解,帮助各位快速入门。

大家加油,祝大家早日掌握PCle协议和DDR协议!