Cadence全家桶Capture+Allegro流程-5-编辑焊盘并制作封装

Cadence作为专业绘图工具,在高速设计领域是王者一般的存在。但是从易用性角度来说,比AD还是有些差距。

接下来我们从Padstack焊盘编辑器讲起,把Allegro的使用讲解一遍,并结合实际的一个小项目的案例进行详细讲解。

同样,我们这个教程不是针对专业LAYOUT工程师,而是针对智能硬件工程师。因此我们的教程会

- 讲解原理;

- 讲解样品制作过程;

但是并不会讲解cadence的各种细节,因为作为智能硬件工程师,往往并不需要掌握cadence的方方面面。作为专业layout工程师,可能需要掌握的更多一些。

Padstack Editor基本介绍

启动Padstack Editor

Start起步设置

启动后可以发现系统预先设定一些Padstack

还可以选择不同形状的焊盘。

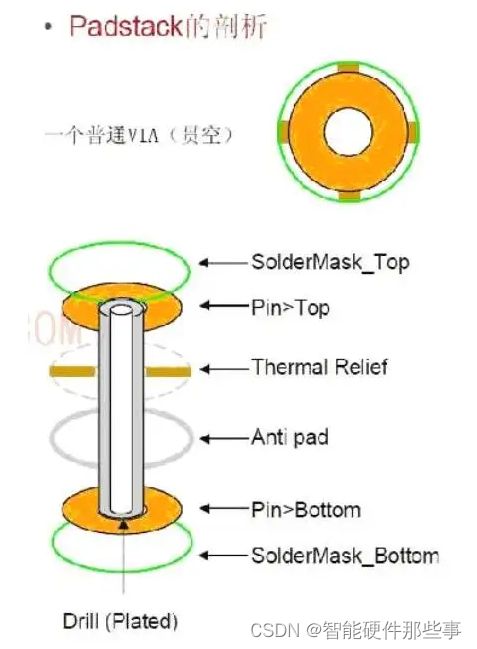

Padstack是焊盘叠加。上面是一个焊盘的剖视图。即使是一个小小的焊盘,也有一个复杂的结构。

Soldermask:其中Solder为锡膏; Mask为遮蔽罩;Solder Mask就是遮挡锡膏的罩子,也就是所谓钢网层。我们把钢网改在PCB上,然后通过印刷,将锡膏也就是Solder印刷到PCB上。

Thermal Relief: 热焊盘。也就是通常可见的十字花焊盘。如果不用十字花焊盘,焊接时,热量很容易被周围包裹的铜皮吸收,会造成焊接失败;

单位选择毫米,精度选择4位;

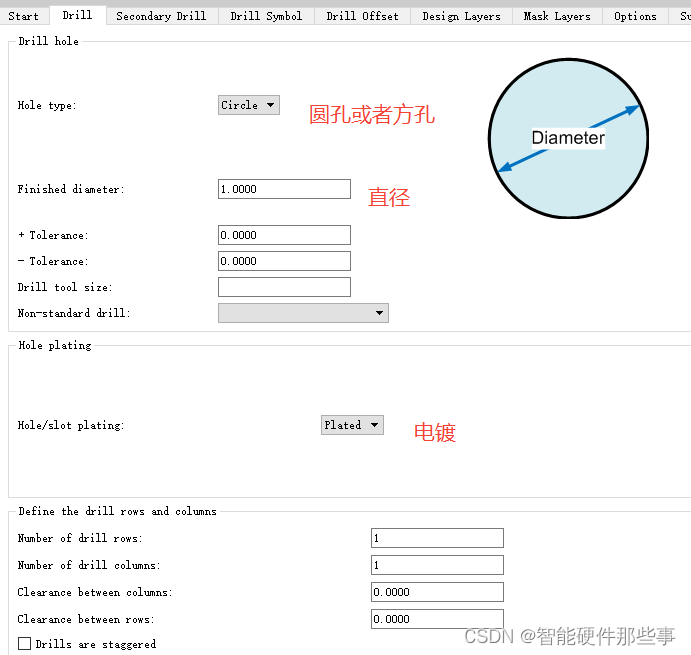

Drill钻孔设置

如果我们选择了通孔,那么还需要设置对应的钻孔。

我们需要了解的设置,就是圆孔或者方孔,直径为多少?

一般钻孔尺寸如何设置呢?主要是看元器件管脚尺寸。一般来说,大部分元器件会给出PIN脚直径以及推荐的焊盘钻孔尺寸。

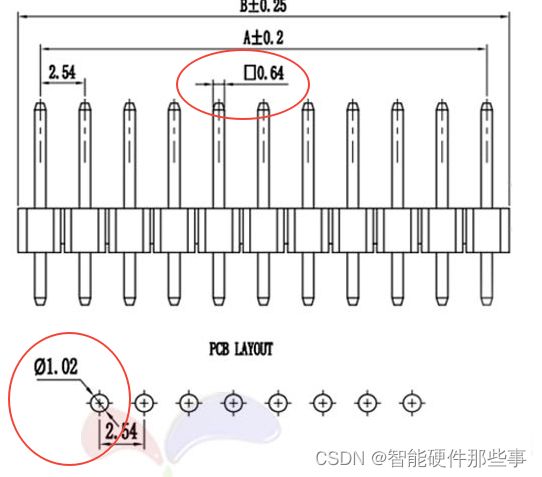

例如:最常见的2.54间距排针,管脚边长为0.64,推荐开孔为1.02。开孔比管脚大了0.5mm,方便插拔。

这里我们了解原理即可,真正项目中,我们更多的是搜索和整理相关的库文件,而不需要从每个焊盘做起。

实例-制作ESP32芯片的封装

接下来,我们通过实例,展示一下,如何制作ESP32芯片的封装。

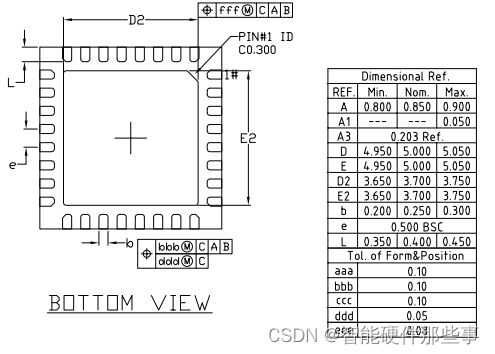

查看Datasheet

首先我们需要获取Datasheet。一般我们获取Datasheet可以从官网获取,也可以从一些常用第三方网站获取。

作为一个智能硬件工程师,比较使用的找Datasheet的方法是:

1.从淘宝搜索对应的芯片,按照销量排序(注意:淘宝商家常常会虚挂很多芯片,有人询价之后,再去调货。所以建议按照销量排序,这样找到的商家相对靠谱,至少30天内成交过)

2. 根据商家详细图片,再查找对应的手册,找到手册后,再和商家的封装进行反复核对,避免封装选错。同一种芯片往往会有很多封装,封装弄错了基本上这个板子就废掉了。

例如:我们接下来需要用ESP32-C3来做一个项目,我们就需要找到这个芯片的手册。具体做法如下:

1. 淘宝上查找ESP32-C3芯片

找到前面几家,都是有销量的。可以看到他们具体型号为ESP32-C3F4。

2. 半导小芯-芯片查询工具_芯片替代查询_数据手册查询_规格书查询_datasheet查询_IC查询

到网上查找数据手册。

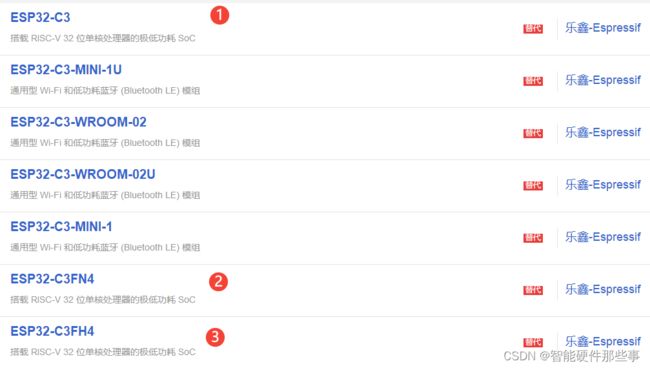

看到这里有3个SOC也就是芯片。我们直接打开C3FN4,也就是第2个。

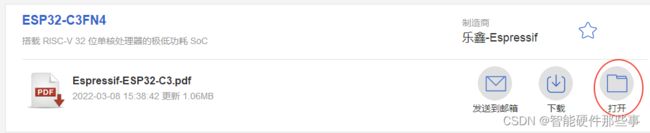

选择打开,直接开启数据手册

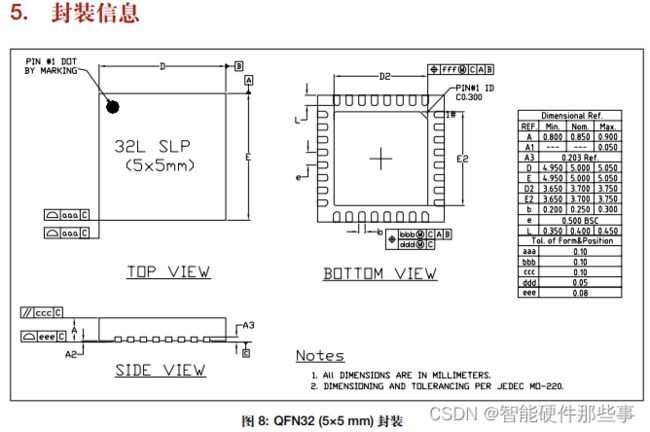

一般封装在数据手册最下方。

b管脚宽度 为0.25

L管脚长度 为0.4

e管脚间距,为0.5

由于管脚间距固定,我们在管脚宽度上,无法增加太多,否则管脚之间的绿油宽度就不够了(管脚之间绿油宽度至少保持0.2mm)

而在长度方向,我们可以适当加大,这样便于贴片时候进行对位。所以长度我们设置为0.6

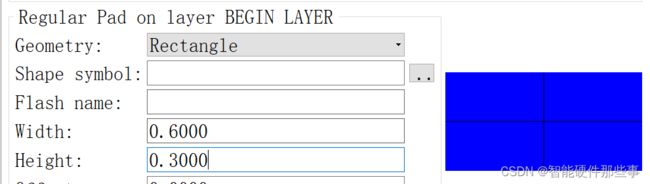

所以我们准备设置焊盘尺寸如下:

高度:0.6

宽度:0.3

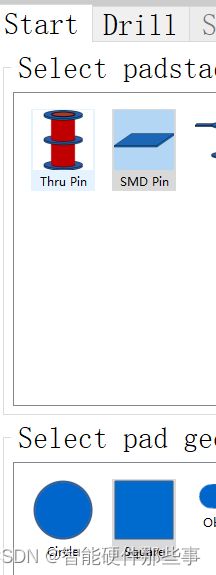

Start开始制作焊盘

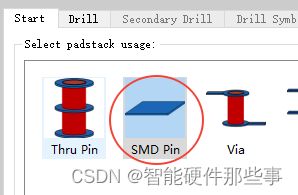

1.选择合适的类型

选择SMD Pin。

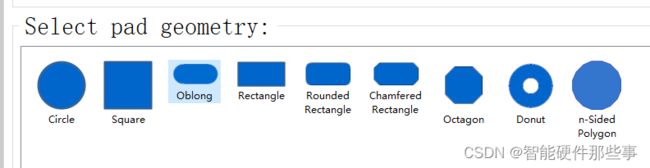

下面选择椭圆形焊盘。

2.设置Design Layer

左下角设置单位为mm,有效位数为4

设置宽度和高度为0.6和0.3

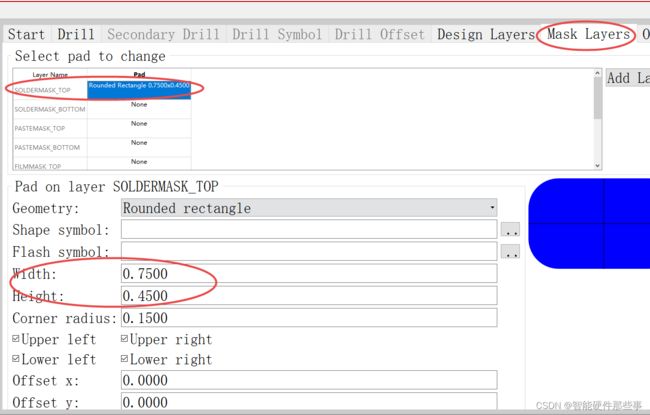

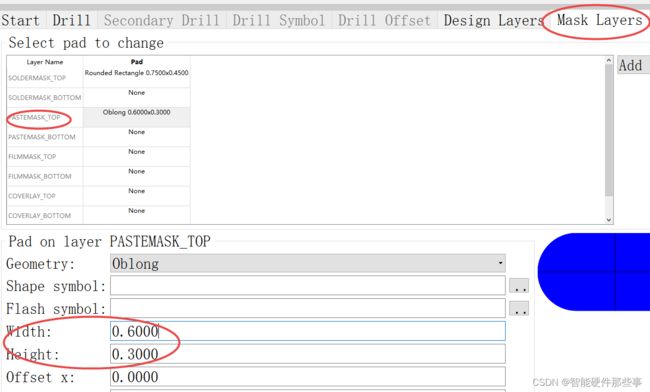

3.设置阻焊

阻焊层也就是常说的绿油层,现在也有黑色,紫色等不同颜色设置。阻焊层的目的是阻止焊锡到处乱跑。比如管脚之间就会有阻焊层,这样焊锡就不会连接在不同焊盘之间。

一般阻焊层比前面的焊盘大0.15即可。

4.设置钢网层

钢网是为了印刷锡膏时用的。为了让锡膏能够透过,将锡膏准确印刷到焊盘上。

钢网层就按照同样的管脚尺寸即可设置。

5.命名规范

sob0R6X0R3

s表示贴片,如果是通孔则用t

ob表示椭圆形;

0R6X0R3表示宽度为0.6高度为0.3

通过统一的命名规范,可以方便后续重用。

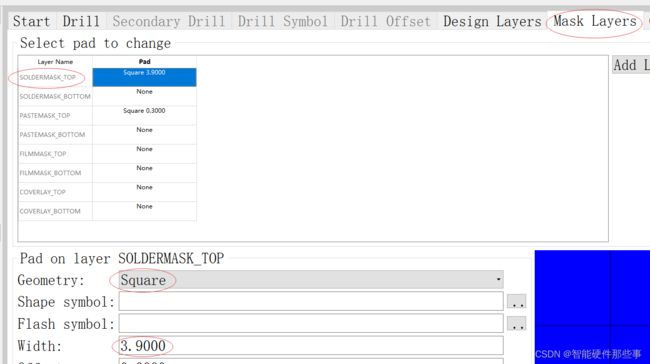

制作中间散热焊盘

中间散热焊盘D2和E2最大尺寸为3.75。我们按照这个尺寸来制作。

1. start

Start的时候,选择Rectangle长方形。

2.设置边长

这里选择正方形,边长为3.75。

3.设置Mask

在绿油层也就是Soldermask层,要比3.75加上0.15,就变成3.9

在钢网层也就是paste_mask层,保持3.75即可

4.文件保存

保存文件时,文件名为sr3r75x3r75即可。其中r表示Rectangle

新建封装

完成焊盘之后,我们就可以制作封装了。制作封装采用的时PCB Editor.

1.创建封装文件

选择File->New

然后新建Package symbol

对应的文件名是qfn32_6x6,这个文件名是按照数据手册中的封装名来命名的。

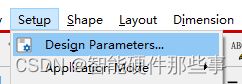

2.设置基本参数

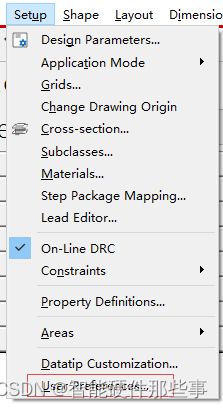

选择Setup->Design Parameter

左下角坐标设置为-100和-100,这样就可以把中间原点保持为坐标0.

3.计算一脚坐标

横坐标:eX7/2=-1.75

纵坐标,也就是跨距:(D+0.1+0.1-0.4)/2=-2.4

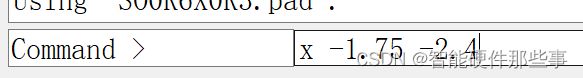

所以1脚坐标为 -1.75 -2.4

1脚坐标计算完成后,剩余管脚都是对称的,因此计算非常简单。

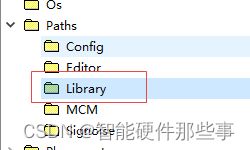

4. 指定焊盘路径

我们焊盘路径统一放在下面路径中。

E:\KEZIOT\LIB\CadenceLib\Library\Padstack

前面制作好的焊盘,也可以放在其中。

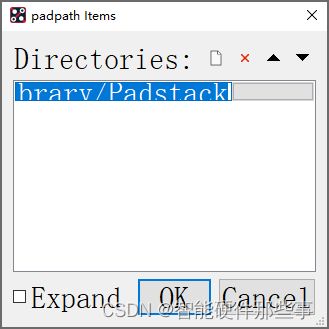

然后在setup->user preference中,进行指定

选择Library

选中对应的padstack

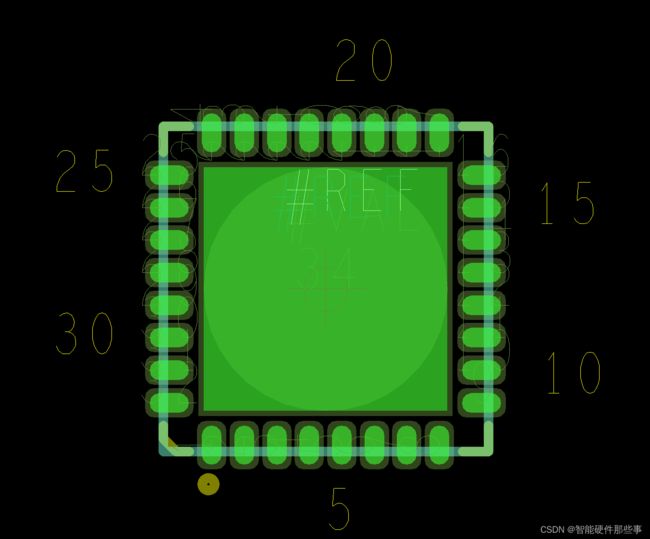

5. 放置焊盘

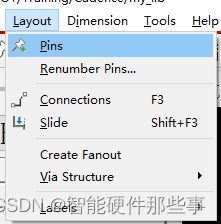

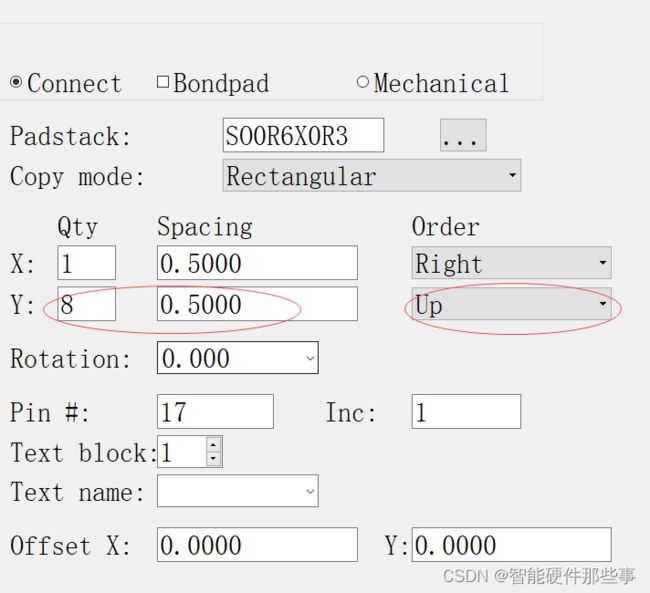

选择Layout->Pins来放置焊盘。

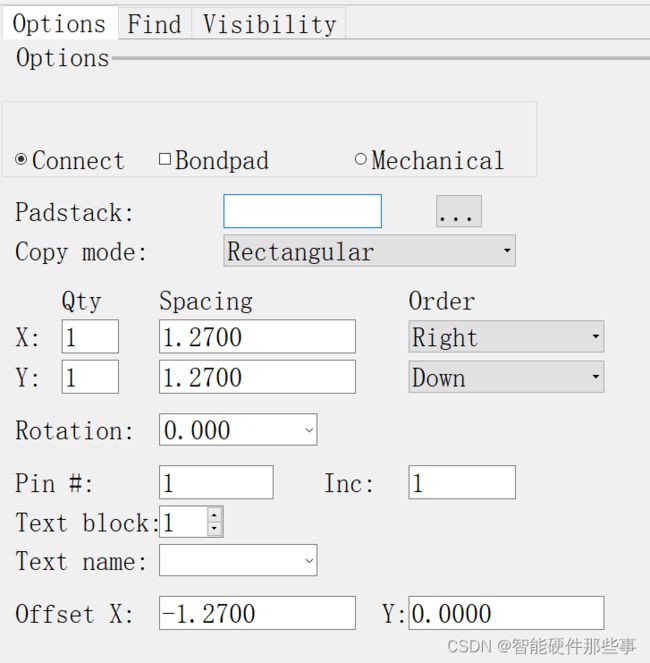

在Option中,首先选择对应的焊盘。

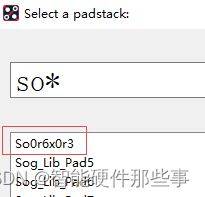

输入so*可以过滤出之前用过的焊盘。

左下角Command界面输入坐标 ,然后输入回车,即可完成摆放。

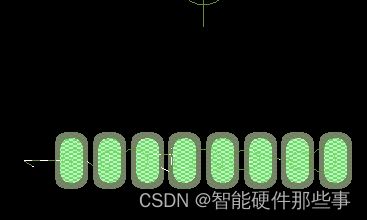

接下来放置右侧的8个,其坐标为:x 1.75 y -2.4

完成放置后,对应如图所示。

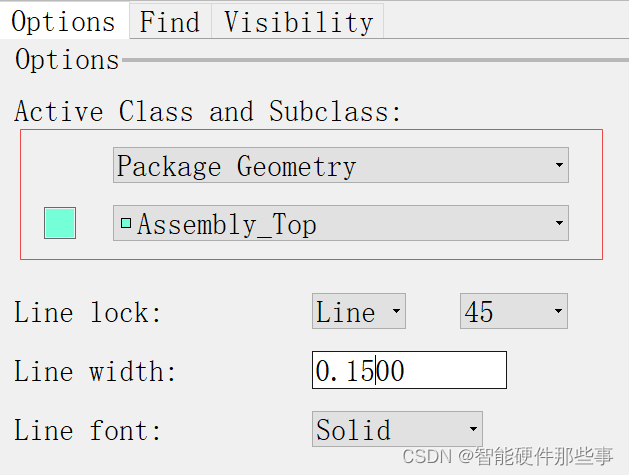

6. 放置装配层

接下来放置装配层。

放在Assembly Top这一层,通过命令进行放置:

x -2.5 -2.5 放在-2.5 -2.5的位置

ix 5 偏移5

iy 5 向上偏移5

ix -5 向左偏移-5

iy -5 向下偏移-5,回到起点。

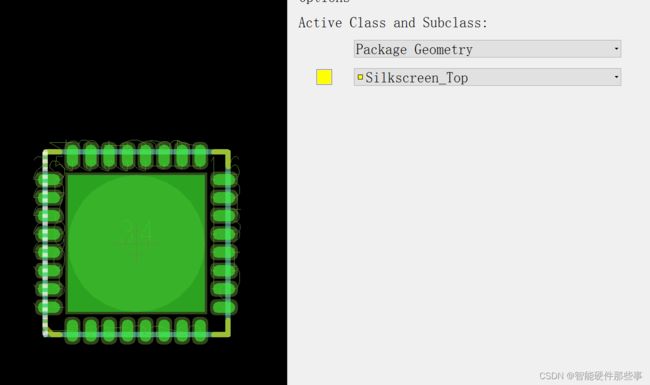

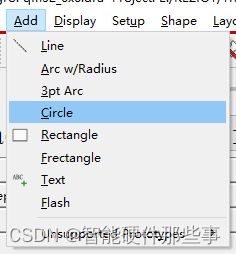

7. 放置丝印层

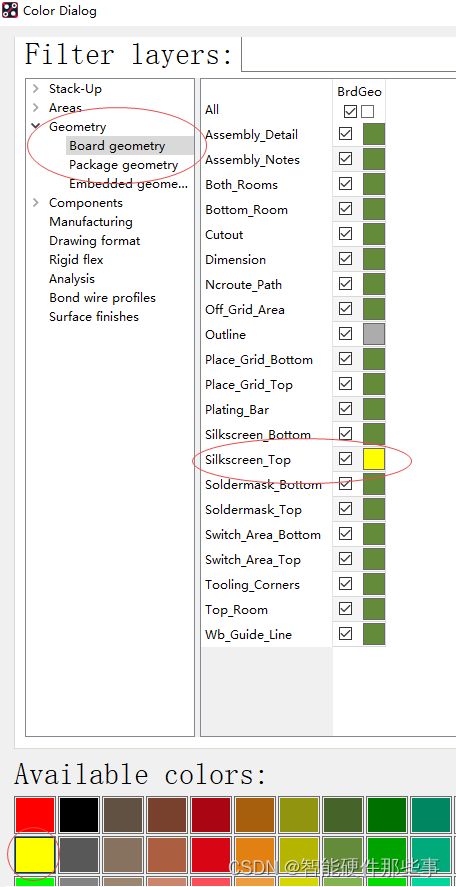

先把丝印层设置为黄色。

选择这个Color192图标

选择Board Geometry->Package Geometry;

选择下方的黄色后,把Silkscreen_Top修改为黄色。

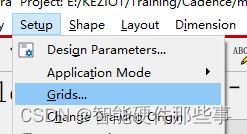

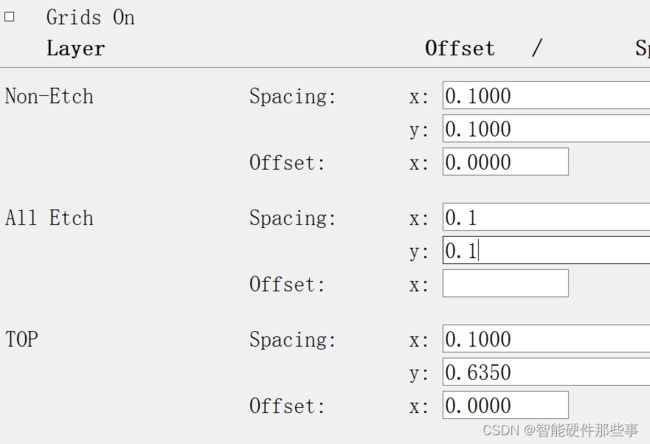

然后再选择Setup->Grids,修改格点。

把格点间距都修改为0.1,方便后续画线。在这里修改格点的原因是:前面都是通过坐标输入,而这里需要手动画线。

设置好格点之后,手动画线即可。

在4个角落划线,画在丝印层。

8. 放置REF和VALUE

REF对应位号,例如:U1, R1这样;

VALUE对应芯片型号,例如ESP32-C3这样;

按照规范,我们需要放置REF和VALUE;

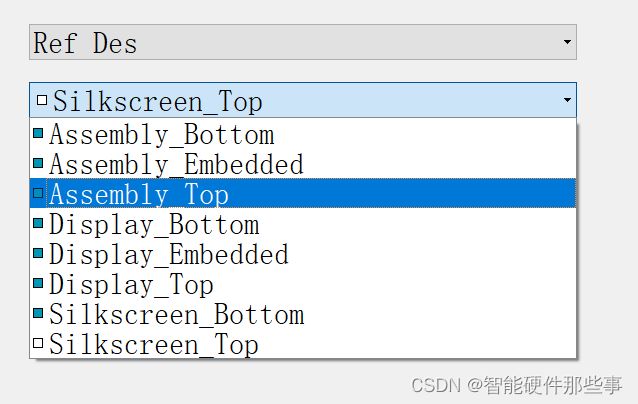

#REF放在Ref Des的Assembly Top和Silkscreen_Top层;

#VAL放在Component Value的Silkscreen_Top层;

9. 放置1脚标志和脚序号

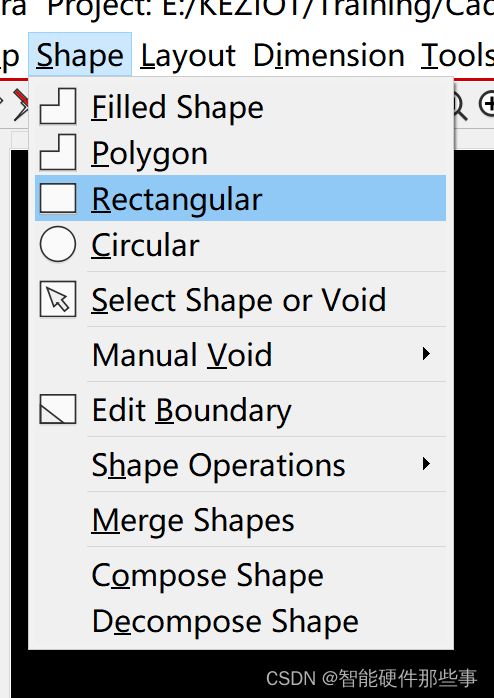

10. 放置占地面积

选择Shape->Rectangle

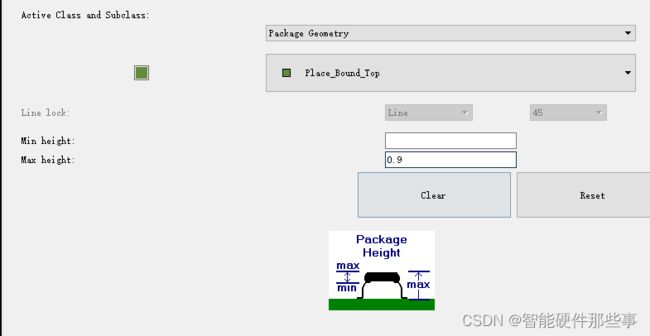

然后选择Package Geometry->Place_Bound_Top。

放置时,比元器件大2个格点即可。

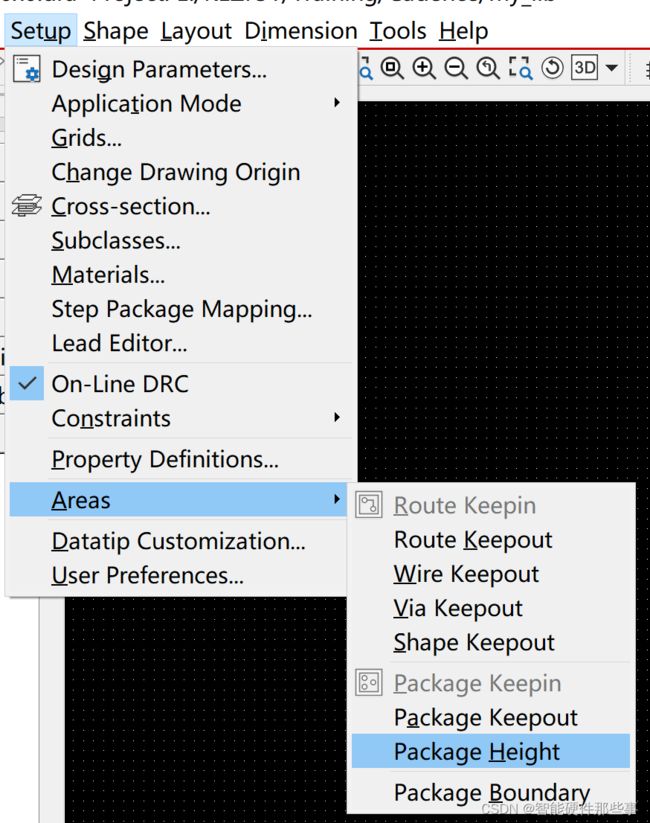

11. 设置高度

选择Setup->Areas->Package Height

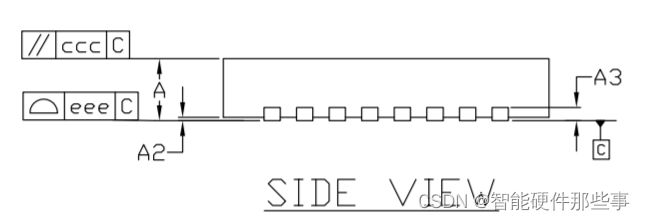

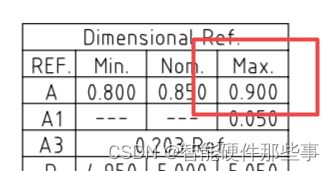

可以看到尺寸A为芯片高度。

尺寸A最大为0.9

选中刚才的Place_Bound,输入高度0.9

12. 保存库

选中Save As即可保存库文件。可以看到,会自动生成dra和psm两个文件。其中dra为封装设计文件。psm为PCB Editor的真正设计文件。

从上面的过程可以看出,用Cadence设计封装还是比较麻烦的,需要首先设计焊盘,然后再用焊盘来设计封装。

幸运的是,我们已经积累了大量的库文件,因此大部分情况,我们是不需要设计封装的。

但是,我们还是需要掌握设计封装的技能,因为早早晚晚需要自己设计新的封装。