Verilog 1995 VS Verilog 2001

2001年3月IEEE正式批准了Verilog‐2001标准(IEEE1364‐2001),与Verilog‐1995相比主要有以下提高。

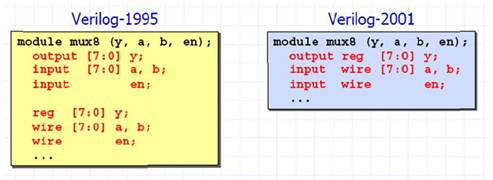

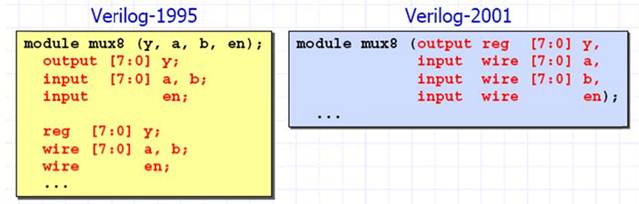

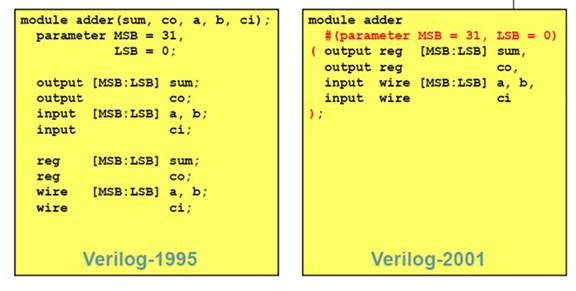

1、模块声明的扩展

(1) Verilog‐2001允许将端口声明和数据类型声明放在同一条语句中,例子如下:

(2)Verilog‐2001中增加了ANSIC风格的输入输出端口声明,可以用于module,task和function。例子如下:

(3)对于含有parameter的module,例子如下:

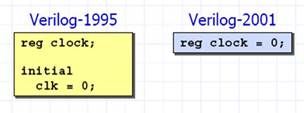

2、带有初始化的寄存器类型变量声明

Verilog‐2001中允许在声明变量的同时对其进行初始化赋值,他是在initial语句中的0时刻开始执行。例子如下:

3、敏感表的改进

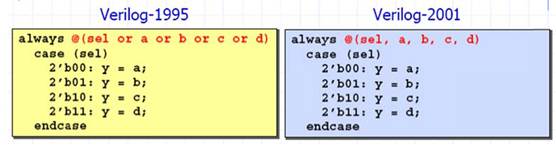

(1)逗号分开敏感列表

在敏感表中的变量可以用逗号“,”分开,当然,当然or也是可以的。例子如下:

always@(posedge clk,negedge rst)也是可以的。

(2)组合逻辑的电平敏感@* //@(*) is also ok

“*”代表了逻辑块中每个被赋值的变量,例子如下:

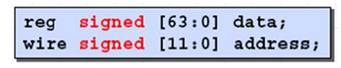

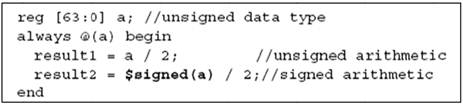

4、有符号算数运算的扩展

(1)net型和reg型可以声明为带符号的变量

(2)函数的返回值可以是有符号数

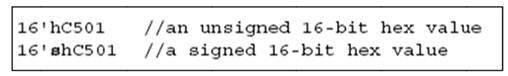

(3)Literal integer numbers可以定义为有符号的

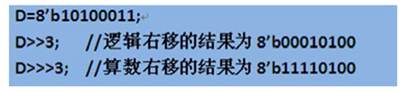

(4)增加算数右移左移(>>>,<<<)

操作符“>>>”和“<<<”。对于有符号数,执行算术移位操作时,将符号位填补移出的位。例子如下:

(5)增加系统函数$signed,$unsigned

用于在无符号和有符号数之间的转换

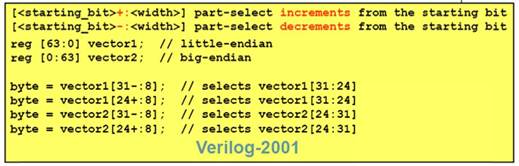

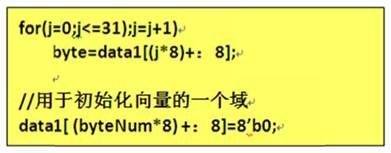

5、可变向量域的选择

[

[

其中,起始位可以是变量,但位宽必须是整数。因此可以用可变域选择,用循环语句选取一个很长的向量所有位。

6、多维数组的建立

Verilog‐1995中只允许对reg,integer和time建立一维的数组,常用于RAM,ROM的建模。Verilog‐2001中可以对net和variable建立多维数组。

7、多维数组的赋值

Verilog‐1995不允许直接访问矩阵字的某一位或某几位,必须将整个矩阵字复制到另一个暂存变量中,从暂存中访问。

Verilog‐2001可以直接访问矩阵的某一维或某几位。

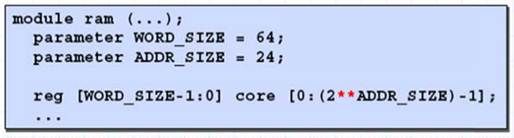

8、乘方运算符

增加乘方运算(power operate),运算符是**,如果其中有一个操作数是real类型的,返回值将是real类型。两个操作数都是integer类型,返回才是integer类型。

9、自动(可重入)任务和自动(递归)函数

(1)可重入任务

任务本质上是静态的,同时并发执行的多个任务共享存储区。当某个任务在模块中的多个地方被同时调用,则这两个任务对同一块地址空间进行操作,结果可能是错误的。Verilog‐2001中增加了关键字automatic,内存空间是动态分配的,使任务成为可重入的。

(2)递归函数

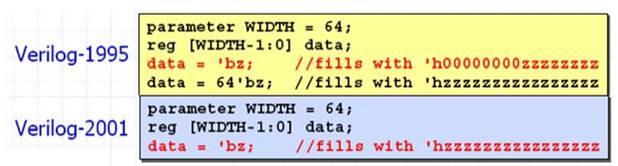

10、自动宽度扩展

Verilog‐1995中对于不指定位数的位宽超过32为的总线赋高阻时,只会对低32位赋值为高阻,高位将为0。

Verilog‐2001将高阻或不定态赋值给未指定位宽的信号时,可以自动扩展到整个位宽范围。

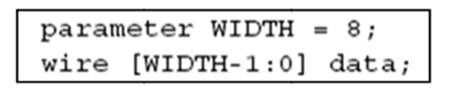

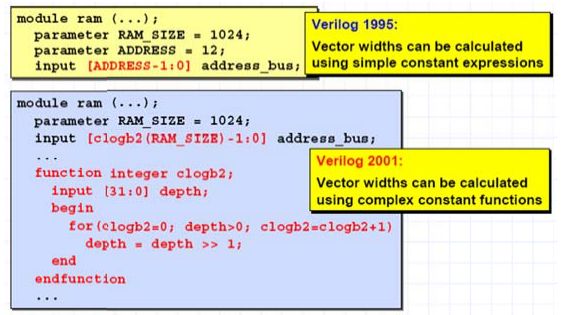

11、常数函数

Verilog语法规定必须使用数值或常数表达式来定义向量的位宽和阵列的规模。

Verilog‐1995中要求上述表达式必须为算数操作。

Verilog‐2001中可以使用函数,成为常数函数。他的数值在编译或详细描述中被确定。

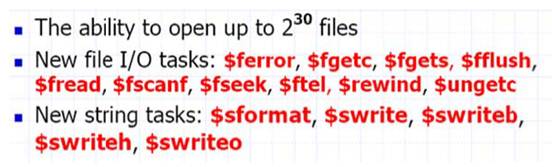

12、增加了文件输入输出操作

Verilog‐1995中在文件的输入/输出操作方面功能非常有限,文件操作经常借助于Verilog PLI(编程语言接口),通过与C语言的文件输入/输出库的访问来处理。并且规定同时打开的I/O文件数不能多于31个。

Verilog‐2001增加了新的系统任务和函数,并且规定同时打开的文件数目为230个。

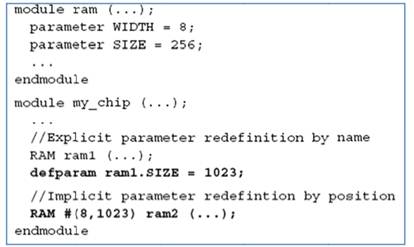

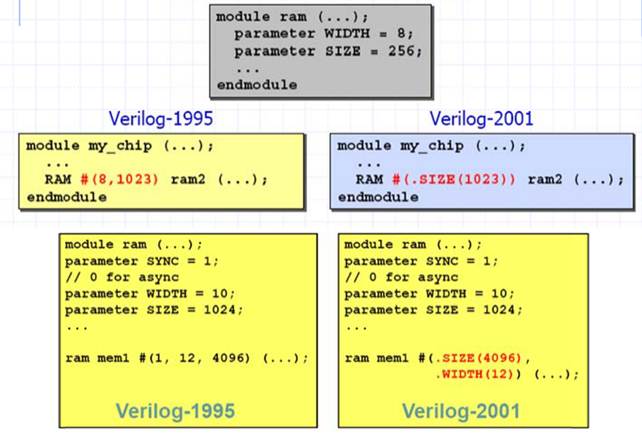

13、显式的参数重载

Verilog‐1995中参数重载有两种方法。一种是defparam语句显式的重新定义。第二种是在模块实体调用时使用#符号隐式的重新定义参数。

Verilog‐2001中增加了一种新的方法,成为显式参数重载。

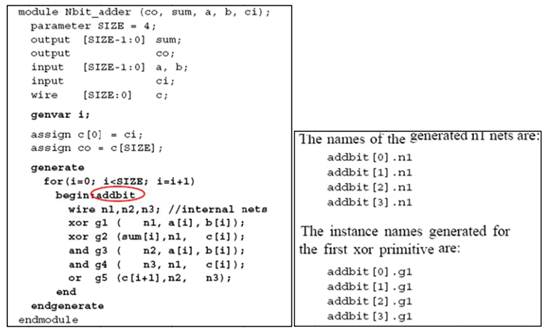

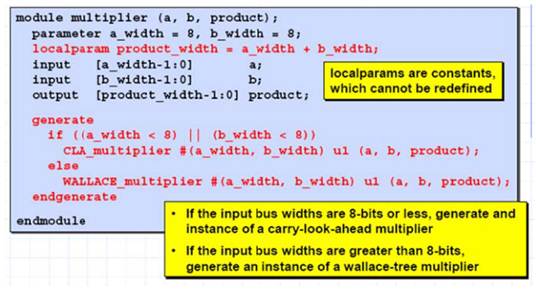

14、generate语句

Verilog‐2001新增了语句“generate”,通过generate循环,可以产生一个对象(比如一个元件或一个模块等)的多个例化,为可变尺度的设计提供了方便。

generate语句一般在循环和条件语句中使用。Verilog‐2001增加了四个关键字generate、endgenerate、genvar和localparam,其中genvar是一个新的数据类型,用在generate循环中的标尺变量必须定义为genvar型数据。

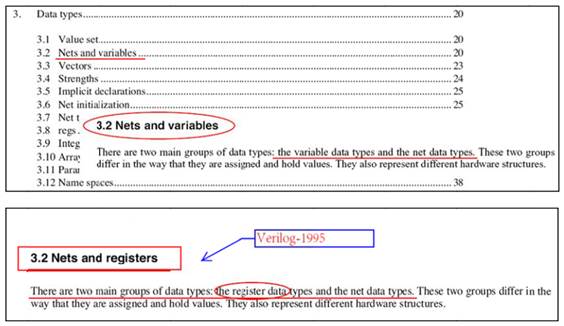

15、register变为variable

自1998年的Verilog一来,register一直用来描述一种变量的类型,这常常给初学者带来困扰,误认为register和硬件中的寄存器一致。在Verilog‐2001参考手册中将register变为variable。

16、对条件编译的改进

Verilog‐1995中支持`ifdef、`else、`endif、`undef进行条件编译,Verilog‐2001中增加了`ifndef和`elseif

17、文件和行编译显示

Verilog需要不断的跟踪源代码的行号和文件名,可编程语言接口(PLII)可以取得并利用行号和源文件的信息,以标记运行是的错误。但如果Verilog代码经过其他工具的处理,源码的行号和文件名可能丢失。故在Verilog‐2001中增加了`line,用来标定源码的行号和文件名。

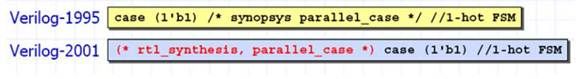

18、属性

随着仿真器之外的其他工具把Verilog作为设计输入,这些工具需要Verilog语言能够加入跟指定工具有关的信息和命令。

Verilog没有定义标准的属性,属性的名字和数值由工具厂商或其他标准来定义。目前尚无指定的标准。

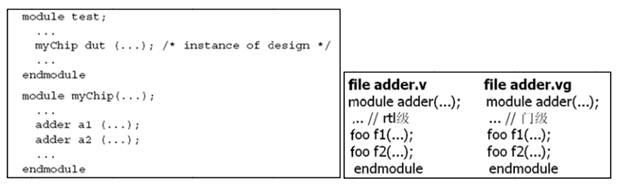

19、设计管理——Verilog配置

Verilog‐1995标准将设计管理工作交给软件来承担,但各仿真工具的设计管理方法各不相同,不利于设计的共享。为了更好地在设计人员之间共享Verilog设计,并且提高某个特定仿真的可重用性,Verilog‐‐2001标准增加了对设计内容的配置这部分内容。

增加关键字config、endconfig、design、instance、cell、use和liblist。

配置块位于模块定义之外,可以指定每一个Verilog模块的版本及其源代码的位置。Verilog程序设计从顶层模块开始执行,找到在顶层模块中实例化的模块,进而确定其源代码的位置,照此顺序,直到确定整个设计的源程序。

configcfg4 ///给配置块命名

designrtlLib.top ///指定从哪里找到顶层模块

defaultliblistrtlLibgateLib; ///设置查找实例模块的默认顺序

instancetest.dut.a2liblistggateLib; //明确指定模块实例使用哪一个库

endconfig

20、系统任务和系统函数的扩展

Verilog‐2001增加了17个文件输入/输出任务:$fgetc、$ungetc、$fflush、$ferror、$fgets、$rewind、$swrite、$swriteb、$swriteo、$swriteh、$sformat、$sdf_annotate、$ffscanf、$sscanf、$fread、$ftell、$fseek。

增加了两个转换函数:$signed和$unsigned。

增加了命令行输入任务:$test$plusargs和$value$plusargs。

21、VCD文件的扩展

VCD文件用于存储选定的变量数值变化的信息,信息的记录由VCD系统任务来完成。

在Verilog‐1995标准中只有一种类型的VCD文件,即四状态类型,这种类型的VCD文件只记录变量在0、1、x和z状态之间的变化,而且不记录信号强度信息。而在Verilog‐2001标准中增加了一种扩展类型的VCD文件,能够记录变量在所有状态之间的转换,同时记录信号强度信息。

扩展型VCD系统任务$dumpports、$dumpportsoff、$dumpportson、$dumpportsall、$dumpportslimit、$dumpportsflush、$vcdclose

22、其他

(1)提高了ASIC/FPGA应用的正确性

①检测脉冲的传播错误

②负脉冲检测

③新的时序约束检查

④负时序约束

⑤提高了对SDF(标准延时文件)的支持

(2)编程语言接口PLI方面有所改进