国产FPGA(紫光同创)—— 数据采集及千兆以太网传输(一)

科研需要,使用国产FPGA(紫光PLG50H)实现数据采集及千兆以太网传输。总体流程如图所示

第一部分先对数据采集部分进行说明。

一、模数转换(ADC芯片-LTC2324)

本项目使用的是LTC2324系列的ADC芯片进行数据的模数转换。以LTC2324-16为例,它是低噪声、高速四路16位逐次逼近寄存器(SAR)ADC,差分输入,支持CMOS或LVDS的高速SPI兼容串行接口,每个通道最大可达2Msps的吞吐量,具体信息查看数据手册。

LTC2324-16数据手册下载

我们使用的是SDR模式,CMOS(每个SDO读取1个通道的)的方式进行数据采集,时序图以及时序特性如下图所示。

CNV:转换输入。该引脚位高时,定义采集阶段。当该引脚被驱动为低电平时,转换阶段启动,输出数据被计时。

SCK:串行数据时钟输入。该时钟的下降沿将转换结果MSB首先移位到SDR模式(DDR=低)中的SDO引脚上。在DDR模式(SDR/DDR=高)下,该时钟的每个边缘首先将转换结果MSB移位到SDO引脚上。

CLKOUT:串行数据时钟输出。CLKOUT是SCK信号的延迟版本(a skew-matched clock),在SDR模式下,SDO在CLKOUT的下降沿转换。

官方建议:在SDR模式下,使用CLKOUT的上升沿将SDO数据锁存到FPGA寄存器中。在DDR模式下,SDO在SCK的每个输入边缘上转换,使用CLKOUT上升沿和下降沿将SDO数据锁存到FPGA寄存器中。

因此在写LTC2324的驱动程序时,使用CLKOUT的下降沿来采集数据。

这一部分其实是理论部分,在这简单的介绍了下,想要详细了解的还是去看数据手册,这样的话更会更容易的上手使用LTC2324.

二、驱动程序

重点部分,在了解LTC2324后,就要使用紫光FPGA进行驱动ADC芯片进行采集的工作,这里是根据紫光FPGA对官方的例程进行修改,使用的时候可以根据实际项目需求进行更改(强烈建议看看官方的例程)。

顶层模块LTC2324_coms.v。包含了生成需要的时钟模块pll.v,fenp.v;生成LTC2324驱动信号的模块pulse_generator.v;以及进行数据接收处理的模块deserializer.v。

// 本驱动实现100MHz时钟下 0.5Msps采样率

// 可以通过调整sync信号来修改采样率

// 使用CLKOUT下降沿采集信号

`timescale 1ps / 1ps

module LTC2324_cmos

(

CLKIN,

SCK,

CLKOUT,

CNV_EN,

SDO1,SDO2,SDO3,SDO4,//输入4通道数据

data1,data2,data3,data4

);

input CLKIN; //Clock in from user @ 50 MHz

input CLKOUT; //CLKOUT signal from the ADC

input SDO1,SDO2,SDO3,SDO4; //Data out Chs 1,2,3,4 from ADC

//Latch signal from FPGA to DC890 on falling edge

output CNV_EN; //Convert start on falling edge

output SCK; //SCK from FPGA to ADC @ 100 MHz SDR

output data1,data2,data3,data4;

wire CNV_EN;

wire sck_gate,sync,rx_start,data_latch;

wire CLKOUT;

wire rx_clk_100,clk_100;

wire SDO1,SDO2,SDO3,SDO4;

pll pll_inst(

.clkin1(CLKIN),

.clkout0(rx_clk_100),

.clkout1(clk_100),

.clkout2(clk_10)

);

fenp fenp_inst(

.clk_10m(clk_10),

.rst_n(rst_n),

.sync(sync)

);

//generate the 'SCK' signal因为紫光FPGA没有双速率IP核所以要自己生成SCK信号在pulse_generator中

/* altddioout sckddr

(

.datain_h(sck_gate),

.datain_l(1'b0),

.outclock(clk),

.dataout(SCK)

); */

//generate the timing pulses 'sck_gate', 'CNV_EN'

pulse_generator pulses

(

.clk(clk_100),

.sync(sync),

.rst_n(rst_n),

.cnv_en(CNV_EN),

.sck_gate(sck_gate),

.rx_start(rx_start),

.data_latch(data_latch),

.sck(SCK)

);

parameter channel1 = 4'b0001;

parameter channel2 = 4'b0010;

parameter channel3 = 4'b0011;

parameter channel4 = 4'b0100;

wire[31:0] data1,data2,data3,data4;//最终采集的32位数据(16位数据加8位时间戳,两个4位通道号)

// Receive serial data from ADC ch 1 and converts it to parallel format

deserializer rx1

(

.rx_start(rx_start),

.reset(rst_n),

.clk_sdr(CLKOUT),

.sdo(SDO1),

.parallel_data(data1),

.data_latch(data_latch),

.channel(channel1)

);

// Receive serial data from ADC ch 2 and converts it to parallel format

deserializer rx2

(

.rx_start(rx_start),

.reset(rst_n),

.clk_sdr(CLKOUT),

.sdo(SDO2),

.parallel_data(data2),

.data_latch(data_latch),

.channel(channel2)

);

// Receive serial data from ADC ch 3 and converts it to parallel format

deserializer rx3

(

.rx_start(rx_start),

.reset(rst_n),

.clk_sdr(CLKOUT),

.sdo(SDO3),

.parallel_data(data3),

.data_latch(data_latch),

.channel(channel3)

);

// Receive serial data from ADC ch 4 and converts it to parallel format

deserializer rx4

(

.rx_start(rx_start),

.reset(rst_n),

.clk_sdr(CLKOUT),

.sdo(SDO4),

.parallel_data(data4),

.data_latch(data_latch),

.channel(channel4)

);

endmodule

因为篇幅的原因其余模块文件可在github下载查看(https://github.com/wang-bocheng/LTC2324)。

不懂得地方可以私信或者评论留言,都会尽力解答,互相学习。

三、modelsim仿真

总体工程编译通过后,进行modelsim联合仿真。主要是看CNV信号以及SCK信号是否满足时序要求。

可以看出CNV信号和SCK信号是满足数据手册的要求(忘记截CNV信号了)。

四、采集实测

所有工作都完成后,就要进行实测环节,测试ADC芯片的采集效果了。

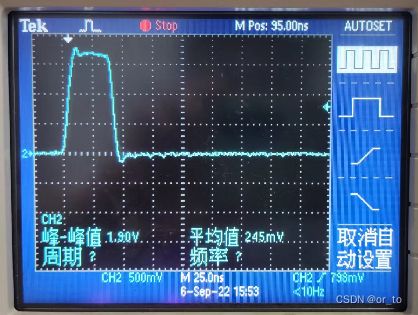

1. 示波器波形

整个项目的测试阶段,为了验证驱动程序的正确性,还用示波器对CNV信号和SCK信号进行观察(其实也使用了Debugger进行波形抓取)。

可以看出,波形是没有问题,说明我们的驱动程序可以对LTC2324进行驱动。

2. 实测部分

先是没有使用麦克风传感器,直接在放大电路上添加正弦波信号进行测试(为什么会有噪声,除了电路的原因,还是因为我们实验室的波形发生器太老了(穷,老师不给换))。

将采集的信号使用千兆以太网发送到PC机(下一部分记录下千兆以太网的实现),将数据保存下来使用matlab进行观察,效果还是不错的。

接下来就是使用麦克风传感器(咪头)采集语音信号进行测试,结果如下图所示,并进行了简单的滤波处理,还是使用千兆以太网上传至PC机使用matlab进行分析。

(这是一首周杰伦的歌,大概采集了4秒钟)。

至此,基于国产FPGA(紫光)的LTC2324数据采集完成,第二部分将记录下千兆以太网是怎么实现的数据传输。