I2C通信协议详解

据非官方统计,90%电子行业的公众号都介绍过3种串行通讯协议:UART、SPI和I2C。这3种串行协议也是电子开发行业最常用的协议。前面介绍了串口通讯协议及其FPGA实现,SPI协议。本篇文章介绍I2C通讯协议及其FPGA实测波形。

1.I2C是什么

在消费电子,工业电子等领域,会使用各种类型的芯片,如微控制器,电源管理,显示驱动,传感器,存储器,转换器等,他们有着不同的功能,有时需要快速的进行数据的交互,为了使用最简单的方式使这些芯片互联互通,于是I2C诞生了,I2C(Inter-Integrated Circuit)是一种通用的总线协议。它是由Philips(飞利浦)公司,现NXP(恩智浦)半导体开发的一种简单的双向两线制总线协议标准。

对于硬件设计人员来说,只需要2个管脚,极少的连接线和面积,就可以实现芯片间的通讯,对于软件开发者来说,可以使用同一个I2C驱动库,来实现实现不同器件的驱动,大大减少了软件的开发时间。极低的工作电流,降低了系统的功耗,完善的应答机制大大增强通讯的可靠性。

2.5种速率

I2C协议可以工作在以下5种速率模式下,不同的器件可能支持不同的速率。

标准模式(Standard):100kbps

快速模式(Fast):400kbps

快速模式+(Fast-Plus):1Mbps

高速模式(High-speed):3.4Mbps

超快模式(Ultra-Fast):5Mbps(单向传输)

【bps:bit/s,即SCL的频率】

其中超快模式是单向数据传输,通常用于LED、LCD等不需要应答的器件,和正常的I2C操作时序类似,但是只进行写数据,不需要考虑ACK应答信号。

在I2C协议的官方文档NXP_UM10204_I2C-bus specification and user manual_Rev.6,超快模式和其他模式在3.2和3.1章节分别进行介绍。

3.4种信号

I2C协议最基础的几种信号:起始、停止、应答和非应答信号。

起始信号

I2C协议规定,SCL处于高电平时,SDA由高到低变化,这种信号是起始信号。

停止信号

I2C协议规定,SCL处于高电平,SDA由低到高变化,这种信号是停止信号。

数据有效性

I2C协议对数据的采样发生在SCL高电平期间,除了起始和停止信号,在数据传输期间,SCL为高电平时,SDA必须保持稳定,不允许改变,在SCL低电平时才可以进行变化。

应答信号****

I2C最大的一个特点就是有完善的应答机制,从机接收到主机的数据时,会回复一个应答信号来通知主机表示“我收到了”。

应答信号出现在1个字节传输完成之后,即第9个SCL时钟周期内,此时主机需要释放SDA总线,把总线控制权交给从机,由于上拉电阻的作用,此时总线为高电平,如果从机正确的收到了主机发来的数据,会把SDA拉低,表示应答响应。

使用MCU、FPGA等控制器实现时,需要在第9个SCL时钟周期把SDA设置为高阻输入状态,如果读取到SDA为低电平,则表示数据被成功接收到,可以进行下一步操作。

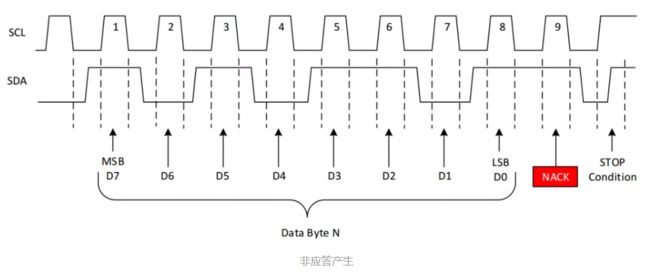

非应答信号

当第9个SCL时钟周期时,SDA保持高电平,表示非应答信号。

非应答信号可能是主机产生也可能是从机产生,产生非应答信号的情况主要有以下几种:

I2C总线上没有主机所指定地址的从机设备

从机正在执行一些操作,处于忙状态,还没有准备好与主机通讯

主机发送的一些控制命令,从机不支持

主机接收从机数据时,主机产生非应答信号,通知从机数据传输结束,不要再发数据了

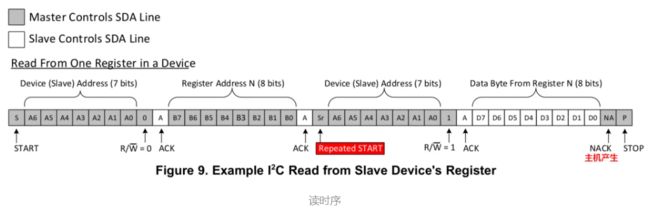

4.读写时序

向指定寄存器地址写入指定数据操作时序:

从指定寄存器地址读取数据操作时序:

注意,读数据时有两次起始信号。

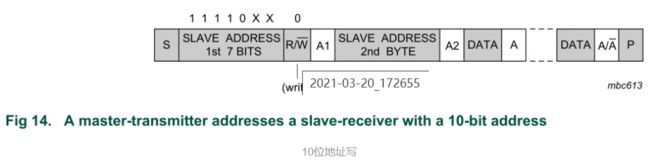

5.7位和10位地址

大多数I2C器件支持7位地址模式,有一些器件还支持10位地址,而且两种类型的器件可以连接在同一个I2C总线上,目前10位地址的器件还没有被广泛使用。

主机发送,从机接收。使用10位地址进行写时序:

主机接收,从机发送。使用10位地址进行读时序:

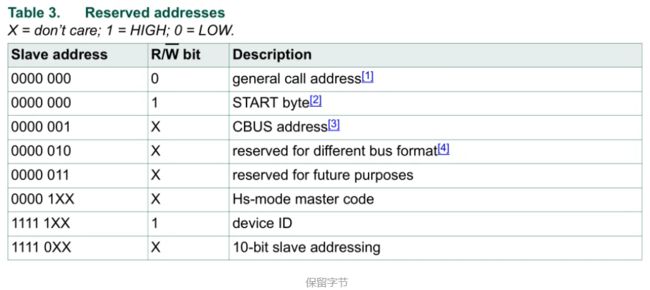

6.I2C保留字节

I2C读写时起始位之后的第一个字节,除了厂商指定的设备地址外,还有一些保留字节,主要有两组0000 xxx和1111 xxx,保留字节的含义:

上述的10位地址模式,就是使用到了最后一种保留字节。

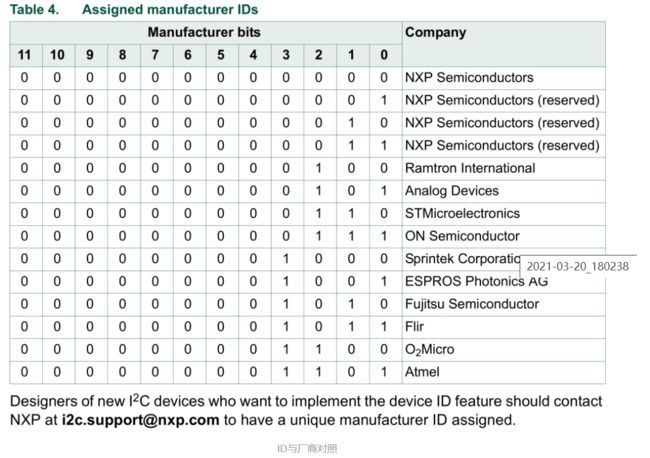

第一种广播模式,可以通过写入第二个字节06h来复位I2C总线上所有的从机器件。具体操作时序可以查看文档NXP_UM10204_I2C-bus specification and user manual_Rev.6:3.1.12 Reserved addresses章节有详细介绍。其中device ID控制字(1111 1xx1),可以读取I2C器件内部的24位器件ID,通过对照NXP I2C协议器件列表可以查询到器件所属的厂商和型号。

设备ID与器件厂商对应表

7.FPGA实测I2C波形

FPGA实现UART、SPI、I2C等串行时序,最常用的实现方式就是状态机大法,将各个步骤分解为各个状态,然后根据不同的状态去控制输出或读取输入,细节方面需要考虑数据的对齐、建立和保持时间、一些异常情况时状态的跳转,不能进入死循环,或卡死在某一个状态。

I2C控制状态机状态定义:

//general

S0_IDLE = 0,

S1_START1 = 1,

S2_CTRL_BYTE1 = 2,

S3_ACK1 = 3,

S4_ADDR = 4,

S5_ACK2 = 5,

//write: 0-1-2-3-4-5->6-7-13-14

S6W_DATA = 6,

S7W_ACK3 = 7,

//read: 0-1-2-3-4-5->8-9-10-11-12-13-14

S8R_START2 = 8,

S9R_CTRL_BYTE2 = 9,

S10R_ACK3 = 10,

S11R_DATA = 11,

S12R_NACK = 12,

//general

S13_STOP = 13,

S14_DONE = 14,

S15_ERR = 15;

注意SDA双向端口的方向控制。

output eeprom_scl,

inout eeprom_sda,

localparam DIR_IN = 1'b0;

localparam DIR_OUT = !DIR_IN;

reg dir;

reg i2c_sda;

reg i2c_scl;

assign eeprom_scl = i2c_scl;

assign eeprom_sda = (dir == DIR_OUT) ? i2c_sda : 1'bz;

wire sda_in = eeprom_sda;

SDA应该在第9个SCL时钟周期设置为输入状态:

下图的波形是使用Xilinx FPGA对AT24C1024的驱动,使用片上逻辑分析仪ChipScope抓取的实际波形,AT24C1024B存储空间为1024K Bit = 131072 Byte,存储单元地址位宽为17位。

AT24C1024B写时序:

AT24C1024B读时序:

SPI和I2C的对比

I2C是半双工,SPI是全双工。

I2C支持多主多从模式,而SPI只能有一个主机。

从GPIO占用上来看,I2C占用更少的GPIO,更节省资源。

I2C有应答响应机制,数据可靠性更高,SPI没有应答机制。

I2C速率不会太高,最高速率3.4Mbps,SPI可以达到很高的速率。

I2C通过器件地址来选择从机,从机数量的增加不会导致GPIO的增加,而SPI通过CS选择从机,每增加一个从机就要多占用一个GPIO。

SPI协议在SCLK边沿进行数据采样,I2C在SCL高电平期间进行数据采样。

两者大多都应用于板内器件短距离通讯。

官方标准文档下载

目前网上比较详细的介绍I2C文档主要有以下3个:

-

I2C官方标准文档_UM10204

I2C的官方文档是原飞利浦(Philips)半导体事业部,现恩智浦(NXP)半导体发布的UM10204文档,全文共64页,是目前最权威最详细的I2C协议介绍文章,最新版本Rev. 6发布于20140404,UM10204_4 April 2014: I2C-bus specification and user manual_Rev.6 -

TI:理解I2C文档_SLVA704

TI在2015年发布了一篇SLVA704文档, 全文共8页,精简的概括了I2C协议的电气特性,操作时序,读写时序等,比较适合I2C入门学习。 -

ZLG:I2C总线规范中文版

这篇文档发布于2000年左右,是对飞利浦官方文档UM10204_v2.1的翻译。

I2C协议文档只是最基础的文档,具体寄存器读写操作等操作,还是要结合所使用芯片的数据手册来使用。

原文地址:https://mp.weixin.qq.com/s/bwb-I5rHd321oZwyuaVSDA