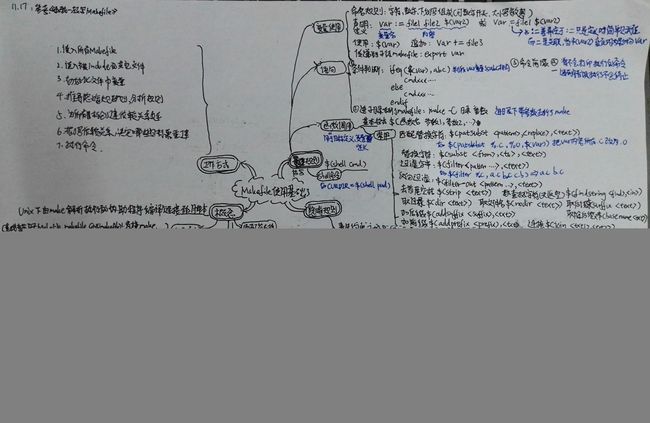

简图记录-Makefile基础

简图记录学习,参考:《跟我一起写Makefile》

一、概念

Makefile: Unix下由make解析执行的协助程序编译链接的脚本,makefile支持通配符如 * ? [] 等;

Makefile执行方式:1、直接make(查找当前目录Makefile、makefile、GNUmakefile);2、make -f xxx (指定xxx位make执行的解析脚本文件)

Makefile脚本内容:

1)、显示规则:显示指定 目标、依赖、生成命令;

#makefile基本规如下:(通过cmd命令将依赖request生成目标target)

target:request1 request2 request3

cmd1

cmd2

cmd32)、隐晦规则:makefile中方便规则制定的简化写法,自动推导规则;

3)、变量定义

4)、文件引入 include xxx 引入xxx文件;

5)、注释:(#开头行)

Makefile执行原理:找到当前目录下的makefile、找到makefile种第一个目标文件target作为最终目标,若target不存在或者依赖的文件比target修改时间更新,则执行cmd命令重新生成target(target所依赖文件按同样的方式判定是否需要更新,这是一个递归过程),处理完成所有目标及其依赖更新结束。

Makefile伪指令:makefile可指定伪目标去执行相关命令但无需生成真正目标文件,在makefile中以.PHONY关键字声明的伪目标(类似通过make xxx来执行伪目标xxx定义规则下的cmd),方便使用tab补全;常见伪指令有clean清除,all编译全部,install编译完成后可执行文件拷贝到对应目录;

二、Makefile书写规则

1、变量

1)命名:通过字符、数字、下划线组成,大小写敏感,额可以数字开头;

2)声明定义: Var2:=a b c $(Var1);//把var2定义位 a b c var1的值; 追加Var1+=d // 把var1的值再追加一个d;(:=为简单定义方式,还有一种是 Var2 = a $(Var1),使用=会使Var2和Var1关联起来,后续Var1的变化也会引起Var2变化)

3)使用:$(Var1),如echo $(Var1);

4)传递到子Makefile export Var1

2、语句使用

条件判断语句(当var变量等于abc执行cmd1否则执行cmd2)

ifeq($(Var),abc)

cmd1

else

cmd2

endif进目录执行makefile:make -C 目录 参数(执行make时带)

语句前缀:@cmd执行cmd时不打印cmd这条指令到终端;-cmd执行cmd遇到错误跳过直接执行(默认停止makefile动作)

3、函数调用

基本格式$(函数名 参数1,参数2,...)

常用:匹配替换字符patsubst; 过滤字符filter; 反向过滤filter-out; 去首位空格strip; 连接join; 加后缀addsuffix; 取目录dir ;取文件名nodir

4、shell命令调用

$(shell cmd) 如var:=$(shell pwd)

三、Makefile隐晦规则

1、隐含变量

针对C文件 $(CC)编译器默认cc、$(CFLAGS)默认C编译器编程参数

2、隐含编译规则

针对C文件 XX.o若没有指定依赖和生成规则,默认按照依赖为XX.c命令为$(CC) -c xx.c $(CFLAGS)

%.o:%.c

$(CC) -c $(CFLAGS) $< -o $@3、自动化变量

$@目标文件集合;$<第一个依赖(若依赖为%.x则为所有满足要求的文件集合);$^所有依赖的集合(空格分离 去除重复)

定义隐含规则如: