芯片设计:一颗芯片到底是如何诞生的(上)

目录

芯片设计整体流程

小故事:苹果的芯片设计路

需求分析

架构设计

逻辑设计

前端设计与验证

逻辑综合

DFT(可测试性设计)

物理实现

小结

芯片设计整体流程

一颗芯片,是如何诞生的呢?其实一颗芯片项目就是一个标准的产品项目,项目的起点是市场需求分析,接着是设计和制造,如果产品成功完成了商业落地,那么就可以开启下一代产品的迭代升级新周期了。

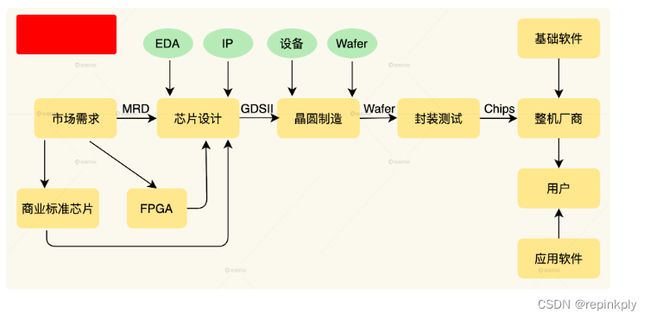

为了方便大家记忆理解,我做了一张完整的流程图。重点有市场需求分析、芯片设计、晶圆制造、封装测试这四个流程,最后,封装测试好的芯片成品会交给设备厂商,完成电子设备硬件的制造组装和软件安装。

你一定要记住这张图,基本上它对所有的电子设备,从指纹密码锁,到手机、PC、服务器,甚至超级计算机,都是适用的。

因为这个流程比较长,我把它拆成了两部分,这一讲重点放在芯片的设计,下一讲我们再来看芯片的制造。

如果只看芯片设计,它主要包含需求分析、架构设计、逻辑设计、物理实现和验证等几个部分。

如果说芯片项目和其他产品项目有什么不同,那就是芯片项目是人类历史上最细微也是最宏大的工程,研发投入大,项目收益高,试错成本极高。

以 iPhone 的 A11 应用处理器为例,这颗处理器包含 43 亿的晶体管,工程师们要在有限的项目时间内,实现手机应用处理器所需要完成的功能任务,还需要在 88mm² 指甲盖大小的面积下放置下 43 亿晶体管和它们自己的连线,再要经过缜密的验证工程,以保证它在2 亿台手机上都能正常工作 2-3 年。

有人说芯片是人类造物的巅峰之作,我是非常认可这种说法的。

像 A11 处理器这样一个项目,它的商业价值有多大呢?我来给你算算。苹果每年的手机销售约为 2 亿台,按照上一讲我提供给你的 iPhone X 物料表,A11 价值 27 美金,乘以 2亿台手机那就是总共价值 54 亿美金。

苹果的应用处理器是自己设计,委托台积电代工的。因此,27 美金的标价,算是成本价格了。如果购买其它同类同性能的应用处理器,可能大约要 80 美金的单价,这样算下来,就是 160 亿美金的总价值。

让我再重复一下几个关键数字,2017 年的发布的 iPhone 8,采用的应用处理器 A11,43亿晶体管,88mm² 指甲盖大小的面积,2 亿手机销量,160 亿美金的总价值。不知道你看到这组数据是什么感觉,我是被这组数据震撼到了。

接下来,我就以苹果公司为例,先讲讲苹果是怎么走上自制芯片的道路的,然后再给你逐步揭秘芯片的设计流程。

小故事:苹果的芯片设计路

2005 年,苹果在开始计划 iPhone 之前的 iPod 产品时,当时是先买 PortalPlayer 公司的,后来采用三星的现成商业芯片搭建的。

商业芯片,英语有一个专门的词叫"off the shelf",就是指从(超市)架子上拿下来就能用。现成的商业芯片的好处是方便易得,价格确定。不好的地方,就是挑一个 100% 满意的比较难。会遇到功能不完全匹配、性能有高有低、接口不够用、大厂价格贵,小厂可能供货不稳定等问题。

站在 2005 年的时间点,那时高通的手机应用处理器还没有 GPU,德州仪器还在为如日中天的诺基亚服务,而且没有单片的方案,需要另配基带芯片。总之,那个时候没有完美选择。

因此苹果打算定制一款自用的芯片。我们现在知道,苹果曾经和 Intel 谈过定制芯片的想法,但是 Intel 拒绝了。于是苹果转向邀请当时为 iPod 供应芯片的三星为自己定制芯片。

本来在买商业现成芯片,和定制芯片或者自制芯片之间,还有 FPGA 一个选择。FPGA 可以通过硬件编程语言,把芯片内的标准阵列器件重新组合,形成新的电路,完成类似定制芯片的功能,可以节省投片生产的开销和时间。

但是,代价就是单片的价格偏高,功耗偏高,因此 FPGA 在数据中心的应用较多,在手机终端领域极少。

苹果这种提供产品规格需求,由三星做设计服务和生产的这种模式,业内叫设计服务。而且委托设计服务的边界,非常灵活,苹果公司可以完全不参与设计只提产品规格要求,也可以自己完成部分设计,从一小部分到绝大部分都可以,其余再交给设计公司。

不过,这个过程其实也挺不容易,苹果在请三星设计过两代芯片之后,开始自建设计团队,最终决定自己来完成芯片设计环节。按照苹果架构师的回忆,三星实现了苹果要求的功能,但是最终的芯片并不是苹果想要的芯片。这种芯片规格书与芯片成品之间的差距,就是架构师要背的锅了。

小故事我先讲到这里,后面也就是苹果自己做设计的故事了。回到开篇说的芯片设计流程,我们来看看,要做芯片设计的话,芯片公司都会做哪些工作呢?

需求分析

其实可以想见当时一定是有多个芯片公司,发现了手机应用处理器这个真实需求。在芯片公司发现市场需求之后,通常会进行市场调查,总结出一个通用的市场需求清单出来。一般这个需求清单,会包括主要应用场景分析、软件栈、竞争分析、性能与定位、需求量与投资回报比分析、行规与标准,主要配套芯片的市场供应情况预测等多项内容。最终形成的就是一份市场需求文档。

每个公司的文档流程不一样,有的公司,在做市场需求文档之前,还要做商业需求文档,重点在于分析投入产出比。在市场需求文档之后,还要做深入的产品需求文档和细分的功能需求文档。

在需求分析之后,通常会有一个立项决策会议,由内部管理层决策是否进行此产品的开发。如果顺利通过立项决策,这个芯片项目就由市场部门,转交给研发部门。

像苹果 A11 这种项目,需求分析这一步,会集中在公司内部,为 iPhone8 服务。而如果是高通,联发科这种商业芯片公司,往往会征求主要客户的反馈,和手机厂商们对齐需求。

架构设计

我们说,一个项目是否有商业价值,主要看需求分析。而一个芯片是否做得好,80% 是由架构设计决定的。

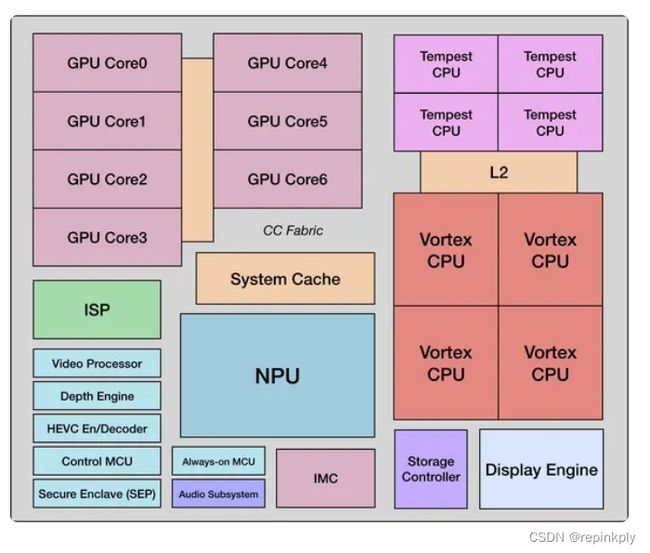

在拿到需求分析文档后,高层设计人员,往往是以架构师为主的团队,需要开会对产品需求逐条进行可行性分析,并在此基础上确定基本架构和模块分解,最终设计出一个系统架构。我可以给你看看,苹果 A12 的一张系统架构图,你可以感受一下。

在基本架构确定之后,芯片的大目标,就是对 Power 功耗、 Performance 性能、Area 面积,也就是业内常提到的 PPA 衡量标准,要有明确的规划,这一般也就确定了要选择的制造工厂和工艺制程。接着,芯片设计公司要把需要向供应商购买的 IP 和自研的 IP,把它们的交付时间和接口逐一确认。苹果的 CPU 核一直是自研的,GPU,则从 IP 供应商那里购买过很长一段时间。

如果采用先进封装技术进行小芯片(chiplet)的设计,此时封装方案和初步的布局规划也都应该确定了。在大多数情况下,一个芯片里面只封装一个集成电路硅片,但是有时候为了更高的性能,或者高密度的设计,当然还有成本因素,需要把多个硅片封装在一起,这种技术手段就叫先进封装。

到架构设计这一步,最终输出的就是一份产品规格书和高层架构设计文档。这是一个将市场需求,翻译为可实现的芯片架构过程。

架构确定了之后,通常架构团队和算法工程师团队会建模仿真,确保功能、性能、吞吐量等指标可实现。有了一个可行的芯片设计方案和芯片原型模型之后,架构团队就可以把文档和芯片模型移交给设计团队,开始逻辑设计。设计团队,会先输出微架构或者模块设计文档,然后进入编码阶段。

回顾一下开篇那张图,你可以理解,架构设计的输入是市场需求文档,输出是产品规格书。下一步,逻辑设计也叫前端设计,就需要拿着产品规格书,去输出 RTL 代码,用以生成网表(Netlist)了。

我们在开头提到,在逻辑设计完成后,还要做物理实现,物理实现就是由 RTL 代码综合成门级网表,然后生成 GDS II 文件的过程。这里的物理实现也叫后端设计,前端和后端设计这两个部分并没有统一严格的界限,凡涉及到与物理工艺有关的设计我们就叫后端设计。

我们先来看逻辑设计。

逻辑设计

前端设计与验证

前端设计(逻辑设计)一般用硬件描述语言,例如 Verilog,将架构师的设计用编码实现。大型芯片项目,设计也是分层次的。先进行模块设计,底层的模块写完之后,把新写的模块、商业 IP、复用的旧 IP 等整合在一起,形成一个完整的设计。

其实硬件描述语言,看起来跟 C 语言颇为类似,不过写 C 语言的人,心里想着“hello world”,写 Verilog HDL 的人,心里想着电路图。

我给你展示一段编码,用 Verilog HDL 写的寄存器传输级设计如下图:

跟其它的软件项目一样,在设计的同时,验证也要并行进行。验证是芯片设计中最为耗时耗力的工序,ARM 的技术白皮书有统计,一般一个项目的 40% 资源是用在验证阶段的。

逻辑综合

设计验证完成之后,还有一个步骤,叫逻辑综合 (Logic Synthesis),就是用 EDA 工具把寄存器传输级设计 RTL 描述变网表(Netlist),非常类似于编译器把 C 语言翻译成机器语言的过程。从这一步开始,芯片的设计就和具体的晶圆代工厂和具体工艺绑定在一起,设计开始具有物理特征了。

网表表示的电路如下图,它其实就是描述电路元件相互之间的连接关系。

逻辑综合,对于半导体设计公司不难,但是却是 EDA 公司的核心产品之一。在实现流程中,就背后算法而言,综合一定是最难最复杂的步骤。一个晶圆厂,并不仅仅要有先进工艺,提供给设计公司的设计工具包 PDK(Process Design Kit)和 EDA 厂商的支持也非常重要。

DFT(可测试性设计)

除了以上两步,前端设计还有一个步骤就是 DFT(Design For Test)。所谓 DFT,就是预先规划并插入各种用于芯片测试的逻辑电路。芯片制造后期,在封测阶段中,很多测试需要依赖 DFT 的设计。

完成以上工作后,前端设计团队就可以将生成的网表交给后端实现团队,开始物理设计了。当然这个过程不是一蹴而就的,前端设计工程师往往要多次,不同层次的反复综合、验证,各种设计规则检查,既要确保设计的正确性,又要保证设计的布局布线可行且优化。

整个逻辑设计阶段,你可以这样理解:架构师写在文档上的指标与功能,是需要设计团队通过一行行的代码实现出来的。

物理实现

在前端设计结束后,后端也就是物理实现需要完成布局布线,这个时候,需要把网表转换成制造工厂可以看懂的文件,也就是转化为制造工厂可以用来制造光罩的图形文件。

后端设计的主要步骤可以总结为:布局规划 Floorplan→布局 Placement→时钟树综合CTS→布线 Routing →物理验证。

布局规划就是在总体上确定各种电路的摆放位置,它是后端实现中最为重要的一个环节。我这里放了一张图,你可以看下苹果 A11 的布局规划是怎么样的。

芯片的面积、时序收敛、稳定性、走线难易,基本上都是受布局规划的影响。在实际项目中,往往此时还有未完成的模块,就要预留位置。

规划之后,在指定区域摆放元器件,就是布局,而把各个元器件连接起来,就是布线。一颗芯片的树状的时钟信号线路非常重要,往往需要单独布线,因此还有一个专门的名称:时钟树综合。最后,要做验证。

我说得简单,其实这就是在指尖上建高楼,在小小的芯片上放置上百亿个晶体管,纳米级的单位,幸而有 EDA 工具辅助,这不是人力所及的工程。

一颗芯片做得好不好,在决策阶段取决于市场需求理解的是否深刻,在逻辑设计阶段取决于工程师的能力强不强,而在物理实现阶段基本取决于 EDA 工具玩得好不好。

在芯片设计进入纳米时代之后,布局布线的复杂度呈指数增长,从布局规划到布局布线,时钟树综合,每一步涉及到的算法在近年都有颠覆性的革新。这些步骤,都高度的依赖EDA 工具。要对 EDA 工具有深度理解,并且要理解 EDA 工具背后的方法学。

整个芯片设计流程就是一个设计、优化、验证的不断迭代的过程,每一步如果不能满足要求,例如时序不能满足目标要求,或者存在物理规则违规,信号完整性不合格,都要重复之前的过程,直至满足要求为止,才能进行下一步。

在项目早期,任何的问题,都可以通过修改 RTL,然后重做后续步骤来完成。因此大项目,往往有多个版本火车并行在跑。

在项目后期,特别是在最后阶段发现个别电路小问题 ,可以进行工程更改(Engineering Change Order,ECO)。ECO 有专门的 EDA 工具和流程,我就不展开说了。

物理设计完成之后就形成了下图展示的电路图。图中可以看到蓝、红等不同颜色,每种颜色就代表着一张光罩。这个时候的芯片设计就可以以 GDSII 的文件格式从设计公司移交给芯片代工厂了。自此,设计完成,制造流程开始。

小结

我们了解了一颗芯片的诞生,第一步就是芯片设计,有几个重点,简单给你总结一下。

- 芯片项目是人类历史上最细微也是最宏大的工程,研发投入大,项目收益高。

- 在需求分析之后,进入芯片设计过程。芯片的设计过程可分为两个部分,分别为:前端

设计(也称逻辑设计)和后端设计(也称物理实现),这两个部分并没有统一严格的界

限,凡涉及到与工艺有关的设计都可称为后端设计。 - 一颗芯片做得好不好,在决策阶段取决于市场需求理解的是否深刻,在逻辑设计阶段取

决于工程师的能力强不强,而在物理实现阶段基本取决于 EDA 工具玩得好不好。 - 整个芯片设计流程是一个设计,优化,验证的不断迭代的过程。