基于VerilogHDL的学号显示

基于VerilogHDL的学号显示

一、准备工作:

环境软件:quartus II 9.0

编写语言:VerilogHDL

开发板:Cyclone II FPGA 2C70

二、功能要求:

1)用八个数码管显示;

2)学号按照10hz 的时钟的节拍从右而左进入,从学号的高位开始进入;

3)8位学号全部进入后停顿5秒,然后全部熄灭,再重新开始;

三、要求:

1)设计要用状态机

2)信号源模块输出10hz的基准时钟,用于同步学号显示。

3)设计应有学号的BCD码和7段码输出,仿真波形要有BCD 码学号

学号构成: 2000 + 学号后4 位

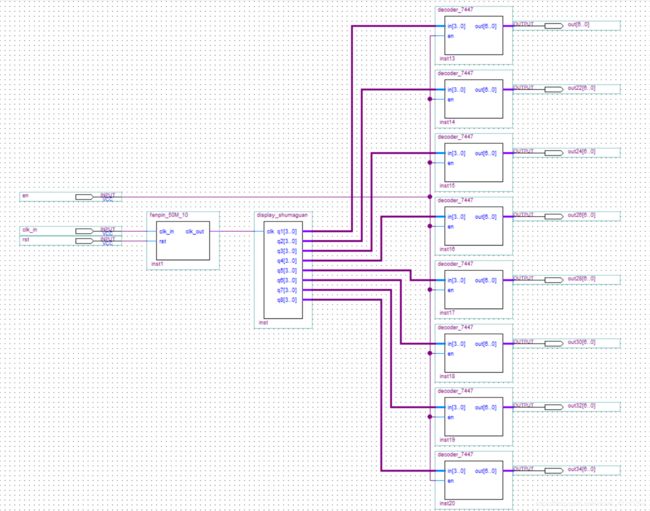

四、顶层设计

五、底层基于VerligHDL的编写

①状态机__学号编码__数码管控制程序

//程序功能:数码管显示学号

module display_shumaguan

(

clk,

q1, q2, q3, q4, q5, q6, q7, q8,

state

);

input clk;

output reg [3:0] q1, q2, q3, q4, q5, q6, q7, q8; //输出给译码器进行译码,用于学号输出的输出端

integer i = 1'd 0; //用于延时,给脉冲计数的临时变量

output integer state = 4'b 0000; //状态变化

//学号:20000131的二进制码

parameter temp_1 = 4'b 0010, temp_2 = 4'b 0000,temp_3 = 4'b 0000,temp_4 = 4'b 0000,

temp_5 = 4'b 0000, temp_6 = 4'b 0001,temp_7 = 4'b 0011,temp_8 = 4'b 0001;

//给9种状态进行编码,S0--S8

parameter S0 = 4'b 0000, S1 = 4'b 0001, S2 = 4'b 0010, S3 = 4'b 0011,

S4 = 4'b 0100, S5 = 4'b 0101, S6 = 4'b 0110, S7 = 4'b 0111,

S8 = 4'b 1000;

always @(posedge clk)

begin

case(state)

S0: //初始状态,输出全为1,使数码管熄灭

begin

state <= S1;

q1 = 4'b 1111; q2 = 4'b 1111; q3 = 4'b 1111; q4 = 4'b 1111;

q5 = 4'b 1111; q6 = 4'b 1111; q7 = 4'b 1111; q8 = 4'b 1111;

end

//分别把学号的二进制数,随着状态的转移,依次输出

S1:

begin

q1 = temp_1;

state <= S2;

end

S2:

begin

q2 = temp_1;q1 = temp_2;

state <= S3;

end

S3:

begin

q3 = temp_1; q2 = temp_2;q1 = temp_3;

state <= S4;

end

S4:

begin

q4 = temp_1; q3 = temp_2; q2 = temp_3; q1 = temp_4;

state <= S5;

end

S5:

begin

q5 = temp_1; q4 = temp_2; q3 = temp_3; q2 = temp_4;

q1 = temp_5;

state <= S6;

end

S6:

begin

q6 = temp_1; q5 = temp_2; q4 = temp_3; q3 = temp_4;

q2 = temp_5;q1 = temp_6;

state <= S7;

end

S7:

begin

q7 = temp_1; q6 = temp_2; q5 = temp_3; q4 = temp_4;

q3 = temp_5; q2 = temp_6; q1 = temp_7;

state <= S8;

end

S8:

begin

end

if(i >= 50) //计数50个上升沿后,再转移到S0状态,即延时5s

begin

state <= S0;

i = 0;

end

else

begin

i= i + 1;

q8 = temp_1; q7 = temp_2; q6 = temp_3; q5 = temp_4;

q4 = temp_5; q3 = temp_6; q2 = temp_7; q1 = temp_8;

end

end

default:

begin

q1 = 4'b 1111; q2 = 4'b 1111; q3 = 4'b 1111; q4 = 4'b 1111;

q5 = 4'b 1111; q6 = 4'b 1111; q7 = 4'b 1111; q8 = 4'b 1111;

end

endcase

end

endmodule

②50MHz频率转换为10Hz时钟输出程序

//分模块功能:50M_10Hz分频

module fenpin_50M_10

(

clk_in, //时钟输入端

rst, //时钟复位端

clk_out //时钟输出端

);

input clk_in, rst;

output reg clk_out;

reg [25:0] cnt; //时钟计数

always @(posedge clk_in or negedge rst)

begin

if (!rst)

cnt <= 26'b 0;

else

begin

cnt = cnt + 1'b 1;

if(cnt == 5000000)

cnt <= 1'b 0;

else if(cnt < 2500000)

clk_out = 1'b 0;

else if(cnt >= 2500000)

clk_out = 1'b 1;

end

end

endmodule

③7447译码器程序

//分模块功能:7447译码器

module decoder_7447

(

in,

out,

en

);

input [3:0]in, en;

output reg [6:0] out;

always @(*)

begin

if(!en)

out = 7'b 111_1111;

else

begin

case(in)

4'b 0000: out = 7'b 000_0001;

4'b 0001: out = 7'b 100_1111;

4'b 0010: out = 7'b 001_0010;

4'b 0011: out = 7'b 000_0110;

4'b 0100: out = 7'b 100_1100;

4'b 0101: out = 7'b 010_0100;

4'b 0110: out = 7'b 110_0000;

4'b 0111: out = 7'b 000_1111;

4'b 1000: out = 7'b 000_0000;

4'b 1001: out = 7'b 000_1100;

4'b 1010: out = 7'b 111_0010;

4'b 1011: out = 7'b 110_0110;

4'b 1100: out = 7'b 101_1100;

4'b 1101: out = 7'b 011_0100;

4'b 1110: out = 7'b 111_0000;

4'b 1111: out = 7'b 111_1111;

default: out = 7'b 111_1111;

endcase

end

end

endmodule