手把手带你实现SDRAM控制器(带Verilog代码)

上篇博客,我们了解了SDRAM的控制命令以及寻址方式,SDRAM芯片需要配合专门的控制电路使用才能发挥功能,这一节我们将一步步分析,使用Verilog搭建一个SDRAM驱动控制器。

目录

学习目标

问题分析

初始化模块

信息收集

模块接口确定

状态机设计

仿真测试

Modelsim仿真:

学习目标

- 搭建SDRAM控制器,能读,能写,并且可以自动初始化以及自动刷新。

- 学习分析问题和使用Verilog解决问题的方法。

问题分析

数字系统自顶向下的的设计原则,我们首先可以分析目标中的功能。不难看出SDRAM控制器应该包含以下模块:

- 初始化模块

- 读控制模块

- 写控制模块

- 自动刷新模块

各个模块将复用SDRAM顶层模块的输出接口,因此将会存在一个总线仲裁的问题,例如当自刷新模块和读模块同时发出请求时,而我们只能响应其中一个,所以我们解决把输出接口交给谁的问题,因此引出第五个模块:仲裁模块。

为了验证设计的需要,我们设计的模块接口兼容野火电子的测试平台接口,各部分关系图如下:

初始化模块

SDRAM在上电之后,在执行正常操作之前需要先执行一次初始化操作。

初始化的流程都是固定的,查看参考手册给的信息可以确定初始化需要顺序执行以下操作:

- 给SDRAM上电,CKE设置为高电平,加载稳定的时钟。

- 执行空指令,并且持续100us。

- 100us过后执行预充电指令,并选中所有Bank(A10为高电平)。

- 预充电指令写入后,等待tRP时间,写入自动刷新命令。

- 之后保持空命令,持续tRC时间。

- tRC时间过后,在此写入自动刷新命令。

- 自动刷新命令写入后,写入空操作命令持续tRC时间。

- 等待时间结束后,即可写入模式寄存器配置指令,地址总线 A0-A11 参数不同 辅助模式寄存器不同模式的设置。

- 模式寄存器配置指令写入后,还需要保持空操 作命令持续 tMRD 时间。

- tMRD时间过后,SDRAM初始化即完成。

观察上述步骤,我们的脑海中肯定一直回荡着:计数器~、状态机~ ,对的,是这样的,完全没错!这个模块的设计主要就是围绕 状态机,佐以计数器。

抛开状态机细节不谈,我们下一步应该要收集我们需要的资料信息:

信息收集

- 时钟资源:100MHz系统时钟,一个周期就是10us

- T=100us 为最小等待时间,我们在使用 SDRAM 时,等待时间 T 可适当延长,设定为200us。

- 开发板的SDRAM信号为W9825G6KH,tRP为两个时钟周期,tMRD3个时钟周期,tRC7个时钟周期。

- 初始化过程中,至少进行两次自动刷新,也可适当增加刷新次数,设定为8次。

- 使用的命令集:NOP=4‘b0111,P_CHARGE=4’b0010,AUTO_REF = 4'b0001,M_REG_SET= 4'b0000。

模块接口确定

本状态机属于穆尔型状态机,时钟和复位接口作为仅有的两个输入,输出则根据SDRAM命令集接口有 init_cmd (4bit) 、init_ba(Bank辅助,2bit),init_addr(地址辅助,13bit),init_end(完成信号,1bit)

状态机设计

状态机的设计有三大要素需要考虑:1、状态数目,2、状态转移条件,3、状态输出。

首先我们要设计出状态的数目,我们可以由前面的初始化步骤画出我们的状态转移图:

平板太滑了,展现不出本人的书法水平,所以大家将就着看。

可以看到,我们的状态机可以设计9个状态去实现它,可能有同学会问,为什么等待状态也要设置好几个不同的状态呀?能不能只设计一个?这是个好问题,其实这四个等待状态就相当于一个等待状态,我们的计数器也只设计一个,然后每个状态会传递不同的计数周期参数,并在计数完成时清零。当然也不是不可以每个状态设计一个计数器,这样代码会简单很多,其实我也建议大家这样做,我觉得Verilog代码设计思路越简单越好,不要像带着C语言那样一个main走天下的思路去写Verilog。

接下来就是代码实现:

// 刷新模块 New_Designed By BUCT WWD 2022/9/7

// SDRAM初始化模块,初始化步骤:上电--延时200us--预充电--刷新x8--寄存器设定--完成

module sdram_init(

input wire sys_clk, //系统时钟信号

input wire sys_rst_n,//系统复位信号

output wire[1:0] init_ba, //Bank辅助位

output wire[3:0] init_cmd,//命令位

output wire[12:0] init_addr,//地址辅助位

output wire init_end //初始化结束标志

);

parameter IDLE = 4'd0,Wait1 = 4'd1,P_CHAR = 4'd2,Wait2 =4'd3,Auto_REF=4'd4,Wait3=4'd5,MRS=4'd6,Wait4=4'd7,OK=4'd8;//九个状态

parameter Init_t = 15'd20000,//初始化200us,各项等待参数

TRP_t = 15'd2,

TRC_t = 15'd7,

TMRD_t = 15'd3;

parameter P_CHARGE = 4'b0010, //指令集

Au_REF = 4'b0001,

NOP = 4'b0111,

M_REG_SET = 4'b0000;

parameter REF_TIME = 4'd8; //自刷新次数参数

reg[3:0] state,next_state;

reg[14:0] cnt_now; //延时长度寄存器

reg[14:0] cnt_value; //计时计数器值

reg[3:0] REF_cnt; //刷新计数

reg[1:0] init_ba_reg;

reg[3:0] init_cmd_reg;

reg[12:0] init_addr_reg;

reg init_end_reg;

always@(posedge sys_clk or negedge sys_rst_n)begin//状态转移

if(sys_rst_n ==1'b0)

state <= IDLE;

else

state <= next_state;

end

always@(posedge sys_clk or negedge sys_rst_n)begin//计时器模块

if(sys_rst_n ==1'b0)

cnt_value <= 15'd0;

else if(cnt_value == cnt_now)//计满自动清零

cnt_value <= 15'd0;

else

cnt_value <= cnt_value +15'd1;

end

always@(posedge sys_clk or negedge sys_rst_n)begin //刷新次数计数器

if(sys_rst_n ==1'b0)

REF_cnt <= 4'd0;

else if((REF_cnt == REF_TIME)&&(cnt_value == 15'd7))

REF_cnt <= 4'd0;

else if(next_state==Auto_REF)

REF_cnt <= REF_cnt + 4'd1;

else

REF_cnt <= REF_cnt;

end

always@(*)begin //状态转移判断模块,根据计时时间判断是否已经持续相应时间长度

if(sys_rst_n ==1'b0)begin

next_state = IDLE;

end else begin

case(state)

IDLE: next_state = Wait1;

Wait1:if(cnt_value == cnt_now)

next_state = P_CHAR;

else

next_state = state;

P_CHAR:next_state = Wait2;

Wait2:if(cnt_value == cnt_now)

next_state = Auto_REF;

else

next_state = state;

Auto_REF:next_state = Wait3;

Wait3:if((REF_cnt == REF_TIME)&&(cnt_value == cnt_now))//自刷新的转移条件还要满足重复次数

next_state = MRS;

else if(cnt_value == cnt_now)

next_state = Auto_REF;

else

next_state = state;

MRS:next_state = Wait4;

Wait4:if(cnt_value==cnt_now)

next_state = OK;

else

next_state = state;

OK: next_state =OK;

endcase

end

end

always@(posedge sys_clk or negedge sys_rst_n)begin

/*各个state持续时间只的设定,特点:时序模块,由下一个状态判断,

这样,在切换状态的一瞬间,计数器执行清零操作,目标计数值被重新赋值,这样就实现了延时参数的传递*/

if(sys_rst_n ==1'b0)begin

cnt_now <= 15'd0;

end else begin

case(next_state)

IDLE:cnt_now <= 15'd0;

Wait1: cnt_now <= Init_t;

P_CHAR:cnt_now <= 15'd0;

Wait2:cnt_now <= TRP_t;

Auto_REF:cnt_now <= 15'd0;

Wait3:cnt_now <= TRC_t;

MRS:cnt_now <= 15'd0;

Wait4:cnt_now <= TMRD_t;

OK:cnt_now <=15'd0;

endcase

end

end

always@(posedge sys_clk or negedge sys_rst_n)begin //输出模块,三段式状态机

if(sys_rst_n == 1'b0)begin

init_cmd_reg <= NOP;

init_ba_reg <= 2'b11;

init_addr_reg <= 13'h1fff;

init_end_reg <= 1'b0;

end else

case(next_state)

IDLE,Wait1,Wait2,Wait3,Wait4: begin

init_cmd_reg <= NOP;

init_ba_reg <= 2'b11;

init_addr_reg <= 13'h1fff;

end

P_CHAR:begin

init_cmd_reg <= P_CHARGE;

init_ba_reg <= 2'b11;

init_addr_reg <= 13'h1fff;

end

Auto_REF:begin

init_cmd_reg <= Au_REF;

init_ba_reg <= 2'b11;

init_addr_reg <= 13'h1fff;

end

MRS:begin

init_cmd_reg <= M_REG_SET;

init_ba_reg <= 2'b00;

init_addr_reg <=

{ //地址辅助配置模式寄存器,参数不同,配置的模式不同

3'b000,//A12-A10:预留

1'b0, //A9=0:读写方式,0:突发读&突发写,1:突发读&单写

2'b00, //{A8,A7}=00:标准模式,默认

3'b011,//{A6,A5,A4}=011:CAS 潜伏期,010:2,011:3,其他:保留

1'b0, //A3=0:突发传输方式,0:顺序,1:隔行

3'b111 //{A2,A1,A0}=111:突发长度,000:单字节,001:2 字节

//010:4 字节,011:8 字节,111:整页,其他:保留

};

end

OK:begin

init_cmd_reg <= NOP;

init_ba_reg <= 2'b11;

init_addr_reg <= 13'h1fff;

init_end_reg <= 1'b1;

end

endcase

end

//最后由于输出是线网,因此需要连续赋值

assign init_cmd = init_cmd_reg;

assign init_addr = init_addr_reg;

assign init_ba = init_ba_reg;

assign init_end = init_end_reg;

endmodule我写的这个状态机有几个特点,第一采用变量少,第二采用的计数器少,第三逻辑简单,大家可以好好体会一下如何让状态机的状态延长时间的方法。事实上我们可以发现,初始化模块所要求的延时都为时钟周期的整数,并且不会有同时两个延时,整个模块的计数器只有两个:自刷新计数器和延时计数器。我们只需要在每个状态来临时赋给它们相应的计数参数,就可以实现单计数器,多状态共用。

仿真测试

TB文件

为了验证我们的状态机设计,我们采用野火的验证平台,这次的测试工程共包含三个部分:

- sdram_init.v

- tb_sdram.v

- sdram_model_plus.v //sdram模块模拟

- PLL IP核

`timescale 1ns/1ns

// Author : EmbedFire

// Create Date : 2019/08/25

// Module Name : tb_sdram_init

// Project Name : uart_sdram

// Target Devices: Altera EP4CE10F17C8N

// Tool Versions : Quartus 13.0

// Description : SDRAM初始化模块仿真

//

// Revision : V1.0

// Additional Comments:

//

// 实验平台: 野火_征途Pro_FPGA开发板

// 公司 : http://www.embedfire.com

// 论坛 : http://www.firebbs.cn

// 淘宝 : https://fire-stm32.taobao.com

module tb_sdram_init();

//********************************************************************//

//****************** Internal Signal and Defparam ********************//

//********************************************************************//

//wire define

//clk_gen

wire clk_50m ; //PLL输出50M时钟

wire clk_100m ; //PLL输出100M时钟

wire clk_100m_shift ; //PLL输出100M时钟,相位偏移-30deg

wire locked ; //PLL时钟锁定信号

wire rst_n ; //复位信号,低有效

//sdram_init

wire [3:0] init_cmd ; //初始化阶段指令

wire [1:0] init_ba ; //初始化阶段L-Bank地址

wire [12:0] init_addr ; //初始化阶段地址总线

wire init_end ; //初始化完成信号

//reg define

reg sys_clk ; //系统时钟

reg sys_rst_n ; //复位信号

//defparam

//重定义仿真模型中的相关参数

defparam sdram_model_plus_inst.addr_bits = 13; //地址位宽

defparam sdram_model_plus_inst.data_bits = 16; //数据位宽

defparam sdram_model_plus_inst.col_bits = 9; //列地址位宽

defparam sdram_model_plus_inst.mem_sizes = 2*1024*1024; //L-Bank容量

//********************************************************************//

//**************************** Clk And Rst ***************************//

//********************************************************************//

//时钟、复位信号

initial

begin

sys_clk = 1'b1 ;

sys_rst_n <= 1'b0 ;

#200

sys_rst_n <= 1'b1 ;

end

always #10 sys_clk = ~sys_clk;

//rst_n:复位信号

assign rst_n = sys_rst_n & locked;

//********************************************************************//

//*************************** Instantiation **************************//

//********************************************************************//

//------------- clk_gen_inst -------------

clk_gen clk_gen_inst (

.inclk0 (sys_clk ),

.areset (~sys_rst_n ),

.c0 (clk_50m ),

.c1 (clk_100m ),

.c2 (clk_100m_shift ),

.locked (locked )

);

//------------- sdram_init_inst -------------

sdram_init sdram_init_inst(

.sys_clk (clk_100m ),

.sys_rst_n (rst_n ),

.init_cmd (init_cmd ),

.init_ba (init_ba ),

.init_addr (init_addr ),

.init_end (init_end )

);

//-------------sdram_model_plus_inst-------------

sdram_model_plus sdram_model_plus_inst(

.Dq ( ),

.Addr (init_addr ),

.Ba (init_ba ),

.Clk (clk_100m_shift ),

.Cke (1'b1 ),

.Cs_n (init_cmd[3] ),

.Ras_n (init_cmd[2] ),

.Cas_n (init_cmd[1] ),

.We_n (init_cmd[0] ),

.Dqm (2'b0 ),

.Debug (1'b1 )

);

endmodulesdram_model

/***************************************************************************************

作者: 李晟

2003-08-27 V0.1 李晟

添加内存模块倒空功能,在外部需要创建事件:sdram_r ,本SDRAM的内容将会按Bank 顺序damp out 至文件

sdram_data.txt 中

×××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××××*/

//2004-03-04 陈乃奎 修改原程序中将BANK的数据转存入TXT文件的格式

//2004-03-16 陈乃奎 修改SDRAM 的初始化数据

//2004/04/06 陈乃奎 将SDRAM的操作命令以字符形式表示,以便用MODELSIM监视

//2004/04/19 陈乃奎 修改参数 parameter tAC = 8;

//2010/09/17 罗瑶 修改sdram的大小,数据位宽,dqm宽度;

/****************************************************************************************

*

* File Name: sdram_model.V

* Version: 0.0f

* Date: July 8th, 1999

* Model: BUS Functional

* Simulator: Model Technology (PC version 5.2e PE)

*

* Dependencies: None

*

* Author: Son P. Huynh

* Email: [email protected]

* Phone: (208) 368-3825

* Company: Micron Technology, Inc.

* Model: sdram_model (1Meg x 16 x 4 Banks)

*

* Description: 64Mb SDRAM Verilog model

*

* Limitation: - Doesn't check for 4096 cycle refresh

*

* Note: - Set simulator resolution to "ps" accuracy

* - Set Debug = 0 to disable $display messages

*

* Disclaimer: THESE DESIGNS ARE PROVIDED "AS IS" WITH NO WARRANTY

* WHATSOEVER AND MICRON SPECIFICALLY DISCLAIMS ANY

* IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR

* A PARTICULAR PURPOSE, OR AGAINST INFRINGEMENT.

*

* Copyright ?1998 Micron Semiconductor Products, Inc.

* All rights researved

*

* Rev Author Phone Date Changes

* ---- ---------------------------- ---------- ---------------------------------------

* 0.0f Son Huynh 208-368-3825 07/08/1999 - Fix tWR = 1 Clk + 7.5 ns (Auto)

* Micron Technology Inc. - Fix tWR = 15 ns (Manual)

* - Fix tRP (Autoprecharge to AutoRefresh)

*

* 0.0a Son Huynh 208-368-3825 05/13/1998 - First Release (from 64Mb rev 0.0e)

* Micron Technology Inc.

****************************************************************************************/

`timescale 1ns / 100ps

module sdram_model_plus (Dq, Addr, Ba, Clk, Cke, Cs_n, Ras_n, Cas_n, We_n, Dqm,Debug);

parameter addr_bits = 11;

parameter data_bits = 32;

parameter col_bits = 8;

parameter mem_sizes = 1048576*2-1;//1 Meg

inout [data_bits - 1 : 0] Dq;

input [addr_bits - 1 : 0] Addr;

input [1 : 0] Ba;

input Clk;

input Cke;

input Cs_n;

input Ras_n;

input Cas_n;

input We_n;

input [3 : 0] Dqm; //高低各8bit

//added by xzli

input Debug;

reg [data_bits - 1 : 0] Bank0 [0 : mem_sizes];//存储器类型数据

reg [data_bits - 1 : 0] Bank1 [0 : mem_sizes];

reg [data_bits - 1 : 0] Bank2 [0 : mem_sizes];

reg [data_bits - 1 : 0] Bank3 [0 : mem_sizes];

reg [1 : 0] Bank_addr [0 : 3]; // Bank Address Pipeline

reg [col_bits - 1 : 0] Col_addr [0 : 3]; // Column Address Pipeline

reg [3 : 0] Command [0 : 3]; // Command Operation Pipeline

reg [3 : 0] Dqm_reg0, Dqm_reg1; // DQM Operation Pipeline

reg [addr_bits - 1 : 0] B0_row_addr, B1_row_addr, B2_row_addr, B3_row_addr;

reg [addr_bits - 1 : 0] Mode_reg;

reg [data_bits - 1 : 0] Dq_reg, Dq_dqm;

reg [col_bits - 1 : 0] Col_temp, Burst_counter;

reg Act_b0, Act_b1, Act_b2, Act_b3; // Bank Activate

reg Pc_b0, Pc_b1, Pc_b2, Pc_b3; // Bank Precharge

reg [1 : 0] Bank_precharge [0 : 3]; // Precharge Command

reg A10_precharge [0 : 3]; // Addr[10] = 1 (All banks)

reg Auto_precharge [0 : 3]; // RW AutoPrecharge (Bank)

reg Read_precharge [0 : 3]; // R AutoPrecharge

reg Write_precharge [0 : 3]; // W AutoPrecharge

integer Count_precharge [0 : 3]; // RW AutoPrecharge (Counter)

reg RW_interrupt_read [0 : 3]; // RW Interrupt Read with Auto Precharge

reg RW_interrupt_write [0 : 3]; // RW Interrupt Write with Auto Precharge

reg Data_in_enable;

reg Data_out_enable;

reg [1 : 0] Bank, Previous_bank;

reg [addr_bits - 1 : 0] Row;

reg [col_bits - 1 : 0] Col, Col_brst;

// Internal system clock

reg CkeZ, Sys_clk;

reg [21:0] dd;

// Commands Decode

wire Active_enable = ~Cs_n & ~Ras_n & Cas_n & We_n;

wire Aref_enable = ~Cs_n & ~Ras_n & ~Cas_n & We_n;

wire Burst_term = ~Cs_n & Ras_n & Cas_n & ~We_n;

wire Mode_reg_enable = ~Cs_n & ~Ras_n & ~Cas_n & ~We_n;

wire Prech_enable = ~Cs_n & ~Ras_n & Cas_n & ~We_n;

wire Read_enable = ~Cs_n & Ras_n & ~Cas_n & We_n;

wire Write_enable = ~Cs_n & Ras_n & ~Cas_n & ~We_n;

// Burst Length Decode

wire Burst_length_1 = ~Mode_reg[2] & ~Mode_reg[1] & ~Mode_reg[0];

wire Burst_length_2 = ~Mode_reg[2] & ~Mode_reg[1] & Mode_reg[0];

wire Burst_length_4 = ~Mode_reg[2] & Mode_reg[1] & ~Mode_reg[0];

wire Burst_length_8 = ~Mode_reg[2] & Mode_reg[1] & Mode_reg[0];

// CAS Latency Decode

wire Cas_latency_2 = ~Mode_reg[6] & Mode_reg[5] & ~Mode_reg[4];

wire Cas_latency_3 = ~Mode_reg[6] & Mode_reg[5] & Mode_reg[4];

// Write Burst Mode

wire Write_burst_mode = Mode_reg[9];

wire Debug; // Debug messages : 1 = On; 0 = Off

wire Dq_chk = Sys_clk & Data_in_enable; // Check setup/hold time for DQ

reg [31:0] mem_d;

event sdram_r,sdram_w,compare;

assign Dq = Dq_reg; // DQ buffer

// Commands Operation

`define ACT 0

`define NOP 1

`define READ 2

`define READ_A 3

`define WRITE 4

`define WRITE_A 5

`define PRECH 6

`define A_REF 7

`define BST 8

`define LMR 9

// // Timing Parameters for -75 (PC133) and CAS Latency = 2

// parameter tAC = 8; //test 6.5

// parameter tHZ = 7.0;

// parameter tOH = 2.7;

// parameter tMRD = 2.0; // 2 Clk Cycles

// parameter tRAS = 44.0;

// parameter tRC = 66.0;

// parameter tRCD = 20.0;

// parameter tRP = 20.0;

// parameter tRRD = 15.0;

// parameter tWRa = 7.5; // A2 Version - Auto precharge mode only (1 Clk + 7.5 ns)

// parameter tWRp = 0.0; // A2 Version - Precharge mode only (15 ns)

// Timing Parameters for -7 (PC143) and CAS Latency = 3

parameter tAC = 6.5; //test 6.5

parameter tHZ = 5.5;

parameter tOH = 2;

parameter tMRD = 2.0; // 2 Clk Cycles

parameter tRAS = 48.0;

parameter tRC = 70.0;

parameter tRCD = 20.0;

parameter tRP = 20.0;

parameter tRRD = 14.0;

parameter tWRa = 7.5; // A2 Version - Auto precharge mode only (1 Clk + 7.5 ns)

parameter tWRp = 0.0; // A2 Version - Precharge mode only (15 ns)

// Timing Check variable

integer MRD_chk;

integer WR_counter [0 : 3];

time WR_chk [0 : 3];

time RC_chk, RRD_chk;

time RAS_chk0, RAS_chk1, RAS_chk2, RAS_chk3;

time RCD_chk0, RCD_chk1, RCD_chk2, RCD_chk3;

time RP_chk0, RP_chk1, RP_chk2, RP_chk3;

integer test_file;

//*****display the command of the sdram**************************************

parameter Mode_Reg_Set =4'b0000;

parameter Auto_Refresh =4'b0001;

parameter Row_Active =4'b0011;

parameter Pre_Charge =4'b0010;

parameter PreCharge_All =4'b0010;

parameter Write =4'b0100;

parameter Write_Pre =4'b0100;

parameter Read =4'b0101;

parameter Read_Pre =4'b0101;

parameter Burst_Stop =4'b0110;

parameter Nop =4'b0111;

parameter Dsel =4'b1111;

wire [3:0] sdram_control;

reg cke_temp;

reg [8*13:1] sdram_command;

always@(posedge Clk)

cke_temp<=Cke;

assign sdram_control={Cs_n,Ras_n,Cas_n,We_n};

always@(sdram_control or cke_temp)

begin

case(sdram_control)

Mode_Reg_Set: sdram_command<="Mode_Reg_Set";

Auto_Refresh: sdram_command<="Auto_Refresh";

Row_Active: sdram_command<="Row_Active";

Pre_Charge: sdram_command<="Pre_Charge";

Burst_Stop: sdram_command<="Burst_Stop";

Dsel: sdram_command<="Dsel";

Write: if(cke_temp==1)

sdram_command<="Write";

else

sdram_command<="Write_suspend";

Read: if(cke_temp==1)

sdram_command<="Read";

else

sdram_command<="Read_suspend";

Nop: if(cke_temp==1)

sdram_command<="Nop";

else

sdram_command<="Self_refresh";

default: sdram_command<="Power_down";

endcase

end

//*****************************************************

initial

begin

//test_file=$fopen("test_file.txt");

end

initial

begin

Dq_reg = {data_bits{1'bz}};

{Data_in_enable, Data_out_enable} = 0;

{Act_b0, Act_b1, Act_b2, Act_b3} = 4'b0000;

{Pc_b0, Pc_b1, Pc_b2, Pc_b3} = 4'b0000;

{WR_chk[0], WR_chk[1], WR_chk[2], WR_chk[3]} = 0;

{WR_counter[0], WR_counter[1], WR_counter[2], WR_counter[3]} = 0;

{RW_interrupt_read[0], RW_interrupt_read[1], RW_interrupt_read[2], RW_interrupt_read[3]} = 0;

{RW_interrupt_write[0], RW_interrupt_write[1], RW_interrupt_write[2], RW_interrupt_write[3]} = 0;

{MRD_chk, RC_chk, RRD_chk} = 0;

{RAS_chk0, RAS_chk1, RAS_chk2, RAS_chk3} = 0;

{RCD_chk0, RCD_chk1, RCD_chk2, RCD_chk3} = 0;

{RP_chk0, RP_chk1, RP_chk2, RP_chk3} = 0;

$timeformat (-9, 0, " ns", 12);

//$readmemh("bank0.txt", Bank0);

//$readmemh("bank1.txt", Bank1);

//$readmemh("bank2.txt", Bank2);

//$readmemh("bank3.txt", Bank3);

/*

for(dd=0;dd<=mem_sizes;dd=dd+1)

begin

Bank0[dd]=dd[data_bits - 1 : 0];

Bank1[dd]=dd[data_bits - 1 : 0]+1;

Bank2[dd]=dd[data_bits - 1 : 0]+2;

Bank3[dd]=dd[data_bits - 1 : 0]+3;

end

*/

initial_sdram(0);

end

task initial_sdram;

input data_sign;

reg [3:0] data_sign;

for(dd=0;dd<=mem_sizes;dd=dd+1)

begin

mem_d = {data_sign,data_sign,data_sign,data_sign,data_sign,data_sign,data_sign,data_sign};

if(data_bits==16)

begin

Bank0[dd]=mem_d[15:0];

Bank1[dd]=mem_d[15:0];

Bank2[dd]=mem_d[15:0];

Bank3[dd]=mem_d[15:0];

end

else if(data_bits==32)

begin

Bank0[dd]=mem_d[31:0];

Bank1[dd]=mem_d[31:0];

Bank2[dd]=mem_d[31:0];

Bank3[dd]=mem_d[31:0];

end

end

endtask

// System clock generator

always

begin

@(posedge Clk)

begin

Sys_clk = CkeZ;

CkeZ = Cke;

end

@(negedge Clk)

begin

Sys_clk = 1'b0;

end

end

always @ (posedge Sys_clk) begin

// Internal Commamd Pipelined

Command[0] = Command[1];

Command[1] = Command[2];

Command[2] = Command[3];

Command[3] = `NOP;

Col_addr[0] = Col_addr[1];

Col_addr[1] = Col_addr[2];

Col_addr[2] = Col_addr[3];

Col_addr[3] = {col_bits{1'b0}};

Bank_addr[0] = Bank_addr[1];

Bank_addr[1] = Bank_addr[2];

Bank_addr[2] = Bank_addr[3];

Bank_addr[3] = 2'b0;

Bank_precharge[0] = Bank_precharge[1];

Bank_precharge[1] = Bank_precharge[2];

Bank_precharge[2] = Bank_precharge[3];

Bank_precharge[3] = 2'b0;

A10_precharge[0] = A10_precharge[1];

A10_precharge[1] = A10_precharge[2];

A10_precharge[2] = A10_precharge[3];

A10_precharge[3] = 1'b0;

// Dqm pipeline for Read

Dqm_reg0 = Dqm_reg1;

Dqm_reg1 = Dqm;

// Read or Write with Auto Precharge Counter

if (Auto_precharge[0] == 1'b1) begin

Count_precharge[0] = Count_precharge[0] + 1;

end

if (Auto_precharge[1] == 1'b1) begin

Count_precharge[1] = Count_precharge[1] + 1;

end

if (Auto_precharge[2] == 1'b1) begin

Count_precharge[2] = Count_precharge[2] + 1;

end

if (Auto_precharge[3] == 1'b1) begin

Count_precharge[3] = Count_precharge[3] + 1;

end

// tMRD Counter

MRD_chk = MRD_chk + 1;

// tWR Counter for Write

WR_counter[0] = WR_counter[0] + 1;

WR_counter[1] = WR_counter[1] + 1;

WR_counter[2] = WR_counter[2] + 1;

WR_counter[3] = WR_counter[3] + 1;

// Auto Refresh

if (Aref_enable == 1'b1) begin

if (Debug) $display ("at time %t AREF : Auto Refresh", $time);

// Auto Refresh to Auto Refresh

if (($time - RC_chk < tRC)&&Debug) begin

$display ("at time %t ERROR: tRC violation during Auto Refresh", $time);

end

// Precharge to Auto Refresh

if (($time - RP_chk0 < tRP || $time - RP_chk1 < tRP || $time - RP_chk2 < tRP || $time - RP_chk3 < tRP)&&Debug) begin

$display ("at time %t ERROR: tRP violation during Auto Refresh", $time);

end

// Precharge to Refresh

if (Pc_b0 == 1'b0 || Pc_b1 == 1'b0 || Pc_b2 == 1'b0 || Pc_b3 == 1'b0) begin

$display ("at time %t ERROR: All banks must be Precharge before Auto Refresh", $time);

end

// Record Current tRC time

RC_chk = $time;

end

// Load Mode Register

if (Mode_reg_enable == 1'b1) begin

// Decode CAS Latency, Burst Length, Burst Type, and Write Burst Mode

if (Pc_b0 == 1'b1 && Pc_b1 == 1'b1 && Pc_b2 == 1'b1 && Pc_b3 == 1'b1) begin

Mode_reg = Addr;

if (Debug) begin

$display ("at time %t LMR : Load Mode Register", $time);

// CAS Latency

if (Addr[6 : 4] == 3'b010)

$display (" CAS Latency = 2");

else if (Addr[6 : 4] == 3'b011)

$display (" CAS Latency = 3");

else

$display (" CAS Latency = Reserved");

// Burst Length

if (Addr[2 : 0] == 3'b000)

$display (" Burst Length = 1");

else if (Addr[2 : 0] == 3'b001)

$display (" Burst Length = 2");

else if (Addr[2 : 0] == 3'b010)

$display (" Burst Length = 4");

else if (Addr[2 : 0] == 3'b011)

$display (" Burst Length = 8");

else if (Addr[3 : 0] == 4'b0111)

$display (" Burst Length = Full");

else

$display (" Burst Length = Reserved");

// Burst Type

if (Addr[3] == 1'b0)

$display (" Burst Type = Sequential");

else if (Addr[3] == 1'b1)

$display (" Burst Type = Interleaved");

else

$display (" Burst Type = Reserved");

// Write Burst Mode

if (Addr[9] == 1'b0)

$display (" Write Burst Mode = Programmed Burst Length");

else if (Addr[9] == 1'b1)

$display (" Write Burst Mode = Single Location Access");

else

$display (" Write Burst Mode = Reserved");

end

end else begin

$display ("at time %t ERROR: all banks must be Precharge before Load Mode Register", $time);

end

// REF to LMR

if ($time - RC_chk < tRC) begin

$display ("at time %t ERROR: tRC violation during Load Mode Register", $time);

end

// LMR to LMR

if (MRD_chk < tMRD) begin

$display ("at time %t ERROR: tMRD violation during Load Mode Register", $time);

end

MRD_chk = 0;

end

// Active Block (Latch Bank Address and Row Address)

if (Active_enable == 1'b1) begin

if (Ba == 2'b00 && Pc_b0 == 1'b1) begin

{Act_b0, Pc_b0} = 2'b10;

B0_row_addr = Addr [addr_bits - 1 : 0];

RCD_chk0 = $time;

RAS_chk0 = $time;

if (Debug) $display ("at time %t ACT : Bank = 0 Row = %d", $time, Addr);

// Precharge to Activate Bank 0

if ($time - RP_chk0 < tRP) begin

$display ("at time %t ERROR: tRP violation during Activate bank 0", $time);

end

end else if (Ba == 2'b01 && Pc_b1 == 1'b1) begin

{Act_b1, Pc_b1} = 2'b10;

B1_row_addr = Addr [addr_bits - 1 : 0];

RCD_chk1 = $time;

RAS_chk1 = $time;

if (Debug) $display ("at time %t ACT : Bank = 1 Row = %d", $time, Addr);

// Precharge to Activate Bank 1

if ($time - RP_chk1 < tRP) begin

$display ("at time %t ERROR: tRP violation during Activate bank 1", $time);

end

end else if (Ba == 2'b10 && Pc_b2 == 1'b1) begin

{Act_b2, Pc_b2} = 2'b10;

B2_row_addr = Addr [addr_bits - 1 : 0];

RCD_chk2 = $time;

RAS_chk2 = $time;

if (Debug) $display ("at time %t ACT : Bank = 2 Row = %d", $time, Addr);

// Precharge to Activate Bank 2

if ($time - RP_chk2 < tRP) begin

$display ("at time %t ERROR: tRP violation during Activate bank 2", $time);

end

end else if (Ba == 2'b11 && Pc_b3 == 1'b1) begin

{Act_b3, Pc_b3} = 2'b10;

B3_row_addr = Addr [addr_bits - 1 : 0];

RCD_chk3 = $time;

RAS_chk3 = $time;

if (Debug) $display ("at time %t ACT : Bank = 3 Row = %d", $time, Addr);

// Precharge to Activate Bank 3

if ($time - RP_chk3 < tRP) begin

$display ("at time %t ERROR: tRP violation during Activate bank 3", $time);

end

end else if (Ba == 2'b00 && Pc_b0 == 1'b0) begin

$display ("at time %t ERROR: Bank 0 is not Precharged.", $time);

end else if (Ba == 2'b01 && Pc_b1 == 1'b0) begin

$display ("at time %t ERROR: Bank 1 is not Precharged.", $time);

end else if (Ba == 2'b10 && Pc_b2 == 1'b0) begin

$display ("at time %t ERROR: Bank 2 is not Precharged.", $time);

end else if (Ba == 2'b11 && Pc_b3 == 1'b0) begin

$display ("at time %t ERROR: Bank 3 is not Precharged.", $time);

end

// Active Bank A to Active Bank B

if ((Previous_bank != Ba) && ($time - RRD_chk < tRRD)) begin

$display ("at time %t ERROR: tRRD violation during Activate bank = %d", $time, Ba);

end

// Load Mode Register to Active

if (MRD_chk < tMRD ) begin

$display ("at time %t ERROR: tMRD violation during Activate bank = %d", $time, Ba);

end

// Auto Refresh to Activate

if (($time - RC_chk < tRC)&&Debug) begin

$display ("at time %t ERROR: tRC violation during Activate bank = %d", $time, Ba);

end

// Record variables for checking violation

RRD_chk = $time;

Previous_bank = Ba;

end

// Precharge Block

if (Prech_enable == 1'b1) begin

if (Addr[10] == 1'b1) begin

{Pc_b0, Pc_b1, Pc_b2, Pc_b3} = 4'b1111;

{Act_b0, Act_b1, Act_b2, Act_b3} = 4'b0000;

RP_chk0 = $time;

RP_chk1 = $time;

RP_chk2 = $time;

RP_chk3 = $time;

if (Debug) $display ("at time %t PRE : Bank = ALL",$time);

// Activate to Precharge all banks

if (($time - RAS_chk0 < tRAS) || ($time - RAS_chk1 < tRAS) ||

($time - RAS_chk2 < tRAS) || ($time - RAS_chk3 < tRAS)) begin

$display ("at time %t ERROR: tRAS violation during Precharge all bank", $time);

end

// tWR violation check for write

if (($time - WR_chk[0] < tWRp) || ($time - WR_chk[1] < tWRp) ||

($time - WR_chk[2] < tWRp) || ($time - WR_chk[3] < tWRp)) begin

$display ("at time %t ERROR: tWR violation during Precharge all bank", $time);

end

end else if (Addr[10] == 1'b0) begin

if (Ba == 2'b00) begin

{Pc_b0, Act_b0} = 2'b10;

RP_chk0 = $time;

if (Debug) $display ("at time %t PRE : Bank = 0",$time);

// Activate to Precharge Bank 0

if ($time - RAS_chk0 < tRAS) begin

$display ("at time %t ERROR: tRAS violation during Precharge bank 0", $time);

end

end else if (Ba == 2'b01) begin

{Pc_b1, Act_b1} = 2'b10;

RP_chk1 = $time;

if (Debug) $display ("at time %t PRE : Bank = 1",$time);

// Activate to Precharge Bank 1

if ($time - RAS_chk1 < tRAS) begin

$display ("at time %t ERROR: tRAS violation during Precharge bank 1", $time);

end

end else if (Ba == 2'b10) begin

{Pc_b2, Act_b2} = 2'b10;

RP_chk2 = $time;

if (Debug) $display ("at time %t PRE : Bank = 2",$time);

// Activate to Precharge Bank 2

if ($time - RAS_chk2 < tRAS) begin

$display ("at time %t ERROR: tRAS violation during Precharge bank 2", $time);

end

end else if (Ba == 2'b11) begin

{Pc_b3, Act_b3} = 2'b10;

RP_chk3 = $time;

if (Debug) $display ("at time %t PRE : Bank = 3",$time);

// Activate to Precharge Bank 3

if ($time - RAS_chk3 < tRAS) begin

$display ("at time %t ERROR: tRAS violation during Precharge bank 3", $time);

end

end

// tWR violation check for write

if ($time - WR_chk[Ba] < tWRp) begin

$display ("at time %t ERROR: tWR violation during Precharge bank %d", $time, Ba);

end

end

// Terminate a Write Immediately (if same bank or all banks)

if (Data_in_enable == 1'b1 && (Bank == Ba || Addr[10] == 1'b1)) begin

Data_in_enable = 1'b0;

end

// Precharge Command Pipeline for Read

if (Cas_latency_3 == 1'b1) begin

Command[2] = `PRECH;

Bank_precharge[2] = Ba;

A10_precharge[2] = Addr[10];

end else if (Cas_latency_2 == 1'b1) begin

Command[1] = `PRECH;

Bank_precharge[1] = Ba;

A10_precharge[1] = Addr[10];

end

end

// Burst terminate

if (Burst_term == 1'b1) begin

// Terminate a Write Immediately

if (Data_in_enable == 1'b1) begin

Data_in_enable = 1'b0;

end

// Terminate a Read Depend on CAS Latency

if (Cas_latency_3 == 1'b1) begin

Command[2] = `BST;

end else if (Cas_latency_2 == 1'b1) begin

Command[1] = `BST;

end

if (Debug) $display ("at time %t BST : Burst Terminate",$time);

end

// Read, Write, Column Latch

if (Read_enable == 1'b1 || Write_enable == 1'b1) begin

// Check to see if bank is open (ACT)

if ((Ba == 2'b00 && Pc_b0 == 1'b1) || (Ba == 2'b01 && Pc_b1 == 1'b1) ||

(Ba == 2'b10 && Pc_b2 == 1'b1) || (Ba == 2'b11 && Pc_b3 == 1'b1)) begin

$display("at time %t ERROR: Cannot Read or Write - Bank %d is not Activated", $time, Ba);

end

// Activate to Read or Write

if ((Ba == 2'b00) && ($time - RCD_chk0 < tRCD))

$display("at time %t ERROR: tRCD violation during Read or Write to Bank 0", $time);

if ((Ba == 2'b01) && ($time - RCD_chk1 < tRCD))

$display("at time %t ERROR: tRCD violation during Read or Write to Bank 1", $time);

if ((Ba == 2'b10) && ($time - RCD_chk2 < tRCD))

$display("at time %t ERROR: tRCD violation during Read or Write to Bank 2", $time);

if ((Ba == 2'b11) && ($time - RCD_chk3 < tRCD))

$display("at time %t ERROR: tRCD violation during Read or Write to Bank 3", $time);

// Read Command

if (Read_enable == 1'b1) begin

// CAS Latency pipeline

if (Cas_latency_3 == 1'b1) begin

if (Addr[10] == 1'b1) begin

Command[2] = `READ_A;

end else begin

Command[2] = `READ;

end

Col_addr[2] = Addr;

Bank_addr[2] = Ba;

end else if (Cas_latency_2 == 1'b1) begin

if (Addr[10] == 1'b1) begin

Command[1] = `READ_A;

end else begin

Command[1] = `READ;

end

Col_addr[1] = Addr;

Bank_addr[1] = Ba;

end

// Read interrupt Write (terminate Write immediately)

if (Data_in_enable == 1'b1) begin

Data_in_enable = 1'b0;

end

// Write Command

end else if (Write_enable == 1'b1) begin

if (Addr[10] == 1'b1) begin

Command[0] = `WRITE_A;

end else begin

Command[0] = `WRITE;

end

Col_addr[0] = Addr;

Bank_addr[0] = Ba;

// Write interrupt Write (terminate Write immediately)

if (Data_in_enable == 1'b1) begin

Data_in_enable = 1'b0;

end

// Write interrupt Read (terminate Read immediately)

if (Data_out_enable == 1'b1) begin

Data_out_enable = 1'b0;

end

end

// Interrupting a Write with Autoprecharge

if (Auto_precharge[Bank] == 1'b1 && Write_precharge[Bank] == 1'b1) begin

RW_interrupt_write[Bank] = 1'b1;

if (Debug) $display ("at time %t NOTE : Read/Write Bank %d interrupt Write Bank %d with Autoprecharge", $time, Ba, Bank);

end

// Interrupting a Read with Autoprecharge

if (Auto_precharge[Bank] == 1'b1 && Read_precharge[Bank] == 1'b1) begin

RW_interrupt_read[Bank] = 1'b1;

if (Debug) $display ("at time %t NOTE : Read/Write Bank %d interrupt Read Bank %d with Autoprecharge", $time, Ba, Bank);

end

// Read or Write with Auto Precharge

if (Addr[10] == 1'b1) begin

Auto_precharge[Ba] = 1'b1;

Count_precharge[Ba] = 0;

if (Read_enable == 1'b1) begin

Read_precharge[Ba] = 1'b1;

end else if (Write_enable == 1'b1) begin

Write_precharge[Ba] = 1'b1;

end

end

end

// Read with Auto Precharge Calculation

// The device start internal precharge:

// 1. CAS Latency - 1 cycles before last burst

// and 2. Meet minimum tRAS requirement

// or 3. Interrupt by a Read or Write (with or without AutoPrecharge)

if ((Auto_precharge[0] == 1'b1) && (Read_precharge[0] == 1'b1)) begin

if ((($time - RAS_chk0 >= tRAS) && // Case 2

((Burst_length_1 == 1'b1 && Count_precharge[0] >= 1) || // Case 1

(Burst_length_2 == 1'b1 && Count_precharge[0] >= 2) ||

(Burst_length_4 == 1'b1 && Count_precharge[0] >= 4) ||

(Burst_length_8 == 1'b1 && Count_precharge[0] >= 8))) ||

(RW_interrupt_read[0] == 1'b1)) begin // Case 3

Pc_b0 = 1'b1;

Act_b0 = 1'b0;

RP_chk0 = $time;

Auto_precharge[0] = 1'b0;

Read_precharge[0] = 1'b0;

RW_interrupt_read[0] = 1'b0;

if (Debug) $display ("at time %t NOTE : Start Internal Auto Precharge for Bank 0", $time);

end

end

if ((Auto_precharge[1] == 1'b1) && (Read_precharge[1] == 1'b1)) begin

if ((($time - RAS_chk1 >= tRAS) &&

((Burst_length_1 == 1'b1 && Count_precharge[1] >= 1) ||

(Burst_length_2 == 1'b1 && Count_precharge[1] >= 2) ||

(Burst_length_4 == 1'b1 && Count_precharge[1] >= 4) ||

(Burst_length_8 == 1'b1 && Count_precharge[1] >= 8))) ||

(RW_interrupt_read[1] == 1'b1)) begin

Pc_b1 = 1'b1;

Act_b1 = 1'b0;

RP_chk1 = $time;

Auto_precharge[1] = 1'b0;

Read_precharge[1] = 1'b0;

RW_interrupt_read[1] = 1'b0;

if (Debug) $display ("at time %t NOTE : Start Internal Auto Precharge for Bank 1", $time);

end

end

if ((Auto_precharge[2] == 1'b1) && (Read_precharge[2] == 1'b1)) begin

if ((($time - RAS_chk2 >= tRAS) &&

((Burst_length_1 == 1'b1 && Count_precharge[2] >= 1) ||

(Burst_length_2 == 1'b1 && Count_precharge[2] >= 2) ||

(Burst_length_4 == 1'b1 && Count_precharge[2] >= 4) ||

(Burst_length_8 == 1'b1 && Count_precharge[2] >= 8))) ||

(RW_interrupt_read[2] == 1'b1)) begin

Pc_b2 = 1'b1;

Act_b2 = 1'b0;

RP_chk2 = $time;

Auto_precharge[2] = 1'b0;

Read_precharge[2] = 1'b0;

RW_interrupt_read[2] = 1'b0;

if (Debug) $display ("at time %t NOTE : Start Internal Auto Precharge for Bank 2", $time);

end

end

if ((Auto_precharge[3] == 1'b1) && (Read_precharge[3] == 1'b1)) begin

if ((($time - RAS_chk3 >= tRAS) &&

((Burst_length_1 == 1'b1 && Count_precharge[3] >= 1) ||

(Burst_length_2 == 1'b1 && Count_precharge[3] >= 2) ||

(Burst_length_4 == 1'b1 && Count_precharge[3] >= 4) ||

(Burst_length_8 == 1'b1 && Count_precharge[3] >= 8))) ||

(RW_interrupt_read[3] == 1'b1)) begin

Pc_b3 = 1'b1;

Act_b3 = 1'b0;

RP_chk3 = $time;

Auto_precharge[3] = 1'b0;

Read_precharge[3] = 1'b0;

RW_interrupt_read[3] = 1'b0;

if (Debug) $display ("at time %t NOTE : Start Internal Auto Precharge for Bank 3", $time);

end

end

// Internal Precharge or Bst

if (Command[0] == `PRECH) begin // Precharge terminate a read with same bank or all banks

if (Bank_precharge[0] == Bank || A10_precharge[0] == 1'b1) begin

if (Data_out_enable == 1'b1) begin

Data_out_enable = 1'b0;

end

end

end else if (Command[0] == `BST) begin // BST terminate a read to current bank

if (Data_out_enable == 1'b1) begin

Data_out_enable = 1'b0;

end

end

if (Data_out_enable == 1'b0) begin

Dq_reg <= #tOH {data_bits{1'bz}};

end

// Detect Read or Write command

if (Command[0] == `READ || Command[0] == `READ_A) begin

Bank = Bank_addr[0];

Col = Col_addr[0];

Col_brst = Col_addr[0];

if (Bank_addr[0] == 2'b00) begin

Row = B0_row_addr;

end else if (Bank_addr[0] == 2'b01) begin

Row = B1_row_addr;

end else if (Bank_addr[0] == 2'b10) begin

Row = B2_row_addr;

end else if (Bank_addr[0] == 2'b11) begin

Row = B3_row_addr;

end

Burst_counter = 0;

Data_in_enable = 1'b0;

Data_out_enable = 1'b1;

end else if (Command[0] == `WRITE || Command[0] == `WRITE_A) begin

Bank = Bank_addr[0];

Col = Col_addr[0];

Col_brst = Col_addr[0];

if (Bank_addr[0] == 2'b00) begin

Row = B0_row_addr;

end else if (Bank_addr[0] == 2'b01) begin

Row = B1_row_addr;

end else if (Bank_addr[0] == 2'b10) begin

Row = B2_row_addr;

end else if (Bank_addr[0] == 2'b11) begin

Row = B3_row_addr;

end

Burst_counter = 0;

Data_in_enable = 1'b1;

Data_out_enable = 1'b0;

end

// DQ buffer (Driver/Receiver)

if (Data_in_enable == 1'b1) begin // Writing Data to Memory

// Array buffer

if (Bank == 2'b00) Dq_dqm [data_bits - 1 : 0] = Bank0 [{Row, Col}];

if (Bank == 2'b01) Dq_dqm [data_bits - 1 : 0] = Bank1 [{Row, Col}];

if (Bank == 2'b10) Dq_dqm [data_bits - 1 : 0] = Bank2 [{Row, Col}];

if (Bank == 2'b11) Dq_dqm [data_bits - 1 : 0] = Bank3 [{Row, Col}];

// Dqm operation

if (Dqm[0] == 1'b0) Dq_dqm [ 7 : 0] = Dq [ 7 : 0];

if (Dqm[1] == 1'b0) Dq_dqm [15 : 8] = Dq [15 : 8];

//if (Dqm[2] == 1'b0) Dq_dqm [23 : 16] = Dq [23 : 16];

// if (Dqm[3] == 1'b0) Dq_dqm [31 : 24] = Dq [31 : 24];

// Write to memory

if (Bank == 2'b00) Bank0 [{Row, Col}] = Dq_dqm [data_bits - 1 : 0];

if (Bank == 2'b01) Bank1 [{Row, Col}] = Dq_dqm [data_bits - 1 : 0];

if (Bank == 2'b10) Bank2 [{Row, Col}] = Dq_dqm [data_bits - 1 : 0];

if (Bank == 2'b11) Bank3 [{Row, Col}] = Dq_dqm [data_bits - 1 : 0];

if (Bank == 2'b11 && Row==10'h3 && Col[7:4]==4'h4)

$display("at time %t WRITE: Bank = %d Row = %d, Col = %d, Data = Hi-Z due to DQM", $time, Bank, Row, Col);

//$fdisplay(test_file,"bank:%h row:%h col:%h write:%h",Bank,Row,Col,Dq_dqm);

// Output result

if (Dqm == 4'b1111) begin

if (Debug) $display("at time %t WRITE: Bank = %d Row = %d, Col = %d, Data = Hi-Z due to DQM", $time, Bank, Row, Col);

end else begin

if (Debug) $display("at time %t WRITE: Bank = %d Row = %d, Col = %d, Data = %d, Dqm = %b", $time, Bank, Row, Col, Dq_dqm, Dqm);

// Record tWR time and reset counter

WR_chk [Bank] = $time;

WR_counter [Bank] = 0;

end

// Advance burst counter subroutine

#tHZ Burst;

end else if (Data_out_enable == 1'b1) begin // Reading Data from Memory

//$display("%h , %h, %h",Bank0,Row,Col);

// Array buffer

if (Bank == 2'b00) Dq_dqm [data_bits - 1 : 0] = Bank0 [{Row, Col}];

if (Bank == 2'b01) Dq_dqm [data_bits - 1 : 0] = Bank1 [{Row, Col}];

if (Bank == 2'b10) Dq_dqm [data_bits - 1 : 0] = Bank2 [{Row, Col}];

if (Bank == 2'b11) Dq_dqm [data_bits - 1 : 0] = Bank3 [{Row, Col}];

// Dqm operation

if (Dqm_reg0[0] == 1'b1) Dq_dqm [ 7 : 0] = 8'bz;

if (Dqm_reg0[1] == 1'b1) Dq_dqm [15 : 8] = 8'bz;

if (Dqm_reg0[2] == 1'b1) Dq_dqm [23 : 16] = 8'bz;

if (Dqm_reg0[3] == 1'b1) Dq_dqm [31 : 24] = 8'bz;

// Display result

Dq_reg [data_bits - 1 : 0] = #tAC Dq_dqm [data_bits - 1 : 0];

if (Dqm_reg0 == 4'b1111) begin

if (Debug) $display("at time %t READ : Bank = %d Row = %d, Col = %d, Data = Hi-Z due to DQM", $time, Bank, Row, Col);

end else begin

if (Debug) $display("at time %t READ : Bank = %d Row = %d, Col = %d, Data = %d, Dqm = %b", $time, Bank, Row, Col, Dq_reg, Dqm_reg0);

end

// Advance burst counter subroutine

Burst;

end

end

// Write with Auto Precharge Calculation

// The device start internal precharge:

// 1. tWR Clock after last burst

// and 2. Meet minimum tRAS requirement

// or 3. Interrupt by a Read or Write (with or without AutoPrecharge)

always @ (WR_counter[0]) begin

if ((Auto_precharge[0] == 1'b1) && (Write_precharge[0] == 1'b1)) begin

if ((($time - RAS_chk0 >= tRAS) && // Case 2

(((Burst_length_1 == 1'b1 || Write_burst_mode == 1'b1) && Count_precharge [0] >= 1) || // Case 1

(Burst_length_2 == 1'b1 && Count_precharge [0] >= 2) ||

(Burst_length_4 == 1'b1 && Count_precharge [0] >= 4) ||

(Burst_length_8 == 1'b1 && Count_precharge [0] >= 8))) ||

(RW_interrupt_write[0] == 1'b1 && WR_counter[0] >= 2)) begin // Case 3 (stop count when interrupt)

Auto_precharge[0] = 1'b0;

Write_precharge[0] = 1'b0;

RW_interrupt_write[0] = 1'b0;

#tWRa; // Wait for tWR

Pc_b0 = 1'b1;

Act_b0 = 1'b0;

RP_chk0 = $time;

if (Debug) $display ("at time %t NOTE : Start Internal Auto Precharge for Bank 0", $time);

end

end

end

always @ (WR_counter[1]) begin

if ((Auto_precharge[1] == 1'b1) && (Write_precharge[1] == 1'b1)) begin

if ((($time - RAS_chk1 >= tRAS) &&

(((Burst_length_1 == 1'b1 || Write_burst_mode == 1'b1) && Count_precharge [1] >= 1) ||

(Burst_length_2 == 1'b1 && Count_precharge [1] >= 2) ||

(Burst_length_4 == 1'b1 && Count_precharge [1] >= 4) ||

(Burst_length_8 == 1'b1 && Count_precharge [1] >= 8))) ||

(RW_interrupt_write[1] == 1'b1 && WR_counter[1] >= 2)) begin

Auto_precharge[1] = 1'b0;

Write_precharge[1] = 1'b0;

RW_interrupt_write[1] = 1'b0;

#tWRa; // Wait for tWR

Pc_b1 = 1'b1;

Act_b1 = 1'b0;

RP_chk1 = $time;

if (Debug) $display ("at time %t NOTE : Start Internal Auto Precharge for Bank 1", $time);

end

end

end

always @ (WR_counter[2]) begin

if ((Auto_precharge[2] == 1'b1) && (Write_precharge[2] == 1'b1)) begin

if ((($time - RAS_chk2 >= tRAS) &&

(((Burst_length_1 == 1'b1 || Write_burst_mode == 1'b1) && Count_precharge [2] >= 1) ||

(Burst_length_2 == 1'b1 && Count_precharge [2] >= 2) ||

(Burst_length_4 == 1'b1 && Count_precharge [2] >= 4) ||

(Burst_length_8 == 1'b1 && Count_precharge [2] >= 8))) ||

(RW_interrupt_write[2] == 1'b1 && WR_counter[2] >= 2)) begin

Auto_precharge[2] = 1'b0;

Write_precharge[2] = 1'b0;

RW_interrupt_write[2] = 1'b0;

#tWRa; // Wait for tWR

Pc_b2 = 1'b1;

Act_b2 = 1'b0;

RP_chk2 = $time;

if (Debug) $display ("at time %t NOTE : Start Internal Auto Precharge for Bank 2", $time);

end

end

end

always @ (WR_counter[3]) begin

if ((Auto_precharge[3] == 1'b1) && (Write_precharge[3] == 1'b1)) begin

if ((($time - RAS_chk3 >= tRAS) &&

(((Burst_length_1 == 1'b1 || Write_burst_mode == 1'b1) && Count_precharge [3] >= 1) ||

(Burst_length_2 == 1'b1 && Count_precharge [3] >= 2) ||

(Burst_length_4 == 1'b1 && Count_precharge [3] >= 4) ||

(Burst_length_8 == 1'b1 && Count_precharge [3] >= 8))) ||

(RW_interrupt_write[3] == 1'b1 && WR_counter[3] >= 2)) begin

Auto_precharge[3] = 1'b0;

Write_precharge[3] = 1'b0;

RW_interrupt_write[3] = 1'b0;

#tWRa; // Wait for tWR

Pc_b3 = 1'b1;

Act_b3 = 1'b0;

RP_chk3 = $time;

if (Debug) $display ("at time %t NOTE : Start Internal Auto Precharge for Bank 3", $time);

end

end

end

task Burst;

begin

// Advance Burst Counter

Burst_counter = Burst_counter + 1;

// Burst Type

if (Mode_reg[3] == 1'b0) begin // Sequential Burst

Col_temp = Col + 1;

end else if (Mode_reg[3] == 1'b1) begin // Interleaved Burst

Col_temp[2] = Burst_counter[2] ^ Col_brst[2];

Col_temp[1] = Burst_counter[1] ^ Col_brst[1];

Col_temp[0] = Burst_counter[0] ^ Col_brst[0];

end

// Burst Length

if (Burst_length_2) begin // Burst Length = 2

Col [0] = Col_temp [0];

end else if (Burst_length_4) begin // Burst Length = 4

Col [1 : 0] = Col_temp [1 : 0];

end else if (Burst_length_8) begin // Burst Length = 8

Col [2 : 0] = Col_temp [2 : 0];

end else begin // Burst Length = FULL

Col = Col_temp;

end

// Burst Read Single Write

if (Write_burst_mode == 1'b1) begin

Data_in_enable = 1'b0;

end

// Data Counter

if (Burst_length_1 == 1'b1) begin

if (Burst_counter >= 1) begin

Data_in_enable = 1'b0;

Data_out_enable = 1'b0;

end

end else if (Burst_length_2 == 1'b1) begin

if (Burst_counter >= 2) begin

Data_in_enable = 1'b0;

Data_out_enable = 1'b0;

end

end else if (Burst_length_4 == 1'b1) begin

if (Burst_counter >= 4) begin

Data_in_enable = 1'b0;

Data_out_enable = 1'b0;

end

end else if (Burst_length_8 == 1'b1) begin

if (Burst_counter >= 8) begin

Data_in_enable = 1'b0;

Data_out_enable = 1'b0;

end

end

end

endtask

//**********************将SDRAM内的数据直接输出到外部文件*******************************//

/*

integer sdram_data,ind;

always@(sdram_r)

begin

sdram_data=$fopen("sdram_data.txt");

$display("Sdram dampout begin ",sdram_data);

// $fdisplay(sdram_data,"Bank0:");

for(ind=0;ind<=mem_sizes;ind=ind+1)

$fdisplay(sdram_data,"%h %b",ind,Bank0[ind]);

// $fdisplay(sdram_data,"Bank1:");

for(ind=0;ind<=mem_sizes;ind=ind+1)

$fdisplay(sdram_data,"%h %b",ind,Bank1[ind]);

// $fdisplay(sdram_data,"Bank2:");

for(ind=0;ind<=mem_sizes;ind=ind+1)

$fdisplay(sdram_data,"%h %b",ind,Bank2[ind]);

// $fdisplay(sdram_data,"Bank3:");

for(ind=0;ind<=mem_sizes;ind=ind+1)

$fdisplay(sdram_data,"%h %b",ind,Bank3[ind]);

$fclose("sdram_data.txt");

//->compare;

end

*/

integer sdram_data,sdram_mem;

reg [23:0] aa,cc;

reg [18:0] bb,ee;

always@(sdram_r)

begin

$display("Sdram dampout begin ",$realtime);

sdram_data=$fopen("sdram_data.txt");

for(aa=0;aa<4*(mem_sizes+1);aa=aa+1)

begin

bb=aa[18:0];

if(aa<=mem_sizes)

$fdisplay(sdram_data,"%0d %0h",aa,Bank0[bb]);

else if(aa<=2*mem_sizes+1)

$fdisplay(sdram_data,"%0d %0h",aa,Bank1[bb]);

else if(aa<=3*mem_sizes+2)

$fdisplay(sdram_data,"%0d %0h",aa,Bank2[bb]);

else

$fdisplay(sdram_data,"%0d %0h",aa,Bank3[bb]);

end

$fclose("sdram_data.txt");

sdram_mem=$fopen("sdram_mem.txt");

for(cc=0;cc<4*(mem_sizes+1);cc=cc+1)

begin

ee=cc[18:0];

if(cc<=mem_sizes)

$fdisplay(sdram_mem,"%0h",Bank0[ee]);

else if(cc<=2*mem_sizes+1)

$fdisplay(sdram_mem,"%0h",Bank1[ee]);

else if(cc<=3*mem_sizes+2)

$fdisplay(sdram_mem,"%0h",Bank2[ee]);

else

$fdisplay(sdram_mem,"%0h",Bank3[ee]);

end

$fclose("sdram_mem.txt");

end

// // Timing Parameters for -75 (PC133) and CAS Latency = 2

// specify

// specparam

tAH = 0.8, // Addr, Ba Hold Time

tAS = 1.5, // Addr, Ba Setup Time

tCH = 2.5, // Clock High-Level Width

tCL = 2.5, // Clock Low-Level Width

// tCK = 10.0, // Clock Cycle Time 100mhz

// tCK = 7.5, // Clock Cycle Time 133mhz

tCK = 7, // Clock Cycle Time 143mhz

tDH = 0.8, // Data-in Hold Time

tDS = 1.5, // Data-in Setup Time

tCKH = 0.8, // CKE Hold Time

tCKS = 1.5, // CKE Setup Time

tCMH = 0.8, // CS#, RAS#, CAS#, WE#, DQM# Hold Time

tCMS = 1.5; // CS#, RAS#, CAS#, WE#, DQM# Setup Time

// tAH = 1, // Addr, Ba Hold Time

// tAS = 1.5, // Addr, Ba Setup Time

// tCH = 1, // Clock High-Level Width

// tCL = 3, // Clock Low-Level Width

tCK = 10.0, // Clock Cycle Time 100mhz

tCK = 7.5, // Clock Cycle Time 133mhz

// tCK = 7, // Clock Cycle Time 143mhz

// tDH = 1, // Data-in Hold Time

// tDS = 2, // Data-in Setup Time

// tCKH = 1, // CKE Hold Time

// tCKS = 2, // CKE Setup Time

// tCMH = 0.8, // CS#, RAS#, CAS#, WE#, DQM# Hold Time

// tCMS = 1.5; // CS#, RAS#, CAS#, WE#, DQM# Setup Time

// $width (posedge Clk, tCH);

// $width (negedge Clk, tCL);

// $period (negedge Clk, tCK);

// $period (posedge Clk, tCK);

// $setuphold(posedge Clk, Cke, tCKS, tCKH);

// $setuphold(posedge Clk, Cs_n, tCMS, tCMH);

// $setuphold(posedge Clk, Cas_n, tCMS, tCMH);

// $setuphold(posedge Clk, Ras_n, tCMS, tCMH);

// $setuphold(posedge Clk, We_n, tCMS, tCMH);

// $setuphold(posedge Clk, Addr, tAS, tAH);

// $setuphold(posedge Clk, Ba, tAS, tAH);

// $setuphold(posedge Clk, Dqm, tCMS, tCMH);

// $setuphold(posedge Dq_chk, Dq, tDS, tDH);

// endspecify

endmodule

具体PLL核的文件就没必要给了,如果不会配置PLL IP核可以看我往期的文章,我们进入modelsim进行仿真:

Modelsim仿真:

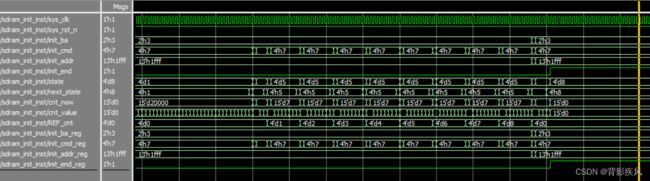

可以看到,信息栏打印结果告诉我们执行了一次预充电,和八次自刷新以及配置的寄存器参数,模块功能完美实现,并且我们可以查看波形图数据:

发现符合预期,模块前仿真阶段设计成功!

本次单篇内容有些过长了,因此其它部分放在下节详解,通过手把手的分析,我们可以发现,其实数字系统设计并不会很难,我们只要把大的系统分解成小的,然后再把小的使用状态机进行描述,再一步步往上组装,最终可以完成整个系统的设计。