1.VHDL的基础知识

目录

1.VHDL语言基础

1.1.标识符 (Identifiers)

关键字(保留 字):

1.2.数据对象(Date Objects)

常量 Constant

变量Variable

信号Signal

1.3.数据类型

VHDL的预定义数据类型

IEEE预定义标准逻辑位与矢量

用户自定义

1.4数据类型转换

属性

运算符

运算符的优先级

1.VHDL语言基础

VHDL 概 概 述:

- VHDL VHSIC Hardwarter Description Language

- Very High speed integrated circuit

- VHDL 是美国国防部在20世 世纪 纪80 年代初 为实现 其高速集 成电路硬件VHSIC计 计 划 提 出 的描述语言;

- IEEE 从1986 年开始致力于 于VHDL 标准化 工 作 , 融 合 了其它ASIC 芯片制造 商开发 的 硬件 描述语言的优点,于93 年形成 了标准版 本( (IEEE.std_1164) ) 。

- 1995年 , 我 国国家技术监督局推荐VHDL做 做 为电 子 设计 自动化硬件 描述语言的国家标准。

VHDL的优点:

- 覆盖面广,系统硬件描述能 力强 ,是一 个多层次的硬 描述语言;

- VHDL 语言 具 有 良好 的可 读性 , 既 可以 被 计算机 接受 , 也容易被人们所理解;

- VHDL 语言可以 与 工艺 无关 编程;

- VHDL 语言 已做 为一种IEEE 的工 业标准 , 便 于 使 用、交流 和 推广 。

1.1.标识符 (Identifiers)

标 识符用来定义常数、 变量 、 信号 、 端口 、 子程序或参数的名字,由字母 母(A~Z,a~z) 、数字(0~9)和下划线 线(_)字符组成。

要求 :

- 首字符必须是字母

- 末字符不能为下 划 线

- 不允许出现两个连续的下划线

- 不区分大小写

- VHDL定义的保留字(关键字),不能用作标识符

- 标识符字符 最长可以是可以是32个字 符 。

注意:注释由两个连续的虚线( -- )引 导

关键字(保留 字):

关键字((keyword))是 是VHDL中具有特别含义的单词 , 只能做为固定的用途 ,用户不能用其做为标识符。

如: ABS, ACCESS , AFTER , ALL , AND , ARCHITECTURE, ARRAY , ATTRIBUTE , BEGIN, BODY , BUFFER , BUS , CASE , COMPONENT , CONSTANT , DISCONNECT , DOWNTO , ELSE, ,ELSIF , END , ENTITY , EXIT , FILE , FOR , FUNCTION, GENERIC , GROUP , IF , INPURE , IN ,INOUT , IS , LABEL, LIBRARY , LINKAGE , LOOP , MAP , MOD , NAND , NEW , NEXT, ,NOR , NOT , NULL , OF , ON , OPEN , OR , OTHERS , OUT, PACKAGE , , POUT , , PROCEDURE , PROCESS , PURE , RANGE , RECODE , REM , REPORT , RETURN , ROL , ROR , SELECT, SHARED , SIGNAL , SLA , SLL , SRA , SUBTYPE , THEN, TRANSPORT , TO , , TYPE , UNAFFECTED , UNITS , UNTIL , USE, VARIABLE , WAIT , WHEN , WHILE , WITH ,XOR , XNOR。

1.2.数据对象(Date Objects)

数据对象包括常量 、变量 、信号和文件四种类型 。

-

常量 Constant

常量是对某一常量名赋予一个固定的值 ,而且只能赋值一次 。通常赋值在程序开始前进行, 该值的数据类型则在说明语句中指明。

Constant 常数名 :数 据 类 型 : =表达式

例子:

Constant Vcc :real:=5.0; -- 定义Vcc的数据类型是实数, 赋值为为5.0V

Constant bus_width: integer := 8; --定义总线宽度为常数8

注意事项:

- 常量所赋的值应和定义的数据类型一致 ;

- 常量在程序包 、实体 、构造体或进程的说明性区域内必须加以说明 。 定义在程序包内的常量可供所含的任何实体 、构造体所引用, 定义在实体说明内的常量只能在该实体内可见 , 定义在进程说明性区域中的常 量只能在该进程内可见。

-

变量Variable

变量只能在进程语句、函数语句和过程语句结构中使用。 变量的赋值是直接的,非预设的, 分配给变量的值立即成为当前值 , 变量不能 表达“ 连线” 或 存储元件 ,不能设置传输延迟量。

变量定义语句:

Variable 变量名 : 数据类型 := 初始值

例子:

Variable count: integer 0 to 255:=20;

解释:定义count整数变量 , 变化范围0 ~255, 初始值为20。

变量赋值语句:

目标变量名 := 表达式;

例子:

x:=10.0; -- 实数变量赋值为10.0

Y:=1.5+x; -- 运算表达式赋值 , 注意表达式必须与目标变量的数据类型相 同

A(3 to 6):=(“1101”); -- 位矢量赋值

-

信号Signal

信号表示逻辑门的输入或输 出 ,类似于连接线, 也可以表达存储元件的状态。 信号通常在构造体 、程序包和实体中。

信号定义语句:

Signal 信号名: 数据类型 := 初始值

例子:

Signal clock :bit := ‘0 ’; -- 定义时钟信号类型 ,初始值为0

Signal count :BIT_VECTOR(3 DOWNTO 0); -- 定义count 为4位矢量

信号赋值语句:

目标信号名 <= 表达式;

例子:

x<=9;

Z<=x after 5 ns; -- 在5ns 后将x的值赋予z

1.3.数据类型

-

VHDL的预定义数据类型

在 VHDL标准程序包STANDARD中定义好 ,实际使用过程中, 已自动包含进VHDL源文件中,不需要通过USE语句显式调用。

- 布尔:(Boolean)

TYPE BOOLEAN IS (FALSE, TRUE); -- 取值为FALSE 和TRUE,不是数,不是数值 ,不能运 算,一 般用于关系运算。

- 位 : ( Bit )

TYPE BIT IS (‘0’,’1’); -- 取值为0 和1,用于逻辑运算。

- 位矢量 : ( Bit_Vector )

TYPE BIT_VECTOR IS ARRAY (Natural range<>) OF BIT; -- 基于Bit类型的数组 ,用于逻辑运算。

例子:

SIGNAL a :Bit_Vector(0 TO 7);

SIGNAL a :Bit_Vector ( 7 DOWNTO 0);

- 字符:(Character)

TYPE CHARACTER IS (NUL, SOH,STX, …, ‘ ’, ‘!’,…); --通常用‘’ 引起来 , 区分大小写。

- 字符串 :(String)

VARIABLE string_var: STRING (1 TO 7);

string_var:=“A B C D” ; -- 通常用“” 引起来 , 区分大小写;

- 整数:(Integer)

取值范围 -(2^31 -1) ~ (2^31 - 1) ,可用32位有符号的二进制数表示。

例子:

variable a :integer range -63 to 63

注意:

- 在实际应用中,VHDL仿真器将Integer做为有符号数处理 , 而VHDL综合器将Integer做为无符号数处理。

- 要求用RANGE子句为所定义的数限定范围 ,以便根据范围来决定表示此信号或变量的二进制数的位数。

- 实数:(Real)

取值范围值范围 -1.0E38 ~ +1.0E38, , 仅用于仿真不可综合。

例子:

1.0 --十 十 进制 浮 点数

8 #43.6 #e+4 --八 八 进制 浮 点数

43.6E-4 --十 十 进制 浮 点数

- 时间: (Time)

物理量数据 ,完整的包括整数和单位两个部分 ,用至少一个空格隔开 , 仅用于仿真不可综合 ;

单位:fs,ps,ns,us,ms,sec,min,hr

- 错误等级 ( (Severity Level) )

表示系统状态, 仅用于仿真不可综合 ;

例子:

TYPE severity_level IS (NOTE 、WARNING 、ERROR 、FAILURE);

-

IEEE预定义标准逻辑位与矢量

- 标准逻辑位( Std_Logic)

| U | Uninitialized (未初始化的) |

X | Forcing Unkown (强制未知的) |

0 | Forcing 0 (强逻辑0) |

| 1 | Forcing 1 (强逻辑1) |

Z | High Impedance (高阻态) |

W | Weak Unknow (弱未知的) |

| L | Weak 0 (弱逻辑0) |

H | Weak 1 (弱逻辑1) |

— | Don’t care (忽略) |

- 标准逻辑位矢量 ( Std_Logic_vector )

使用 Std_Logic和 Std_Logic_Vector要 调用IEEE库中的Std_Logic_1164程序包; 就综合而言,能够在数字器件中实现的是“ -、 0 、1 、Z”四种状态。

-

用户自定义

方法一:

TYPE 数据类型名 IS 数据类型定义 OF 基本数据类型 或

TYPE 数据类型名 IS 数据类型定义

例子:

数 组: type value_type is array (127 downto 0) of integer;

type matrix_type is array (0 to 15, 0 to 31) of std_logic;枚举: type states is (idle ,decision ,read ,write);

type boolean is (false ,true);

type bit is (‘0’ ,‘1’);

方法二:

SUBTYPE 子类型名 IS 基本数据类型定义 RANGE 约束

例子:

subtype digit is integer range 0 to 9;

1.4数据类型转换

VHDL为强定义类型语言,不同类型的数据不能进行运算和直接赋值 。

- 类型标记法

Variable A: integer; Variable B: real;

A= integer (B); B=real (A);

- 函数法

Conv_interger (A) ;-- 由std_logic转换为integer型,在std_logic_unsigned包。

- 常数转换法 / 常量转换法

Type conv_table is array(std_logic) of bit;

Constant table: conv_table:=(‘0’|’L’=>’0’, ‘1’|’H’=>’1’, others=>’0’);

Signal a: bit; signal b: std_logic;

A<=table(b); -- 将std_logic型 型 转换为 为bit型

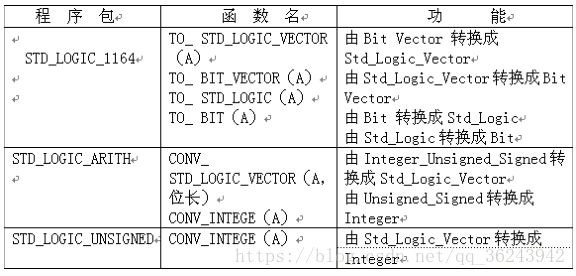

在“STD_LOGIC_1164” 、“STD_LOGIC_ARITH”和 “STD_LOGIC_UNSIGNED” 的程序包中提供的数据类型变换函数。

-

属性

属 性提供的是关于信号 、类型等的指定特性 。

‘event : 若属性对象有事件发生,则生成布尔值“true”,常用来检查时钟边沿是否有效。

上升沿: Clock’ EVENT AND Clock=‘1’

’range : 生成一个限制性数组对象的范围

’left : 生成数 据 类 型 或数 据 子 类 型 的 左边界 值;

’right , ’high, ’low, ’length

’range: “0 to n” ; ’reverse_range :“n downto 0”

-

运算符

- 算术运算符 : +, -, *, / , MOD, REM ,SLL ,SRL ,SLA, SRA ,ROL ,ROR ,** ,ABS

- 关系运算符 : =, /= , <, > , <=, >=

- 逻辑运算符: AND ,OR ,NAND ,NOR ,XNOR ,NOT ,XOR

- 赋值运算符: <= ,:=

- 关联运算符: =>

- 其他运算符 : +, -,&

并置操作符 &

SIGNAL a : STD_LOGIC_VECTOR (3 DOWNTO 0) ;

SIGNAL d : STD_LOGIC_VECTOR (1 DOWNTO 0) ;

...

a <= '1'&'0'&d(1)&'1' ; -- 元素与元素并置 , 并置后的数组长度为为4

...

IF a & d = "101011" THEN ... –- 在IF条 条 件 句中可以使用并置符

-

运算符的优先级

优先级从到高,如下所示:

逻辑 、算术运算符 : NOT, ** ,ABS

乘法运算符 : / , MOD, REM, *

正负运算符 : +, -

加减、 并置运算 符 : +, -, &

关系运算符 : =, /= , <, > , <=, >=

逻辑运算符 :AND ,OR ,NAND ,NOR ,XNOR ,NOT ,XOR

注意事项:

1.移位运算符的左边为一维数组 , 其类型必须是BIT或BOOLEAN, 右边必须是整数移位次数为整数的绝对值,

- SLL: : 将位向量左移 , 右边移空位补零 ;

- SRL: : 将位向量右移 , 左边移空位补零 ;

- SLA: : 将位向量左移 , 右边第一位的数值保持原值不 变;

- SRA: : 将位向量右移 , 左边第一位的数值保持原值不变;

- ROL 和ROR: 自循环左右移位

例子:

“1100”SLL1 =“1000” “1100”SRL1 =“0110” “1100”SLA1 =“1000”

“1100”SRA1 =“1110” “1100”ROL1 =“1001” “1100”ROR1 =“0110

2.取余运算(a REM b) 的符号与a相同, 其绝对值小于b的绝对值

例子:

(-5 )REM 2= (-1) 5 REM 2= (1)

3.取模运算(a MOD b) 的符号与b相同, 其绝对值小于b的绝对值

例子:

(-5 )MOD 2=1 5 MOD (- 2)= (-1)