逃离x86架构-----CPU体系结构CISC与RISC之争

x86架构诞生

Intel 8086是一个由Intel于1978年所设计的16位微处理器芯片,是x86架构的鼻祖。不久,Intel 8088就推出了,拥有一个外部的8位数据总线,允许便宜的芯片用途。

早在1981年,IBM公司推出了基于Intel 8088处理器的个人电脑(PC);和8086处理器相比,它是一台低价格,低性能的处理器。尽管在当时Motorola MC69000处理器的性能也相当不错,但是IBM这样选择的理由是因为8088处理器已经能够对地址总线进行“复用”,并且总线宽度达到8位,和以往相比,大大减少了整个系统的开销。由于当时没有芯片组这一概念,因此数据和指令的存储和读取都要依靠主板上的特殊门电路,这些部件也是8位的宽度。如果使用Mortola MC69000处理器的话,那么在相同功能的情况下,主板需要更多的此类部件,因此大大增加了主板的制造成本。尽管有人建议,Mortola MC69000有助于系统性能的提高,但是IBM固守“简单就是美”的原则,毅然选择了8088处理器。

IBM的“生死抉择”却给软件开发者带来灾难性的影响(当时没有充分意识到)。由于处理器采用了808X的架构,因此数据和代码只能在64KB的范围内进行访问。如果某一个程序需要使用超过64KB的内存,那么程序不得不使用16位的段地址和16位的偏移地址组合,来达到20位的数据访问范围。当时的程序员就为16位到20位的地址转化伤透了脑筋。在程序的编译过程中,也引进了相应的内存使用模式(小型,中型,大型,巨型)。系统集成的汇编语言在程序编写时,必须指明是近程调用(near call)还是远程调用(far call)。如果要把8088处理器的程序移植到如MC68000机时,就必须把地址扩展成32位,这个过程非常繁琐。

尽管64KB的限制是IBM个人电脑的一个死穴,但是当时IBM PC的市场销售额非常不错。8088处理器和DOS操作系统能够支持大部分的应用软件,因此IBM的个人电脑推出不久就受到各界的好评;而对于64KB的限制,人们似乎没有太多的关注。随着PC的成功推出,IBM着手于X86系统架构标准的制定,并且希望成为全球最大的电脑制造商。Intel和Microsft都参与了此标准的定制,并且携手进行个人电脑的开发。

第一个x86架构的“婴儿”便是于1985年推出的32位的80386处理器(386处理器)。当时,大部分的操作系统(或者准操作系统)还是16位模式,因此程序员也必须进行地址的转化,这个令人厌烦的转化工作直到Microsoft公司发布了第一款32位的操作系统Windows 95时,才得以解决。Windows 95是第一款使用32位地址的操作系统,它能够对32位空间的数据进行读写操作,并且80386处理器的内部有7个通用寄存器(GPRS)。

从19世纪80年代开始,X86架构快速的发展着。同时,RISC(精简指令集)架构也受到人们的关注,并且有不少成功的产品,如SPARC ,PA-RISC,MIPS等。从价格上而言,X86架构的PC机最便宜;而那些基于RISC处理器的大型机价格昂贵。但是在架构上,PC机和大型机有非常多的相同点,它们都有着良好的软件支持,并且集成汇编语言。

它们之间第二个相似点就是PC和大型机的档次通常用以整体的性价比来决定,而不是只决定于CPU的处理能力。可靠性,可用性,和功能性是用于衡量机器性能的主要标准。PC机和大型机的定位也相当的明确,在1980年,一台PC机的价格只要几百美元,而大型机的架构至少要上千美元;在功能上,PC机定位于整数的运算,而大型机却是以浮点数的运算来衡量性能的高低。

尽管PC机和RISC大型机在价格和功能上定位不同,但是在1990年初,Sun Microsystems公司推出了桌面的微型RISC系统“MicroSPARC”。为了能够稳固自身的地位,针对Sun公司这个行为,Intel公司不久后就推出了性能和MicroSPARC相当的Pentium Pro处理器,Pentium Pro处理器是X86架构发展过程中的一个里程碑。

Pentium Pro 处理器首先在x86体系中引入了“微指令”的概念,即一条指令能够完成原先几条指令的操作。在256KB二级缓存的协助下,微指令使得系统的整体性能有了突破性的飞跃。当时由0.35微米制成技术制造的Pentium Pro处理器可以和原先任何一款RISC处理器叫板。在当时,Pentium Pro的惊人性能在PC的制造界产生了巨大的影响,那些原先RISC的支持者不得不重新审视起x86架构来。尽管x86架构存在GPRS数量过少,串行的通讯指令过于复杂,内存操作不便等缺点,但是RISC的开发者们不得不承认,当时的RISC架构达不到Pentium Pro的性能。

揭开X86的真像

随着经济的不断发展,x86处理器的应用范围越来越广,但是人们似乎渐渐忘却x86架构的不足。在x86架构的发展过程中,它微处理器(MPU)或多或少的占据着领先的地位。为了保持领先,个人电脑的发展似乎脱离了IBM原先“简单就是美”的初衷。CPU的制成技术快速的发展着,集成的晶体管数量也基本按照莫尔定律增加。当CPU集成的晶体管数量超过1百万后,“制成工艺”和“晶体管集成度”成为衡量系统性能的另一个标准。

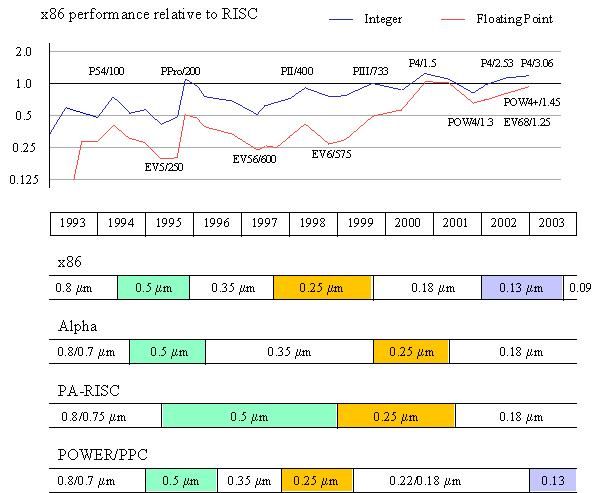

同时,基于RISC处理器的大型机也不懈的发展着,尽管在制成技术上不及X86架构,但是它的整数和浮点数性能要高于X86架构。以下是1993年至今,x86性能和RISC的比值。

图 x86/RISC 性能比 vs制成工艺

上图分为两个部分,上半部分是x86/RISC的性能比。可以看出,在整体上,RISC的性能要高于x86(x86/RISC<1),但是它们之间的差距正在逐渐减少。其中Pentium Pro ,P4/1.5 ,P4/3.06这几款CPU的性能已经超过了同期RISC处理器的性能。图的下半部分是x86和RISC制成工艺的对比。

Pentium Pro推出时,x86架构系统和RISC处理器系统的分工就相当的明确。

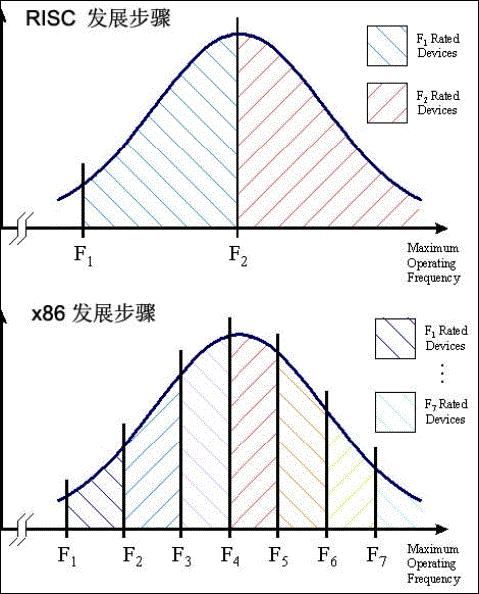

RISC系统针对高端的服务器市场,CPU和所有的部件都必须确保系统的“稳定性”,即使降低10%的性能也要尽可能的提高系统的稳定性。因此RISC 处理器必须经过详细,严谨的设计,并且需要通过一系列严格的测试。因此大型机的CPU非常昂贵,每一代的CPU一般只推出2~3种不同频率的产品,因为企业不可能在系统升级上不断的投入昂贵的费用。

相比之下x86架构系统主要针对个人用户和小型的商用系统。和RISC相比,x86的价格要低1~2个数量级,它主要是确保系统的性能,或者尽可能的提高系统的性价比。因此针对同一代的CPU,它会推出7~8种不同频率的产品。例如Intel Northwood Pentium 4的整个推出的过程中,一共发布了7种不同频率的产品。

图 产品推出力度对比

上图清楚的表明,在同一代产品中,RISC系统一般只会推出2-3种产品,而X86架构会有7-8种的产品。因此后者的粒度要比前者细的多。这也说明RISC系统的CPU一旦设计定型,就会进行制造和测试,在产品最后发布之前,尽可能的改正设计中的错误,因为RISC昂贵的价格决定一旦CPU的设计存在问题,那么这就是一款失败的产品,在市场上就不会有立足之地。而x86的CPU价格较低,因此它不断推出的产品能够弥补以往设计中的不足,不同产品在于占领不同的市场。

X86=永恒?

随着X86架构的不断成熟,人们逐步开始认识到其本身的限制和不足(例如32位的X86架构的寻址空间只有4GB),但是巨大的商业利益和强劲的软硬件的支持,使得x86的架构难以动摇。尽管在x86的发展历程中,也有不少的体系设计用于代替x86架构,但是它们都因为得不到广泛的支持,最终以失败告终。其中,影响较大的是以下3次“x86革命”。

第一次革命:MIPS/ACE 联盟

1991年4月,Compaq, Microsoft, DEC, MIPS和一些小型的计算机公司成立了高级计算环境(ACE)小组,他们的目的在于使用基于RISC处理器的MIPS架构来取来现有的x86/IBM个人电脑。 但是由于MPU上市日期的延迟,ACE小组的内部竞争,以及利益分成的问题,使得ACE小组的发展举步为艰,最后以失败而告终。

第二次革命:Apple/IBM/Motorola (AIM) 联盟

同样在1994年4月底,Apple Computer, IBM 和 Motorola组成了AIM联盟,目的在于把RISC处理器用于个人电脑系统。Motorola 和IBM联手对POWER架构进行重新设计,用于取代原先Macintosh系统中逐渐衰落的680X0 CISC处理器。POWER架构给Mac系统带来了巨大的成功,它的性能要比原先的Mac大大提高。但是x86架构的发展始终要快于PowerPC ,而且PowerPC没有任何的性价比优势,因此不多久,Mac机就在x86架构面前败下阵来。在Intel和Microsoft巨大的压力下,1994年8.3%的市场占有率也紧缩到目前的3%。

第三次革命:DEC/Samsung

1996年年底, DEC的芯片制造部门(原先的Digital Semiconductor公司)发布布了21164PC。它是原先高性能处理器21164A(EV56)的PC版,因此价格较低,并且使用了微软的Windows NT操作系统。由于缺少相应的软件支持,DEC开发了FX!32模拟器,它能够把原先X86的软件无缝的应用到21164PC平台。尽管CPU的价格低廉,但是支持21164PC的主板却非常昂贵。而且在当时,人们对NT操作系统并没有表现出多大的兴趣,因此21164PC慢慢的在X86架构发展中退出了历史舞台。

上述例子中的MPU制造商失败的主要原因就是跟不上Intel CPU的发展速度。Intel不断进行着新型的CPU设计,并且以价格来争取市场;上述的三种新型CPU架构都是被Intel强大的马力所拖垮。其中,MIPS/ACE 联盟主要是资金的问题,而AIM联盟的失败归咎于CPU的设计跟不上Intel的发展速度。

Intel的自我革命

目前的事实告诉我们,当今几乎不可能有其他的MPU制造商使用其他的系统结构,来挑战Intel 现下兼容的X86平台;其他的芯片制造商也没有雄厚的资金和实力来和Intel公司进行抗衡。人们考虑:是否Intel公司自己会提出一种全新的架构;或者Intel是否会脱离IBM的x86标准来发展自身的Wintel体系架构(Wintel:Windows操作系统和Intel处理器)。近几年,Intel致力研究的Itanium(安腾)处理器(IPF Itanium Processor Family)似乎有取代x86的趋势。Intel也宣布,Itanium会首先使用在服务器上,然后过渡到PC平台,最终在移动平台上实现。

安腾处理器是构建在IA-64(Intel Architecture 64) Itanium是英特尔最初的基于64-位体系的微处理器。Intel 的IPF主要针对RISC处理器原先占有的中高端服务器市场。Intel推出64位的处理器只是一个时间的问题,可能在目前而言,还为时过早;但是Intel的竞争对手AMD公司已经在今年推出了x86架构的扩展―――64的处理器和系统平台。AMD 64位的架构并不是全新的架构,而是对原先32位的x86架构进行扩展,突破了4GB寻址空间的限制;但是64位的计算环境却在业界产生了巨大的影响,它成为Intel IPF技术的挑战者。姑且不论AMD 64位架构推出时机是否合适,但是业界普遍认为64位的架构会在5年内成为主流的桌面PC架构,同时AMD的这一举措也加快了IPF处理器的推出。

IPF技术是由Intel和惠普联合研制,取得了一定的成绩。但是目前的IPF处理器核心尺寸,电源功耗都决定了其不能使用在桌面系统上。IPF采用0.18微米的制成工艺,和Alpha EV(397mm2,125W),POWER4(415 mm2,115W)相比,Itanium 2处理器的尺寸为421 mm2,电源功耗高达130W。

在随后的,代号为Madison/Deerfield的Intanium 2处理器中,Intel使用了0.13微米的制成工艺。1.3GHz的Itanium 2处理器的最大发热量和2.66GHz Northwood Pentium 4相当。和2.66GHz Pentium 4相比,1.3GHz Itanium2的整数运算性能有了10%的提高,浮点数性能有了50%的提高。在高级的优化技术下,IPF的性能要比原先同等频率的处理器高出整整一倍,而且随着IPF技术的成熟,这种差距会愈加扩大。

尽管在硬件的技术上,AMD和Intel都已经相当成熟;但是AMD 64位的系统和Intel的IPF都不得不面临一个相同的问题:缺少软件的支持。目前支持AMD 64位系统和IPF技术的只有Window最新的操作系统。AMD公司和Intel公司对于64位架构的研发上都或多或少面临“鸡生蛋,还是蛋生鸡”的尴尬局面。64位的架构必须有软件的支持才能发挥应有的功效,同样软件只有凭借64位的架构才能进行开发。业界人员保守的估计,64位的软件至少要3-5年才能普及起来。

对于IPF处理器而言,它和原先x86架构下的处理器有什么本质的不同呢?如果不考虑AMD的64位扩展x86架构,在相同的电源功耗,相同的费用,相同的制成工艺下,IPF处理器在整数运算上的性能会高出20%-30%,浮点数和DSP的运算性能会有50%的提高。

结论:革命尚未成功,同志仍需努力

“说要比做的容易。”随着IPF技术的成熟,32位x86架构缺陷的不断出现,IPF取代x86架构势在必行。但是一旦真正的进行“改革”。IPF(或者其他架构)必定会受到来自各方面的压力和阻碍。乐观的估计,IPF取代x86成为主流的架构至少要在2005年以后。如果考虑到来自AMD 64位的x86的架构阻挠,那么整个改革的之间会更长,甚至有失败的可能。

我们深知,每一项新技术的应用,都会伴随着出生时的阵痛;但是对于未来却是一片光明。Intel的IPF如此,AMD的64位架构也是如此。在PC发展历程中,正是这些一次又一次的阵痛,不断推动着整个IT界发展,使IT界保持旺盛的发展力。也许这些阵痛可能会带来难产,使得婴儿死于襁褓之中;但是每一次成功的诞生,都会给IT界带来一个全新的世界。不管X86架构未来如何,我们都期待着会有一个崭新的明天。

CPU体系结构CISC与RISC之争

(转自pcpro.com.cn)

在PC发展之初,除了成熟的CISC指令架构外,IBM没有更好的选择,原因很简单,更先进的RISC架构在1975年才出现,且只针对超级计算机领域,当时没有人意识到PC会有如此之大的发展,只是将它作为计算产品的一种补充而已。为图省事,IBM干脆就选择了Intel作为微处理器芯片的合作伙伴,而Intel所创立的X86指令系统便属于CISC架构。

我们有必要对指令架构、CISC、RISC之类的概念作明晰的解释。众所周知,微处理器的基本逻辑是运行指令的电路,计算机的任何一个程序都是由或多或少的基本指令组成,而指令本身又是由若干个微操作构成,例如对两个二进制数进行加减运算,或者将结果送进寄存器中等等。了解汇编语言或机器语言的读者对此应该比较清楚。这些基本指令被称为微处理器的微代码(Microcode),指令数量越多、完成微操作所需的逻辑电路就越多,芯片的结构就越复杂。每个处理器开发商都可以自己定义出一套指令系统,但如果指令系统不相同,构成软件的指令也不相同,这样就无法实现软件兼容。在专用计算机时代,这种情况十分普遍,各个计算机厂商都独立发展指令系统、微处理器、计算整机和软件,不同厂商的软硬件产品无法兼容使用,其原因就在于微处理器的指令系统采用不同的定义。然而,尽管当时指令系统种类甚多,它们却都归属于CISC架构—CISC的英文全称是Complex Instruction Set Computer,意为“复杂指令系统计算机”。它的特点是指令数量庞大臃肿,每个指令不管执行频度高低都处于同一个优先级,程序员的编程工作相对容易。但它的致命弊端是执行效率低下,处理器的晶体管被大量低效的指令所占据,资源利用率颇为低下。当IBM成功发展出RISC系统之后,CISC迅速被超级计算机所抛弃。但机缘巧合,它却在PC上获得新生,为了保持软件兼容,PC必须一直延续X86架构无法脱离(IBM将标准制定权让给Intel,最终葬送了自己在PC领域的前途)。后来加入微处理器战团的Cyrix、Rise、AMD、IDT等厂商无一不是如此,PC朝着X86道路渐行渐远,从8位、16 位、32位一直扩展到现在的64位,虽然它依然有旺盛的生命力,但背后的一系列缺陷也逐渐显现:芯片设计臃肿不堪,能源利用率低下,性能与晶体管规模相当的RISC产品根本不在一个水平线上。

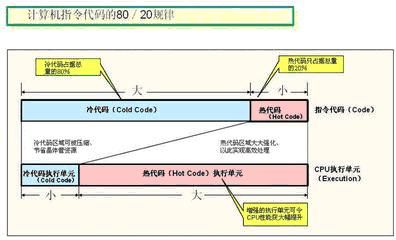

图1依据80/20法则划分的“冷代码”与“热代码”概念——前者占据X86指令总量的80%,后者只占据20%。与之相应,冷代码执行单元占据绝大多数硬件资源,而高度活跃的热代码执行单元所占据的硬件资源反而要少得多。PARROT优化之后,热代码执行单元被大大加强,冷代码单元则被相应缩减,在晶体管规模不变的前提下实现性能的跨越式提升。

相比之下,RISC(全称Reduced Instruction Set Computer,精简指令系统计算机)则是一套优化过的指令架构,它是根据著名的80/20法则所订立。早在上个世纪60年代,计算机科学家们发现,计算机中80%的任务只是动用了大约20%的指令,而剩下20%的任务才有机会使用到其他80%的指令。如果对指令系统作相应的优化,就可以从根本上快速提高处理器的执行效率。IBM公司在1975年成功开发出第一款RISC处理器,从此RISC架构开始走进超级计算机中。由于指令高度简约,RISC处理器的晶体管规模普遍都很小而性能强大,深受超级计算机厂商所青睐。很快,许多厂商都拿出自己的RISC指令系统,除了IBM的Power和PowerPC 外,还有DEC的Alpha、SUN的SPARC、HP的PA-RISC、MIPS技术公司的MIPS、ARM公司的ARM等等。它的应用范围也远比 X86来得广泛,大到各种超级计算机、工作站、高阶服务器,小到各类嵌入式设备、家用游戏机、消费电子产品、工业控制计算机,都可以看到RISC的身影。只不过这些领域同普通消费者较为脱离,故而少为人知。

无论在执行效率、芯片功耗还是制造成本上,选择RISC都比沿用X86更加英明。我们不妨作一番实际的比较:目前Intel公司最快的处理器是 Prescott核心的Pentium 4 XE系列,它的晶体管总数在1亿7800万个以上,最高功耗达到130W,但它的运算能力不超过20GigaFlops(FLoating point Operations per Second,每秒浮点运算)。而目前最快的RISC处理器是IBM推出的Cell,它的晶体管总数为2.34亿个,在采用90纳米工艺制造时芯片面积为221平方毫米,但它的运算力高达2560GigaFlops,整整是Pentium 4 XE的128倍。Intel将在年中推出双核心的Smithfield,性能最多能有80%的提升,而芯片规模将达到与Cell相同的水平。由此可见,二者完全不是一个层面上的对手,X86指令系统的低效性在这里一览无遗。与此对应,RISC产品在成本上优势明显—半导体芯片的制造成本同芯片面积三次方成正比。在工艺相同的情况下,芯片面积大小取决于所集成的晶体管规模。RISC处理器核心精简、效率更高,只要很少的晶体管就能达到与X86产品媲美的效能,制造成本可大大低于现有的X86处理器。而小晶体管规模亦有助于保持较低的能耗值,RISC处理器在这方面表现相当杰出,现在的嵌入式设备几乎都采用 RISC产品,原因就在于这类产品的功耗值超低。

过去,PC钟情于X86的原因在于软件兼容,尤其是微软只为X86 PC开发Windows系统,这也被认为是PC采用RISC架构的最大障碍。这个障碍最终也将被解除,Linux操作系统逐渐发展成熟,Mac OS X的综合水准更远在Windows之上,办公、图形、网络、多媒体相关的各类跨平台应用软件极大丰富。如果你是一个游戏玩家,RISC平台一定会令你大呼过瘾,于2005-2006年发布的索尼PS3、任天堂Revolution和微软XBOX等新一代游戏机产品将全面转入RISC体系(有趣的是,三种游戏机都采用IBM所设计的处理器,指令系统相同),短时间内许多品质一流的配套游戏软件将会大量涌现。只要指令系统相同,这些游戏完全可以实现平滑移植。

单从技术角度考虑,以RISC取代X86作为PC的主力架构的确是非常英明的选择,更高的效率、更快的速度、更低的成本以及同样丰富的软件支持, RISC PC将展现出勃勃生机。然而,这一切似乎不容易实现,无论Intel、AMD还是微软,它们的辉煌成就都构建在X86的基础之上,转向RISC对它们来说无异于釜底抽薪。目前执著发展RISC PC的只有苹果公司,它们的全系列PC都基于IBM的PowerPC指令架构。不幸的是,尽管苹果公司大名鼎鼎,但它对整个市场的影响力极其有限,PC转向RISC最大的障碍不在于技术或兼容性,而是缺乏一个实质性的领导者,但有迹象表明,蓝色巨人(IBM)对此有着强烈的意愿,RISC能否把握住PC的下一个三十年尽皆取决于它。

即便不采用RISC架构,我们仍然可以借助它的思想对X86处理器进行结构性改良。事实上,X86处理器一直都从RISC产品中获取灵感,包括EV6总线、整合内存控制器、超线程技术、双核心等等新技术新概念都是首先在RISC产品中得到成功应用,之后才被Intel/AMD引入到X86处理器当中。实践证明,这种做法往往对X86处理器的性能提升有着决定性的影响,而从RISC汲取营养也就成为X86业界的习惯做法。

不过,上述这些技术改良都只停留在应用层面,指令体系的根本差异成为X86与RISC之间的壁垒,若能借助RISC理念对X86处理器进行结构性改良,也许可获取更大的效益。Intel在IDF技术峰会上提出的“PARROT”概念便充分体现了这种思想。PARROT的全称是“Power AwaReness thRough selective dynamically Optimized Traces”,从其名称不难得知,PARROT是一项借助“动态优化执行路径”来提高处理器执行效率的技术。它的理论基础也是著名的80/20法则,但与RISC不同,X86处理器无法从指令系统层面上实现这一点。,Intel另辟蹊径,提出了一个全新的发展思路,将20%的常用指令定义为“热代码(Hot Code)”,剩余的80%指令使用频率没那么高,被定义为“冷代码(Cold Code)”。对应的CPU也在逻辑上被划分为两个部分:一是热核(Hot Spot),只针对调用到热代码的程序;另一部分则是冷核(Cold Spot),负责执行20%的次常用任务。由于热核部分要执行80%的任务,设计者便可以将它设计得较为强大,占据更多的晶体管资源。而冷核部分任务相对简单,没有必要在它身上花费同样的功夫。理论上说,设计者可以将80%的晶体管资源用在热核上面,使之高效率执行任务,剩余的20%晶体管资源则用于仅完成20%任务的冷核。相比之下,现在的X86处理器完全没经过结构优化,所有指令地位对等,80%的次常用指令占据了大量的晶体管资源,又没有创造出相应的价值,芯片内只有20%的区域处于活跃状态,这显然不够科学。

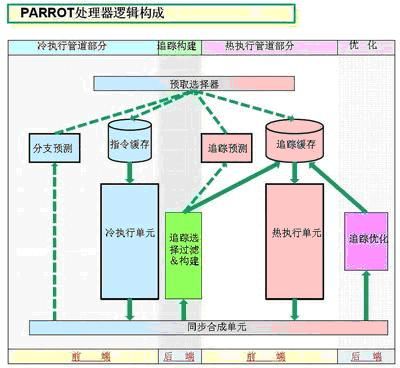

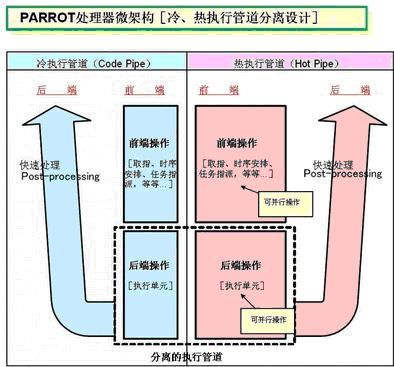

“PARROT”创造了一种崭新的双核概念,过去我们谈论的双核心指的是在一枚芯片内集成两个对等的CPU内核,通过并行运算获得性能增益,我们可以将它看作是横向维度的对等设计。而“PARROT”则是一种纵向维度的双核理念,热核与冷核地位并不对等,且无法独立运作,只能说是一个CPU内核中的两部分分立逻辑。它所起到的是提高CPU的硬件资源利用率,以高执行效率达到高效能的目的,这种做法显然比目前业界鼓吹的“双核心”更具革命意义。我们不妨深入分析“PARROT”的微架构(图2所示),处理器执行管道被分为“冷管道(Cold Pipe)”和“热管道(Hot Pipe)”两部分,二者都拥有彼此独立的取指和执行单元,当处理器读取程序指令时,会预先对其作分析,以判定它是归属于“热代码”还是“冷代码”。若为活跃的“热代码”,则将其送入“热管道”逻辑进行高效处理;如果属于“冷代码”,那么将其送入“冷管道”逻辑处理,所得结果最终再作汇总输出。

图2 PARROT微架构,CPU被划分为相对独立的两个执行管道。

图3所示为“PARROT”处理器的详细执行路径情况,我们可以看到,“冷管道”部分相对简单,只有“指令缓存(Instruction Cache)”、“冷执行单元(Cold Execution)”和“分支预测单元(Branch Prediction)”,占据少量的晶体管即可。而“热管道”部分则显得相当复杂,它由“追踪缓存(Trace Cache)”、“追踪预测单元(Trace Prediction)”、“热执行单元(Hot Execution)”、“追踪优化(Trace Optimizer)”以及“追踪选择过滤&构建(Trace Select Filter&Build)”等几大逻辑单元共同构成,每个逻辑都被设计得尽可能强大。计算结果生成之后,再由“同步合成单元(Synchronized Commit)”组合汇总,最后才通过前端总线输出给计算机内存,由此完成整个运算过程。

图3 基于PARROT思想的X86处理器逻辑结构—冷代码与热代码在执行阶段被彼此分离。

PARROT的新奇思路令人耳目一新,通过对执行单元的结构性优化,X86处理器可以说是获得了重生。设计者可以对“热核”部分进行大大强化,使之拥有更高的效能,在执行多数任务时用户都可感觉到立竿见影的性能提升,而对于冷核的必要压缩则大幅度节省了晶体管资源,并可达到明显降低芯片功耗的目的。设计者可以在晶体管规模不变的前提下,让X86处理器获得数倍的效能提升。毫无疑问,PARROT对于深陷困境的X86架构无疑是雪中送炭,X86处理器将因此出现跨越性的技术进步。而换个角度看,PARROT完全可以说是RISC思想的伟大胜利,80/20法则再度成为魔法的关键,只不过,上一次 IBM基于此建立了伟大的RISC指令系统,而这次是Intel在保持X86软件兼容的前提下,成功实现了对微处理器结构的优化,两种做法可谓是殊途同归。据悉,PARROT技术将在2007年开始进入实用,“Merom”将成为首款基于PARROT思想的处理器内核。大家一定看过这样的新闻:2007 年Intel的服务器处理器、桌面处理器和移动处理器都将采用“Merom”内核,无论性能还是功耗都将有出色的表现,我们有足够的理由对它寄以厚望。

转自:http://hi.baidu.com/iovsdplqyybgrwq/item/d945f0c35fb2df185050585f