微机接口技术及应用(纯手打)——期末复习用

目录

-

概述

-

总线

-

I/O地址译码技术

-

定时、计时技术

-

中断技术

-

DMA技术

-

并行接口

-

串行通信接口

一、概述

接口的作用?

进行CPU与设备之间的信息交换

接口的基本任务?

(1)实现设备与总线的连接

(2)连接后,CPU对设备进行操作或控制

用户接口是所有微机系统都必须具有的接口层次

设备接口和总线桥的概念

(1)设备接口:I/O设备与本地总线之间的连接电路并进行信息交换的中转站,直接传递

(2)总线桥:连接的是本地总线与PCI总线,间接传递(映射)

为什么要设置I/O接口?

(1)总线与设备信号不兼容

(2)总线与设备速度不兼容

(3)避免CPU穷于应付与设备打交道,提高CPU效率

(4)有利于设备的独立发展

I/O设备接口的功能?

(1)执行CPU命令

(2)返回外设状态

(3)数据缓冲

(4)信号转换

(5)设备选择

(6)数据宽度与数据格式转换

接口与CPU交换数据的方式?

用老师收作业举例,老师就是CPU,学生是设备接口

(1)查询方式。老师隔一段时间就挨个问每个学生作业写好了没有,写好了就收,没写好就不收

(2)中断方式。老师不问学生,写好了的同学就立马交给老师

(3)DMA方式。由学习委员(DMA)收作业,一起交给老师,老师不再挨个问学生,不再让学生单独交作业

是不是DMA方式是最高效的??

接口技术的发展趋势

经历了 固定式简单接口——>可编程复杂接口——>功能强大的智能接口 几个发展阶段。

向着更加智能化、多功能化、高集成度化发展

概述就完了~

二、总线

总线这玩意儿在《计算机组成原理》学过,不过当时疫情在家里,学得比较水,这里再当复习一下

总线是啥?

总线是连接微处理器、存储器、外部设备构成微机系统,进行各成员之间相互通信的公共通路

总线包括:

地址线、数据线、控制线

总线最基本的任务

微处理器对外连接和传输信息

总线标准

各成员之间通过总线进行连接和传输信息时,应遵守一些协议与规范,这些协议与规范成为总线标准

性能参数

评价总线好不好,看这几方面

(1)总线频率,MHz表示

(2)总线宽度,数据总线的位数

(3)总线传输率,单位时间内总线上可传输的数据总量,单位MB/s

总线传输率 = (总线宽度 / 8位)X 总线频率

(4)同步的方式

(5)多路复用

(6)负载功能

(7)信号线数

(8)总线控制方式

最重要的是(1)(2)(3),其他的了解就可以啦

总线传输操作过程

申请与仲裁——>寻址——>传输——>结束

总线与接口是啥关系?

外部设备要连接到微机系统中,但不是直接连进去的,接口就是个桥梁作用,接口才是直接挂在总线上的东东,而不是设备

外部设备——>接口——>总线

总线的层次化结构

CPU总线、PCI总线、本地总线(如ISA总线、用户总线)

传输速率依次递减

三、I/O端口地址译码技术

啥叫端口?

是一个I/O地址空间的地址单元

端口与接口的关系?

端口是接口电路中能被CPU访问的寄存器的地址

一个接口电路中可以有几种不同类型的端口:命令(端)口,状态(端)口,数据(端)口

端口的两种编址方式?

(1)独立编址,接口中的端口地址单独编址,不和存储空间合在一起

特点:指令短、执行速度快、地址线少、I/O地址和存储器地址可以重叠,不会混淆

缺点:指令类型少、会增加控制信号引脚

(2)统一编址,从存储空间内划出一片区域来给I/O设备用

特点:增强了I/O处理能力、有较大的寻址空间

缺点:使存储空间变小、执行时间长、增加了地址线等硬件开销

端口的读与写的指令及用法?

有这样一个事实:

AL :8位

AX : 16位

EAX :32位

IN AL, 0F4H; // 从端口0F4H输入 8 位数据到AL

IN AX, OF4H; // 将端口0F4H和端口0F5H的 16 位数据送到AX

IN EAX, OF4H; // 将端口0F4H、0F5H、0F6H、0F7H的 32 位数据送到 EAX

IN EAX, DX; // 将DX所指的端口输入 32 位数据到EAX

OUT DX, EAX; // EAX内容输出到DX所指的32位数据端口

----------- 这是一条华丽的分隔线 -----------

MOV DX, 300H; // 将300H这个端口地址存到DX

IN AL, DX; // 将DX所指端口的 8 位数据输入到AL

MOV [DI], AL; // 将AL的八位数据存到存储器

----------- 这又是一条华丽的分割线 -----------

MOV DX, 300H;

MOV AL, [SI];

OUT DX, AL;

I/O端口寻址方式

就分为直接寻址和间接寻址

区别在于端口地址是否经过DX寄存器传输,是:间接寻址, 否:直接寻址

例如:

IN AX, 0E0H; // 直接

MOV DX, 300H;

IN AX, DX; // 间接

I/O端口地址的选用原则,这个是重点

(1)由系统配置的外部设备占用的地址不能使用

(2)厂家申明保留的地址最好不要使用,否则会发生地址重叠和冲突,造成用户开发的产品与系统不兼容

(3)用户可以使用300到31FH地址,为了避免与其他用户开发的插排发生地址冲突,最好采用可选式地址译码,即开关地址

I/O地址的译码方法

(1)全译码

所有的I/O地址线全部作为译码电路的输入参加译码,一般要求产生单个端口时使用

(2)部分译码

只有高位地址线参加译码, 产生片选信号。一般要求在产生多个接口端口时使用

低位地址线直接连接到接口芯片,进行片内端口寻址——寄存器寻址

(3)开关式译码

在部分译码方法的基础上,加上地址开关来改变端口地址。一般要求I/O端口地址需要改变事使用

电路设计要注意的问题?

(1)遵循I/O端口地址的选用原则

(2)正确的选择译码方法

(3)灵活设计I/O地址译码电路

三八译码器与其他器件一起的使用

待写

四、定时、计时技术

分类

(1)内部定时

产生运算器、控制器等CPU内部的控制时序。

由CPU硬件结构决定,一旦设计好了,就不会变动

单位比外部定时小得多,一般在ns级

(2)外部定时

外设在实现某种功能时所需要的一种时序关系。

可由硬件实现,也可由软件实现,定时长短根据需要而定

定时方法

(1)软件定时

运用编程软件,循环执行一段程序而产生的等待延时

延时长短不仅与延时程序中的延时常数有关,而且会随主机工作频率不同而发生变化

(2)硬件定时

采用外部定时器计时

分为可编程定时器(较灵活)和不可编程定时器

芯片82C54A,绝对的重点

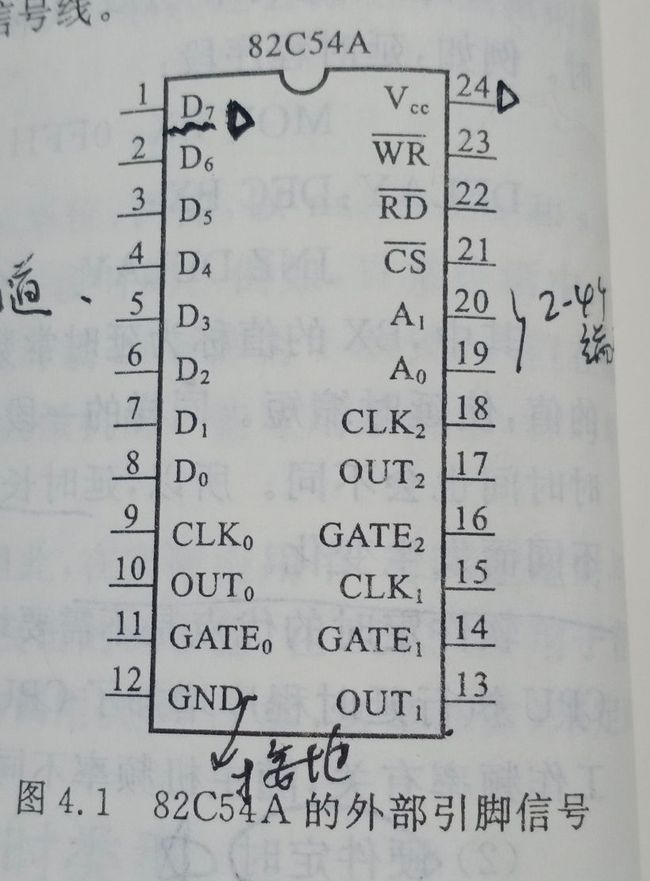

(1)外部连接特性

[1] 面向CPU的信号线

数据线:D0~D7,地址线,CS片选信号,A0、A1(片内端口地址),读/写线,RD(I/O读信号),WR(I/O写信号)

[2] 面向I/O设备的信号线

时钟脉冲信号CLK0~CLK2(输入),用作计数脉冲

门控信号GATE0~GATE2(输入),用于定时/计数的启动和停止

输出信号OUT0~OUT2(输出),用于实现对I/O设备的定时/计时操作

(2)内部结构

3个相同结构的独立的计数器,每个计数器由16位的初值寄存器、减法计数器、当前数值锁存器三部分组成

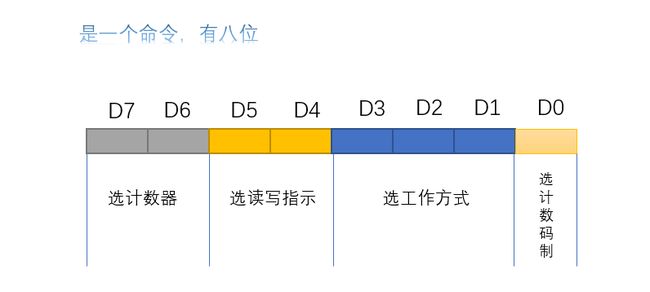

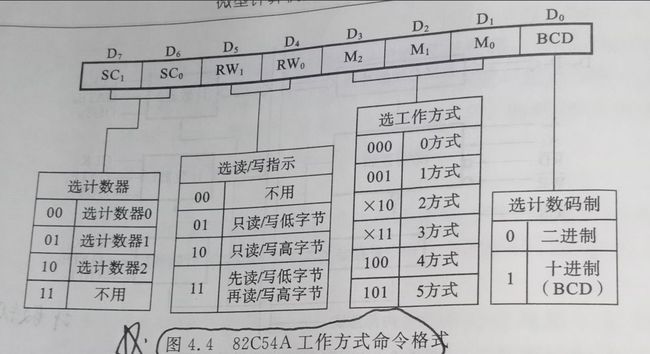

(3)命令字

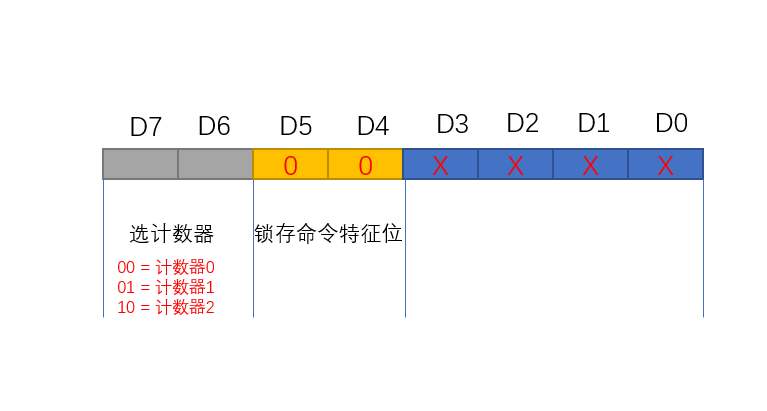

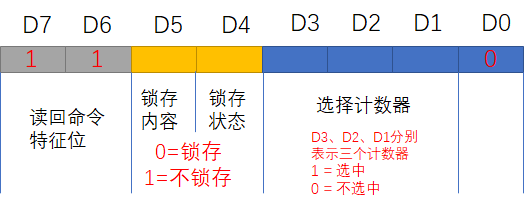

分为三个:方式命令(初始化),锁存命令(当前计数值锁存起来再读),读回命令(既能锁存计数值,又能锁存状态信息)

[1]方式命令,开始工作之前都要使用它进行初始化,格式如下

具体怎样用01码来选,见下

举个例子:

[2]锁存命令

后四位与锁存命令无关

[3]读回命令

[4]工作方式

有6种工作方式:0, 1, 2, 3, 4, 5

由软件启动:0, 2, 3, 4 高电平触发

由硬件启动:1, 5 上升沿触发

需要强制停止:2, 3 (置GATE = 0)

自动停止:0, 1, 4, 5

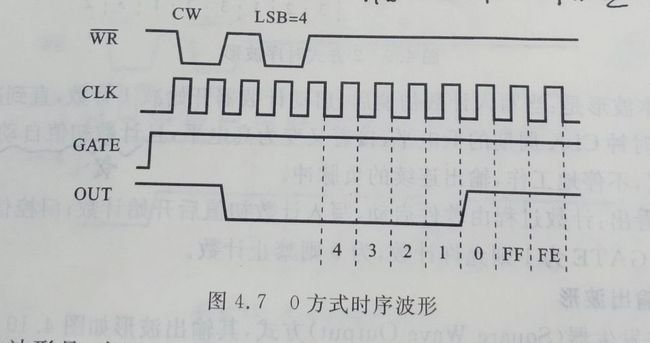

- 0工作方式

做事件计数器,改变计数初值就可以改变计数器的大小

由波形可知

0工作方式:当写入计数值后,计数器开始计数,OUT信号变为低电平,并保持低电平直到计数器的内容减为0,停止工作,OUT信号变为高电平,并保持高电平直到再次写入新的计数值

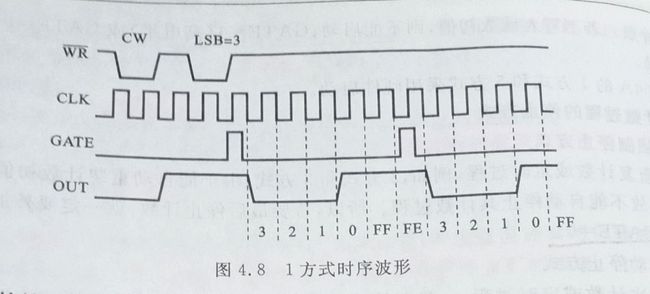

- 1工作方式

硬件可重触发单稳,波形如下:

由波形可知

1工作方式:当写入计数值后,再由GATE门信号启动计数,OUT变为低电平,没来一个CLK,计数器减一直到减到0时,停止工作,OUT输出高电平,并维持高电平到GATE门信号再次启动

可见1方式和0方式的最大区别在于启动方式。1 : 硬件启动, 0:软件启动

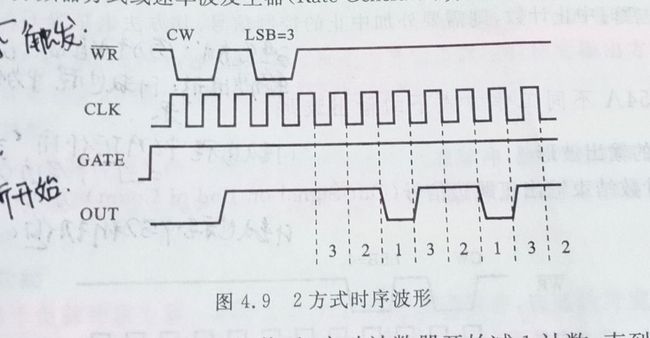

- 2工作方式

N分频器方式或速率波发生器

由波形可知

2工作方式:当写入计数值后,计数器开始计数,直到减到1时,OUT输出一个宽度为时钟CLK周期的低电平,接着又变为高电平,且计数初值自动重装,开始下一轮计数,如此往复,不停地工作,输出连续的负脉冲

和方式0,1的区别:计数时保持高电平,不能自动停止

- 3工作方式

方波发生器

由波形可知

3工作方式:当写入计数值后,计数器开始计数,OUT输出占空比为1:1或近似1:1的连续方波,且计数初值自动重装,开始下一轮的计数,不停地工作,计数初值为偶数时,输出波形的占空比为1:1;为奇数时,输出波形的占空比近似1:1

这个工作方式很特殊:1:1和近似1:1

- 4工作方式

软件触发选通

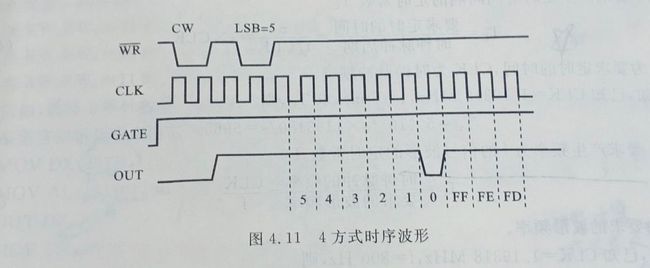

由波形可知

4工作方式:当写入计数初值后,开始计数,OUT输出高电平,直到计数器减到0时,在OUT端输出一个宽度等于时钟CLK脉冲周期的负脉冲,并停止工作,然后OUT信号变为高电平,并保持高电平到再次写入新的计数值

特点:只有计数到0时才为低电平

- 5工作方式

硬件触发选通

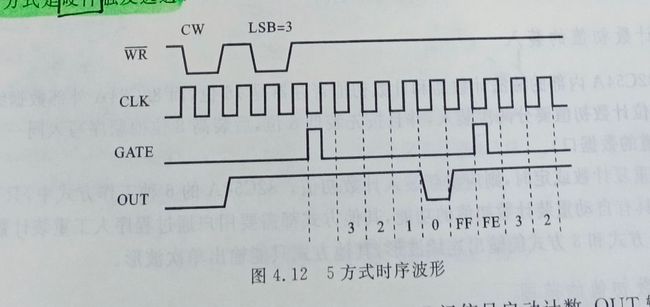

由波形可知

5工作方式:当写入计数初值后,由GATE门信号启动计数,OUT输出高电平,开始减一直到减到0时,在OUT端输出一个宽度等于时钟CLK脉冲周期的负脉冲,并停止工作。然后OUT变为高电平,并维持到高电平直到写入新的计数值

和4工作方式的最大区别在于:启动方式。4:软件启动 5:硬件启动

- 82C54A计算初值

要求产生定时时间间隔的定时常数Tc = 要求定时的时间t / 时钟脉冲周期(1/CLK) = t * CLK

要求产生频率为f的信号波形的定时常数Tc = 时钟脉冲的频率 / 要求的波形频率 = CLK / f

- 82C54A初始化的两个任务

一是设置方式命令

二是设置计数初始值

- 使用汇编语言进行初始化

功能:选择2号计数器,工作在3方式,计数初值为533H(2个字节),采用二进制计数

MOV DX, 307H; // 命令口

MOV AL, 10110110B; // 2号计数器的方式命令字

OUT DX, AL;

// 上面为设置方式命令

MOV DX, 306H; // 2号计数器数据口

MOV AX, 533H; // 计数初值

OUT DX, AL; // 先送低字节到2号计数器

MOV AL, AH; // 取高字节送AL

OUT DX, AL; // 后送高字节到2号计数器

五、中断技术

中断的概念

CPU在正常运行程序时,由于外部/内部随机事件或由程序预先安排的事件,引起CPU暂时中断正在运行的程序,而转为外部/内部或为预先安排的事件服务的程序中去,服务完毕,再返回去继续执行被暂时中断的程序

也就是CPU正在处理程序A,但是B突然插了一手,CPU停止执行A,先执行完B,再继续执行A

中断的分类

可分为两大类:硬中断和软中断

(1)硬中断

是由来自外部的事件产生,具有随机性

可分为可屏蔽中断INTR和不可屏蔽中断NMI(立即照办,在硬件中断中优先级最高)

(2)软中断

是在预料之中的

(1)DOS功能调用

存放在磁盘上的操作系统软件,是用户访问系统资源的主要途径

(2)BIOS功能调用

存放在ROM,独立于DOS的I/O中断服务程序,直接对系统中的I/O设备进行设备级控制

应用

(3)特殊中断

既不是由外部设备提出申请而产生的,也不是由用户在程序中发中断指令而发生的,而是由内部的突发事件所引起的中断,是不可屏蔽中断

0号中断——除数为零

1号中断——单步中断

3号中断——断点中断

4号中断——溢出中断

中断号

系统分配给每个中断源的代号,以便识别和处理

中断号怎样获取?

(1)可屏蔽中断——中断控制器获取

(2)软中断——指令直接给出的

(3)不可屏蔽中断——系统预先设定的

中断响应周期

(1)置位中断服务寄存器ISR

总线控制器发出第一个INTA脉冲

中断服务程序执行完毕后,该寄存器不能自动清零,需要中断控制器发中断结束命令EOI才能清零

(2)读取中断号

总线控制器发出第二个INTA脉冲

中断号的分配

系统对外部中断和内部中断、硬中断和软中断一律统一编号,一共有256个号

中断号是固定不变的,中断号所对应的中断向量是可以改变的

中断向量与中断向量表

通过中断向量表中的中断向量查找程序的入口地址

啥是中断向量?

中断服务程序的入口地址由服务程序的段基址CS(2字节)和偏移地址IP(2字节)两部分组成。

中断向量就是中断服务程序的这4个字节的入口地址

找中断服务程序的本质就是找中断向量

中断向量的段地址SC * 16 + 段地址IP = 存放服务程序第一条指令的物理地址

啥是中断向量表?

把系统中所有的中断向量集中起来放到存储器的某一区域内,这个存储区就是中断向量表

中断向量表的起始地址是固定的,并且从存储器的物理地址0开始

如何在中断向量表中查找服务程序的中断向量?

中断号 X 4得到一个向量表的地址指针,该指针所指向的表项就是服务程序的中断向量,即服务程序的入口地址

中断处理过程

可屏蔽中断的处理过程

(1)中断申请与响应握手

(2)标志位的处理和断点保存

(3)向中断服务程序转移并执行中断服务程序

(3)返回断点

不可屏蔽中断和软件中断的处理过程

不需通过中断响应周期获取中断号

中断服务程序结束,不需要发送中断结束命令

其他与可屏蔽中断一样

中断控制器82C59A,重点

外部特性

有3组信号线

(1)面向CPU的信号线:8根数据线D0~D7,一对中断请求线INT和中断回答线INTA,WR和RD控制线,地址线CS,A0

(2)面向外设的8根中断申请线IR0~IR7

有两个作用:1. 接受外设的中断申请 2. 作中断优先级排队用

(3)面向同类芯片的中断级联信号线,用于扩展中断源

内部寄存器

(1)中断请求寄存器(IRR)

(2)中断服务寄存器(ISR)

INTA信号的活动

ISR的记录由CPU响应中断后发回的第一个中断回答信号INTA1直接置位

清零的方式:

- 在INTA1信号将某位置1后,接着由第二个INTA2将该位置0,这叫自动清零

- 必须在中断服务程序中,用中断结束命令EOI强制清零,这叫非自动清零

(3)中断屏蔽寄存器(IMR)

(4)中断申请优先级分析器(PR)

几乎都是8位

82C59A的编程命令

初始化命令(4个)

对芯片的工作方式和中断号进行设置,包括中断触发方式、级联方式、排队方式及结束方式

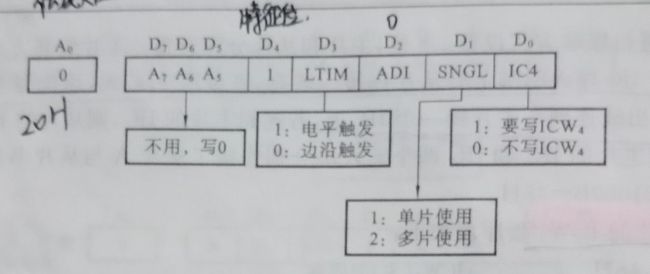

(1)ICW1:进行中断触发方式和单片/多片使用

8位,D3位设置触发方式,D1位设置单/多片使用

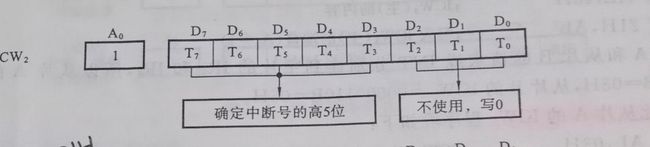

(2)ICW2:进行中断号设置

一共8位,初始化编程时只用写高五位,低三位写0

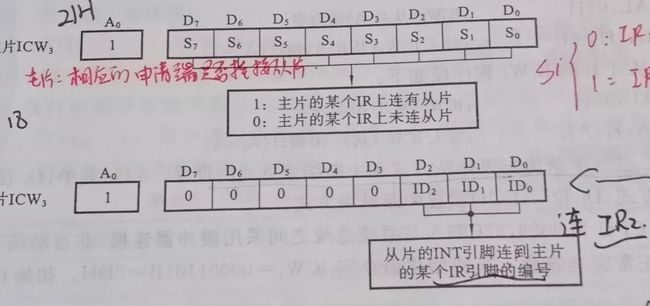

(3)ICW3:进行级联方式设置

8位,主片和从片分开设置

若有从片,则写1,无从片写0

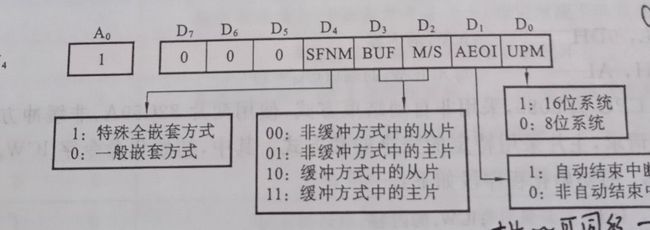

(4)ICW4:设置中断优先级排队方式和中断结束方式

操作命令(3个)

对82C59A经初始化所选定的中断屏蔽(常规中断屏蔽(用OCW1)、特殊中断屏蔽(用OCW3))、中断结束(用OCW2)、中断排队方式(固定的完全嵌套(输入线IR决定)、优先级循环队列(用OCW2))进行操作

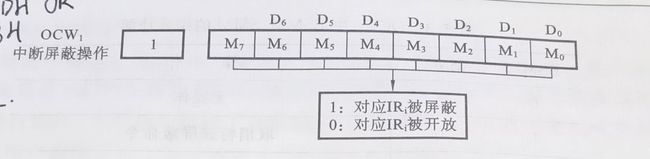

(1)OCW1:控制常规的屏蔽/开放

8位,分别对应8个外部中断请求,置1屏蔽,置0开放

对主片和从片要分别写OCW1

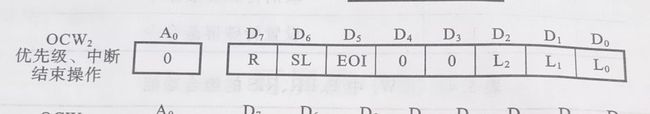

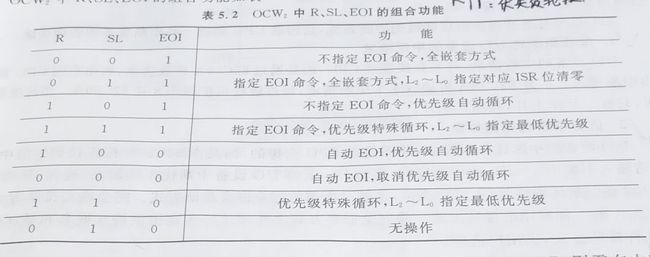

(2)OCW2:执行中断结束和优先级循环排队操作

8位,D6,D5位,D0~D2用于进行中断结束操作

D7位进行优先级循环的操作

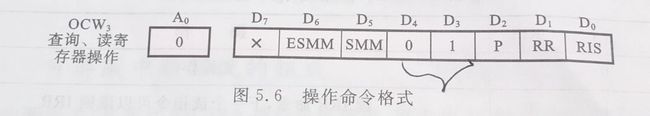

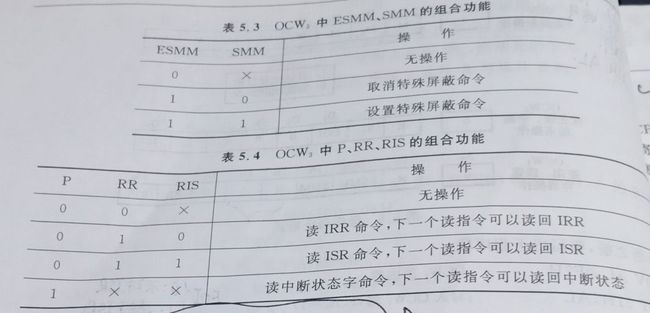

(3)进行特定的屏蔽/开放操作

D6、D5位进行特定的屏蔽/开放操作

D2位作查询时读取状态及RR、RIS用

82C54A对中断管理的作用

- 接收和扩充I/O设备的中断请求

- 进行中断优先级排队

- 向CPU提供中断号

- 进行中断申请的开放与屏蔽

- 执行中断结束命令

修改中断向量的方法

利用DOS功能调用INT 21H的35H号和25H号功能

步骤:

- 调用35H号功能

- 调用25H号功能

- 新中断服务程序完毕后,再用25H号功能将保存在自变量中的原中断写回去,恢复原中断向量

六、DMA技术

存储器直接存储方式、数据不经过CPU而直接写入或从存储器中读出

特点

传输速率高、用硬件控制、DMA传输期间CPU被挂起,部分或完全失去对系统总线的控制(DMA控制器暂时取代CPU)

使用场合

主要用于高速、大批量数据传输的系统中

传输过程

(1)申请阶段

外设向DMAC(DMA控制器)发出DMA请求信号DREQ,如果同意,就进一步向CPU发出总线保持信号

(2)响应阶段

DMAC接管总线正式成为系统的主控者

(3)数据传输阶段

DMAC通知设备传输,同时具有总线控制权,像存储器发地址信号和外设接通,进行传输

(4)传输结束阶段

DMA操作类型

(1)数据传输

(2)数据校验

(3)数据检索

DMA操作方式

(1)单字节方式

(2)连续(块字节)方式

(3)请求(询问)方式

两种工作状态

主动态——主控器

取代CPU,获得系统总线的控制权

被动态——受控器

接受CPU的控制

82C37A——DMA控制器

七、并行接口

特点

(1)以字节、字或双字宽度,在接口与I/O设备之间的多根数据线上传输,因此传输速率快

(2)除数据线外,还可设置握手联络信号,易于实现异步互锁协议,提高数据传输的可靠性

(3)所传输的并行数据的格式、传输速率和工作时序,均由被连接或控制的I/O设备操作的要求绝对,并行接口本身对此没有固定的规定,使用起来自由

(4)一般不作差错检验和传输速率控制

(5)用于近距离传输

(6)实际应用中使用很广泛

八、串行接口

特点

(1)在一根数据线上,传输数据+联络控制信号

(2)传输有固定的格式

(3)在通信设备与计算机之间需要进行逻辑关系及逻辑电平的转换

(4)双方传输速率一致