【HDLBits刷题】Exams/m2014 q4j

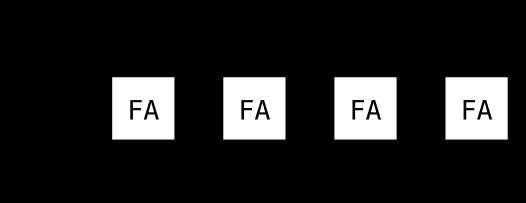

Implement the following circuit:

("FA" is a full adder)

1、第一种,就是采用实例化模块的方式来进行:

module top_module (

input [3:0] x,

input [3:0] y,

output [4:0] sum);

wire cout0,cout1,cout2;

fadd U1(x[0],y[0],0,cout0,sum[0]);

fadd U2(x[1],y[1],cout0,cout1,sum[1]);

fadd U3(x[2],y[2],cout1,cout2,sum[2]);

fadd U4(x[3],y[3],cout2,sum[4],sum[3]);

endmodule

module fadd (

input a, b, cin,

output cout, sum );

assign {cout,sum} = a + b + cin;

endmodule2、第二种,直接使用相加

module top_module (

input [3:0] x,

input [3:0] y,

output [4:0] sum

);

// This circuit is a 4-bit ripple-carry adder with carry-out.

assign sum = x+y; // Verilog addition automatically produces the carry-out bit.

// Verilog quirk: Even though the value of (x+y) includes the carry-out, (x+y) is still considered to be a 4-bit number (The max width of the two operands).

// This is correct:

// assign sum = (x+y);

// But this is incorrect:

// assign sum = {x+y}; // Concatenation operator: This discards the carry-out

endmodule既然没有限制,那么 assign sum = x+y; 自然可以。如果 x+y 产生了进位,verilog 的语法会自动将 x+y 扩展成 5 bit 数。

但有一点,如果使用位连接符 {x+y},那么结果就会被限制为 4 bit 数。这是 Verilog 语法的一个 quirk (怪异之处)。