- Instagram千号矩阵:亚矩阵云手机破解设备指纹检测的终极方案

云云321

矩阵智能手机线性代数

在Instagram的全球化运营中,构建千号矩阵已成为品牌扩大曝光、精准触达用户的核心策略。然而,平台对设备指纹的强监管——通过硬件参数聚类、传感器动态性检测、IP地理一致性校验等200余个维度构建风控模型,使得传统多账号运营面临高封号率、低存活率的双重挑战。亚矩阵云手机通过动态设备指纹重置、智能行为仿真与独立IP池管理三大技术模块,为Instagram千号矩阵提供了安全、高效、低成本的解决方案。

- STM32F103R6的Keil和Protues仿真-点亮LED灯

怎么就重名了

stm32嵌入式硬件单片机

STM32F103R6的Keil和Protues仿真-点亮LED灯STM32F103R6的Keil和Protues仿真-点亮LED灯1、效果1.1、低电平点亮1.2、高电平点亮2、代码2.1、Keil2.2、protueshttps://gitee.com/xiaolixi/l-stm32/tree/master/STM32Protues/diandeng-lowhttps://gitee.com

- 扩展卡尔曼滤波器EKF+无迹卡尔曼滤波器 UKF+泰勒级数的位置估计+三边测量法和多边测量法【7363期】

Matlab研究室

matlab

欢迎来到Matlab研究室博客之家✅博主简介:热爱科研的Matlab仿真开发者,修心和技术同步精进,Matlab项目合作可私信。个人主页:Matlab研究室代码获取方式:Matlab研究室学习之路—代码获取方式(包运行)⛳️座右铭:行百里者,半于九十;路漫漫其修远兮,吾将上下而求索。更多Matlab信号处理仿真内容点击Matlab信号处理(视频版)⛄代码运行视频(CSDN免积分下载)【ACOMTS

- STC15单片机实战笔记一

未来电子机械工程师

单片机STC15实战单片机

新建工程一、新建工程前的准备1、添加型号与头文件到keil第一次新建STC工程时,需要将STC的型号与头文件添加到keil软件中。打开STC-ISP下载工具,切换至keil仿真设置栏,按提示添加即可。2、新建工程文件夹①、在新建工程目录下新建软件开发文件夹用于存放工程文件;②、在软件开发目录下新建user文件夹,用于存放main,public等文件;③、在软件开发目录下新建app文件夹,用于存放应

- (34)FPGA原语设计(BUFGMUX)

宁静致远dream

FPGA就业技能ux开发语言r语言

(34)FPGA原语设计(BUFGMUX)1.1目录1)目录2)FPGA简介3)VerilogHDL简介4)FPGA原语设计(BUFGMUX)5)结语1.2FPGA简介FPGA(FieldProgrammableGateArray)是在PAL、GAL等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门

- AUTOSAR汽车电子嵌入式编程精讲300篇-基于 FPGA 的 CAN 控制器设计与验证(续)

格图素书

汽车fpga开发

目录3CAN控制器的设计3.1CAN的模块构成3.2CPI模块3.2.1CPI模块总设计3.2.2位时序设计3.2.3发送模块设计3.2.4接收模块设计3.2.5错误处理模块设计3.2.6过载帧模块设计3.3CAN控制器的操作模式4CAN控制器的验证4.1基于Vivado软件的CAN控制器仿真4.1.1CAN控制器配置及地址打包4.1.2其余端口配置说明4.1.3Testbench编写说明4.1.

- FPGA小白到项目实战:Verilog+Vivado全流程通关指南(附光学类岗位技能映射)

阿牛的药铺

算法移植部署fpga开发verilog

FPGA小白到项目实战:Verilog+Vivado全流程通关指南(附光学类岗位技能映射)引言:为什么这个FPGA入门路线能帮你快速上岗?本文设计了一条**"Verilog语法→工具链操作→光学项目实战→岗位技能对标"的阶梯式学习路径。不同于泛泛而谈的FPGA教程,我们聚焦光学类产品开发**核心能力(时序接口设计、图像处理算法移植、高速接口应用),通过3个递进式项目(从LED闪烁到图像边缘检测),

- FPGA 设计中的 “Create HDL Wrapper“ 和 “Generating Output Products“ 的区别

行者..................

fpga开发

CreateHDLWrapper(创建HDL包装器)目的:为顶层设计模块(通常是BlockDesign/IPIntegrator设计)创建一个HDL包装文件功能:将图形化/框图设计的BlockDesign转换为可综合的HDL代码(Verilog或VHDL)创建一个顶层模块,将所有IP核和连接实例化使用场景:当使用IPIntegrator创建BlockDesign后需要将图形化设计转换为HDL代码以

- 什么是热力学计算?它如何帮助人工智能发展?

知识大胖

NVIDIAGPU和大语言模型开发教程人工智能量子计算

现代计算的基础是晶体管,这是一种微型电子开关,可以用它构建逻辑门,从而创建CPU或GPU等复杂的数字电路。随着技术的进步,晶体管变得越来越小。根据摩尔定律,集成电路中晶体管的数量大约每两年增加一倍。这种指数级增长使得计算技术呈指数级发展。然而,晶体管尺寸的缩小是有限度的。我们很快就会达到晶体管无法工作的阈值。此外,人工智能的进步使得对计算能力的需求比以往任何时候都更加迫切。根本问题是自然是随机的(

- GMSK调制解调算法的仿真与研究(源码+万字报告+讲解)

炳烛之明科技

算法

目录GMSK调制解调算法的仿真与研究1摘要1Abstract11绪论51.1研究背景及意义51.2国内外研究现状61.3研究内容102几种数字调制方式112.1GMSK调制112.1.1GMSK简介112.1.2GMSK调制原理122.2QPSK调制152.3二进制相移键控(BPSK)163GMSK调制与解调方案与研究173.1GMSK传统调制方法173.1.1直接产生GMSK信号173.1.2P

- 【osgEarth】在osgEarth中实现的一些模型效果:雷达波、通信链路、爆炸、尾焰、轨迹、文字标牌等

bailang_zhizun

OSGosgEarthQTqtc++

学习osgEarth也有一段时间了,记录一下最近一段时间的学习成果。主要是在osgEarth三维场景中实现了一些模型效果,部分模型参考借鉴了西安恒歌的一些显示效果(当然是不能和他们比的doge),期间也从杨总(freesouths)的一些资料、文章中学到了很多,在此也感谢杨总他们的无私奉献。1、简单的仿真小场景简单的仿真小场景,感兴趣的可以看看。基于osgEarth制作的一个简单的飞机对抗仿真小场

- Xilinx系FPGA学习笔记(三)Vivado的仿真及ILA使用

贾saisai

FPGA学习fpga开发学习笔记

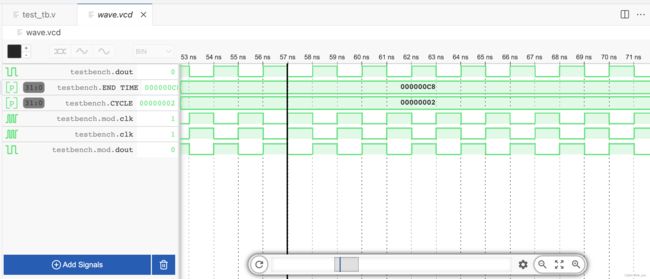

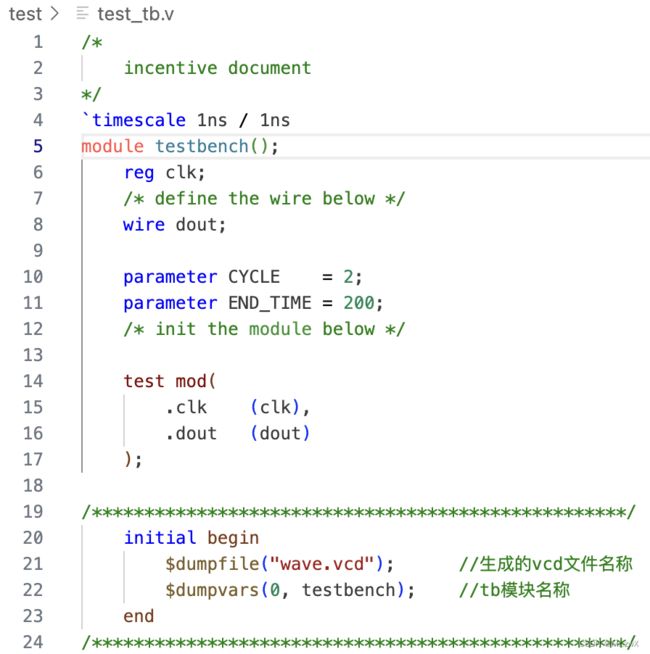

系列文章目录文章目录系列文章目录前言仿真验证(类似modelsim)ILA在线调试工具添加ILAILA的例化ILA的使用前言接着学习vivado的使用方法仿真验证(类似modelsim)首先类似添加.v文件的方法,在File-AddSource中选择Addorcreatesimulationsources或者直接在Sources里面选就行然后就编写testbench,类似之前介绍的modelsim

- 【TCP/IP】14. 远程登录协议

14.远程登录协议14.远程登录协议14.1基本概念14.2Telnet命令14.3Telnet选项及协商14.4Telnet子选项协商14.5Telnet操作模式本章要点14.远程登录协议14.1基本概念Telnet协议是TCP/IP协议族的重要成员,核心功能是实现本地计算机对远程主机的终端仿真,使本地用户能像直接操作远程主机一样访问其资源。远程登录的定义本地用户通过TCP/IP协议进入远程主机

- 单稳态触发器Multisim电路仿真——硬件工程师笔记

逼子歌

单片机语音识别嵌入式硬件硬件工程师真题硬件工程师硬件工程触发器

目录1单稳态触发器基础知识1.1工作原理1.2电路结构1.3特点1.4应用1.5设计考虑1.6总结2555定时器实现的单稳态触发器2.1电路配置2.2工作原理2.3特点2.4应用2.5设计考虑2.6总结3反相器和与非门实现积分型单稳态触发器3.1电路结构3.2工作原理3.3特点3.4应用3.5设计考虑3.6总结4反相器和与非门实现微分型单稳态触发器4.1电路结构4.2工作原理4.3特点4.4应用4

- 英伟达 Isaac ROS产品体验

芝麻香儿

Roadstodeeplearning.AI英伟达IsaacROS

这里写自定义目录标题英伟达IsaacROS产品体验运行的商品名称运行过程记录GPU加速仿真总结英伟达IsaacROS产品体验NVIDIAIsaacROS是一套为自主移动机器人(AMR)开发的硬件加速软件包,专为在NVIDIAGPU和Jetson平台上优化ROS(RobotOperatingSystem)应用程序而设计。它通过提供一系列模块化的ROS包和完整的处理管道,帮助开发者加速AI感知、图像处

- 前沿交叉:Fluent与深度学习驱动的流体力学计算体系

m0_75133639

流体力学深度学习人工智能航空航天fluent流体力学材料科学CFD

基础模块流体力学方程求解1、不可压缩N-S方程数值解法(有限差分/有限元/伪谱法)·Fluent工业级应用:稳态/瞬态流、两相流仿真(圆柱绕流、入水问题)·Tecplot流场可视化与数据导出2、CFD数据的AI预处理·基于PCA/SVD的流场数据降维·特征值分解与时空特征提取深度学习核心3.物理机理嵌入的神经网络架构·物理信息神经网络(PINN):将N-S方程嵌入损失函数(JAX框架实现)·神经常

- 【手把手教程】支付宝沙箱环境部署与调试全流程指南(附源码演示)

源码云商

后端springbootvue.js数据库java

支付宝作为国内最主流的支付平台之一,其提供的沙箱环境是开发者在接入支付宝支付时非常重要的一步。本篇文章将带你从零配置支付宝沙箱环境,实现本地支付接口的调试部署,适用于个人学习、项目开发、毕业设计等多个场景。✨一、什么是支付宝沙箱环境?支付宝沙箱环境是专门提供给开发者进行接口联调测试的仿真环境,与正式环境接口一致,但不涉及真实资金流转,适合用来测试支付、退款、回调等流程。二、准备工作1.注册支付宝开

- 【氮化镓】低剂量率对GaN HEMT栅极漏电的影响

北行黄金橘

氮化镓器件可靠性GaNHEMT氮化镓可靠性辐照栅极漏电γ射线辐照损伤

2024年2月22日,中国科学院新疆理化技术研究所的Li等人在《IEEEACCESS》期刊发表了题为《DegradationMechanismsofGateLeakageinGaN-BasedHEMTsatLowDoseRateIrradiation》的文章,基于实验分析和TCAD仿真,研究了低剂量率辐照下基于GaN的p型栅高电子迁移率晶体管(HEMTs)的栅漏电退化机制。实验采用60Coγ射线源

- 量子化学仿真软件:NWChem_(12).并行计算技术

kkchenjj

化工仿真2化工仿真模拟化工仿真

并行计算技术并行计算技术在量子化学仿真软件中扮演着至关重要的角色。随着计算化学任务的复杂度和数据规模的不断增长,传统的单核计算已经无法满足高性能计算的需求。并行计算通过利用多个处理器或计算节点来分担计算任务,可以在显著减少计算时间的同时提高计算效率。在NWChem中,支持多种并行计算模式,包括共享内存并行(OpenMP)、分布式内存并行(MPI)以及混合并行(OpenMP+MPI)。本节将详细介绍

- 量子化学仿真软件:ORCA_(7).密度泛函理论DFT计算

kkchenjj

化工仿真2化工仿真模拟算法人工智能机器学习化工仿真

密度泛函理论DFT计算密度泛函理论(DensityFunctionalTheory,DFT)是量子化学中一种重要的方法,用于研究多电子系统的电子结构。DFT通过将电子密度作为基本变量,而不是波函数,大大简化了多电子系统的计算复杂度。在ORCA中,DFT计算是常用的计算方法之一,可以用于优化分子结构、计算电子密度、能级、振动频率等。1.基本概念1.1电子密度电子密度定义为单位体积内的电子数。在DFT

- 【论文阅读】Transfer Learning for Automatic Modulation Recognition Using a Few Modulated Signal Samples

摘要:这封信提出了一种用于自动调制识别(AMR)的迁移学习模型,该模型仅具有少量调制信号样本。传输模型以音频信号UrbanSound8K作为源域进行训练,然后以一些调制信号样本为目标域进行微调。为了提高分类性能,信噪比(SNR)被用作一个功能来促进信号的分类。仿真结果表明,迁移模型在分类精度方面具有显著优势。这篇文章的核心内容是提出了一种基于迁移学习(TransferLearning)的自动调制识

- 西门子PLC 1500联合Factory io进行液位控制PID仿真

西门子PLC1500联合Factoryio进行液位控制PID仿真项目调试视频地址:点击查看考虑到大家都是学习用到的,我把仿真的所有资源还是打包上传到了网盘,链接放到了文章的最后,大家自行下载吧!希望我的作品能起到抛砖引玉的效果,期待大家更好的作品!内容总览1.项目构思2.电气图纸设计3.仿真环境硬件组态(FactoryIo)4.PLC程序组态(TIAV15.1)5.触摸屏程序组态(TP1200)6

- SystemVerilog LRM 学习笔记 -- clocking块

1clocking...endclocking块clocking块是SV新feature,主要是为了更好解决testbench和DUT之间的timing和同步建模的问题,可以使user基于clockcycle在更高的抽象层次上写testbench(如“##3”,表示三个clock)。clocking只能在module/interface/checker/program中声明,不能在function

- system Verilog:clocking中定义信号为input和output的区别

加载-ing

systemverilog

在SystemVerilog中,clocking块用于定义时钟块,这通常用于描述时钟边缘和同步的输入/输出行为,特别是在测试平台和硬件接口描述中。在下述两个代码示例中,主要区别在于a被定义为一个input还是output。当a被定义为input时:systemverilogclockingcb@(posedgeclk);inputa;endclocking这意味着a是一个从被测试设计(DUT)到测

- 基于FPGA的二维FFT实现

廉连曼

基于FPGA的二维FFT实现【下载地址】基于FPGA的二维FFT实现本项目提供了一种基于FPGA的高效二维FFT实现方案,专为数字信号处理和图像处理领域设计。通过并行使用两个一维FFT单元,本方案显著提升了二维FFT变换的计算效率,并基于Xilinx的FFTIP核,确保易于集成到其他FPGA设计中。该方案适用于各类频谱分析场景,尤其适合图像处理系统。经过Verilog编程和Modelsim仿真测试

- 基于FPGA的Verilog电子密码锁设计资源文件:为安全而生,智控锁码

基于FPGA的Verilog电子密码锁设计资源文件:为安全而生,智控锁码【下载地址】基于FPGA的Verilog电子密码锁设计资源文件基于FPGA和Verilog语言设计的电子密码锁项目,提供完整的硬件设计原理图、Verilog代码、仿真波形图和硬件描述文档。通过FPGA的可编程特性,实现密码设置、验证及锁定功能,适合学术研究、教学演示或个人兴趣学习。项目文件清晰,包含详细的使用说明,帮助用户快速

- 《数字集成电路——课程设计报告》资源介绍

幸刚磊Thomas

《数字集成电路——课程设计报告》资源介绍【下载地址】数字集成电路课程设计报告资源介绍该开源项目提供了《数字集成电路——课程设计报告》的完整资源,专为电子工程及相关专业的学生和研究人员设计。报告详细介绍了与非门、或非门、反相器、主从JK触发器以及二-四译码器等基础逻辑电路的搭建与仿真过程。通过使用Cadence和LTspice软件,学习者可以掌握数字集成电路的实际设计技能。报告内容深入浅出,适合具备

- 【FFT】基于FPGA的FFT傅里叶变换和相位计算系统设计

fpga和matlab

★FPGA项目经验板块19:信号发生器fpga开发FFT相位计算

1.软件版本ISE14.7,modeslimSE,10.1c2.系统仿真与分析第1步:信号源的产生主要通过rom将产生的数据保存到rom中,然后,我们再仿真的时候调用即可。这个部分仿真效果如下所示,你给的程序中,这个部分主要有两个数据源,一个是1025,一个是N为1024,我们这里分别将这两个数据量化之后保存到rom中,仿真如下所示:

- [SystemVerilog] Clocking

S&Z3463

SystemVerilogfpga开发

SystemVerilogClocking用法详解SystemVerilog的clocking块(ClockingBlock)是一种专门用于定义信号时序行为的构造,主要用于验证环境(如UVM)中,以精确控制信号的采样和驱动时序。clocking块通过将信号与特定时钟关联,简化了测试环境中对时序敏感信号的处理,减少了手动时序管理的复杂性。本文将详细介绍SystemVerilog中clocking块的

- python网络仿真模拟_复杂网络仿真工具networkX的环境搭建(Windows环境)

写这篇文章的目的是希望没有编程经验的小白也能够跟着文章的指示搭建自己的networkx环境,所以写得很初步很详细,会编程的人也不妨一看,可以避开一些我已经绕过的弯路我的PC环境是windows764位操作系统1.安装python,networkX属于python的一个模块,所以要先安装python;python可以去官网下载(官网上有不同版本的python,根据自己的PC环境下载)我下载的是文件p

- java数字签名三种方式

知了ing

javajdk

以下3钟数字签名都是基于jdk7的

1,RSA

String password="test";

// 1.初始化密钥

KeyPairGenerator keyPairGenerator = KeyPairGenerator.getInstance("RSA");

keyPairGenerator.initialize(51

- Hibernate学习笔记

caoyong

Hibernate

1>、Hibernate是数据访问层框架,是一个ORM(Object Relation Mapping)框架,作者为:Gavin King

2>、搭建Hibernate的开发环境

a>、添加jar包:

aa>、hibernatte开发包中/lib/required/所

- 设计模式之装饰器模式Decorator(结构型)

漂泊一剑客

Decorator

1. 概述

若你从事过面向对象开发,实现给一个类或对象增加行为,使用继承机制,这是所有面向对象语言的一个基本特性。如果已经存在的一个类缺少某些方法,或者须要给方法添加更多的功能(魅力),你也许会仅仅继承这个类来产生一个新类—这建立在额外的代码上。

- 读取磁盘文件txt,并输入String

一炮送你回车库

String

public static void main(String[] args) throws IOException {

String fileContent = readFileContent("d:/aaa.txt");

System.out.println(fileContent);

- js三级联动下拉框

3213213333332132

三级联动

//三级联动

省/直辖市<select id="province"></select>

市/省直辖<select id="city"></select>

县/区 <select id="area"></select>

- erlang之parse_transform编译选项的应用

616050468

parse_transform游戏服务器属性同步abstract_code

最近使用erlang重构了游戏服务器的所有代码,之前看过C++/lua写的服务器引擎代码,引擎实现了玩家属性自动同步给前端和增量更新玩家数据到数据库的功能,这也是现在很多游戏服务器的优化方向,在引擎层面去解决数据同步和数据持久化,数据发生变化了业务层不需要关心怎么去同步给前端。由于游戏过程中玩家每个业务中玩家数据更改的量其实是很少

- JAVA JSON的解析

darkranger

java

// {

// “Total”:“条数”,

// Code: 1,

//

// “PaymentItems”:[

// {

// “PaymentItemID”:”支款单ID”,

// “PaymentCode”:”支款单编号”,

// “PaymentTime”:”支款日期”,

// ”ContractNo”:”合同号”,

//

- POJ-1273-Drainage Ditches

aijuans

ACM_POJ

POJ-1273-Drainage Ditches

http://poj.org/problem?id=1273

基本的最大流,按LRJ的白书写的

#include<iostream>

#include<cstring>

#include<queue>

using namespace std;

#define INF 0x7fffffff

int ma

- 工作流Activiti5表的命名及含义

atongyeye

工作流Activiti

activiti5 - http://activiti.org/designer/update在线插件安装

activiti5一共23张表

Activiti的表都以ACT_开头。 第二部分是表示表的用途的两个字母标识。 用途也和服务的API对应。

ACT_RE_*: 'RE'表示repository。 这个前缀的表包含了流程定义和流程静态资源 (图片,规则,等等)。

A

- android的广播机制和广播的简单使用

百合不是茶

android广播机制广播的注册

Android广播机制简介 在Android中,有一些操作完成以后,会发送广播,比如说发出一条短信,或打出一个电话,如果某个程序接收了这个广播,就会做相应的处理。这个广播跟我们传统意义中的电台广播有些相似之处。之所以叫做广播,就是因为它只负责“说”而不管你“听不听”,也就是不管你接收方如何处理。另外,广播可以被不只一个应用程序所接收,当然也可能不被任何应

- Spring事务传播行为详解

bijian1013

javaspring事务传播行为

在service类前加上@Transactional,声明这个service所有方法需要事务管理。每一个业务方法开始时都会打开一个事务。

Spring默认情况下会对运行期例外(RunTimeException)进行事务回滚。这

- eidtplus operate

征客丶

eidtplus

开启列模式: Alt+C 鼠标选择 OR Alt+鼠标左键拖动

列模式替换或复制内容(多行):

右键-->格式-->填充所选内容-->选择相应操作

OR

Ctrl+Shift+V(复制多行数据,必须行数一致)

-------------------------------------------------------

- 【Kafka一】Kafka入门

bit1129

kafka

这篇文章来自Spark集成Kafka(http://bit1129.iteye.com/blog/2174765),这里把它单独取出来,作为Kafka的入门吧

下载Kafka

http://mirror.bit.edu.cn/apache/kafka/0.8.1.1/kafka_2.10-0.8.1.1.tgz

2.10表示Scala的版本,而0.8.1.1表示Kafka

- Spring 事务实现机制

BlueSkator

spring代理事务

Spring是以代理的方式实现对事务的管理。我们在Action中所使用的Service对象,其实是代理对象的实例,并不是我们所写的Service对象实例。既然是两个不同的对象,那为什么我们在Action中可以象使用Service对象一样的使用代理对象呢?为了说明问题,假设有个Service类叫AService,它的Spring事务代理类为AProxyService,AService实现了一个接口

- bootstrap源码学习与示例:bootstrap-dropdown(转帖)

BreakingBad

bootstrapdropdown

bootstrap-dropdown组件是个烂东西,我读后的整体感觉。

一个下拉开菜单的设计:

<ul class="nav pull-right">

<li id="fat-menu" class="dropdown">

- 读《研磨设计模式》-代码笔记-中介者模式-Mediator

bylijinnan

java设计模式

声明: 本文只为方便我个人查阅和理解,详细的分析以及源代码请移步 原作者的博客http://chjavach.iteye.com/

/*

* 中介者模式(Mediator):用一个中介对象来封装一系列的对象交互。

* 中介者使各对象不需要显式地相互引用,从而使其耦合松散,而且可以独立地改变它们之间的交互。

*

* 在我看来,Mediator模式是把多个对象(

- 常用代码记录

chenjunt3

UIExcelJ#

1、单据设置某行或某字段不能修改

//i是行号,"cash"是字段名称

getBillCardPanelWrapper().getBillCardPanel().getBillModel().setCellEditable(i, "cash", false);

//取得单据表体所有项用以上语句做循环就能设置整行了

getBillC

- 搜索引擎与工作流引擎

comsci

算法工作搜索引擎网络应用

最近在公司做和搜索有关的工作,(只是简单的应用开源工具集成到自己的产品中)工作流系统的进一步设计暂时放在一边了,偶然看到谷歌的研究员吴军写的数学之美系列中的搜索引擎与图论这篇文章中的介绍,我发现这样一个关系(仅仅是猜想)

-----搜索引擎和流程引擎的基础--都是图论,至少像在我在JWFD中引擎算法中用到的是自定义的广度优先

- oracle Health Monitor

daizj

oracleHealth Monitor

About Health Monitor

Beginning with Release 11g, Oracle Database includes a framework called Health Monitor for running diagnostic checks on the database.

About Health Monitor Checks

Health M

- JSON字符串转换为对象

dieslrae

javajson

作为前言,首先是要吐槽一下公司的脑残编译部署方式,web和core分开部署本来没什么问题,但是这丫居然不把json的包作为基础包而作为web的包,导致了core端不能使用,而且我们的core是可以当web来用的(不要在意这些细节),所以在core中处理json串就是个问题.没办法,跟编译那帮人也扯不清楚,只有自己写json的解析了.

- C语言学习八结构体,综合应用,学生管理系统

dcj3sjt126com

C语言

实现功能的代码:

# include <stdio.h>

# include <malloc.h>

struct Student

{

int age;

float score;

char name[100];

};

int main(void)

{

int len;

struct Student * pArr;

int i,

- vagrant学习笔记

dcj3sjt126com

vagrant

想了解多主机是如何定义和使用的, 所以又学习了一遍vagrant

1. vagrant virtualbox 下载安装

https://www.vagrantup.com/downloads.html

https://www.virtualbox.org/wiki/Downloads

查看安装在命令行输入vagrant

2.

- 14.性能优化-优化-软件配置优化

frank1234

软件配置性能优化

1.Tomcat线程池

修改tomcat的server.xml文件:

<Connector port="8080" protocol="HTTP/1.1" connectionTimeout="20000" redirectPort="8443" maxThreads="1200" m

- 一个不错的shell 脚本教程 入门级

HarborChung

linuxshell

一个不错的shell 脚本教程 入门级

建立一个脚本 Linux中有好多中不同的shell,但是通常我们使用bash (bourne again shell) 进行shell编程,因为bash是免费的并且很容易使用。所以在本文中笔者所提供的脚本都是使用bash(但是在大多数情况下,这些脚本同样可以在 bash的大姐,bourne shell中运行)。 如同其他语言一样

- Spring4新特性——核心容器的其他改进

jinnianshilongnian

spring动态代理spring4依赖注入

Spring4新特性——泛型限定式依赖注入

Spring4新特性——核心容器的其他改进

Spring4新特性——Web开发的增强

Spring4新特性——集成Bean Validation 1.1(JSR-349)到SpringMVC

Spring4新特性——Groovy Bean定义DSL

Spring4新特性——更好的Java泛型操作API

Spring4新

- Linux设置tomcat开机启动

liuxingguome

tomcatlinux开机自启动

执行命令sudo gedit /etc/init.d/tomcat6

然后把以下英文部分复制过去。(注意第一句#!/bin/sh如果不写,就不是一个shell文件。然后将对应的jdk和tomcat换成你自己的目录就行了。

#!/bin/bash

#

# /etc/rc.d/init.d/tomcat

# init script for tomcat precesses

- 第13章 Ajax进阶(下)

onestopweb

Ajax

index.html

<!DOCTYPE html PUBLIC "-//W3C//DTD XHTML 1.0 Transitional//EN" "http://www.w3.org/TR/xhtml1/DTD/xhtml1-transitional.dtd">

<html xmlns="http://www.w3.org/

- Troubleshooting Crystal Reports off BW

blueoxygen

BO

http://wiki.sdn.sap.com/wiki/display/BOBJ/Troubleshooting+Crystal+Reports+off+BW#TroubleshootingCrystalReportsoffBW-TracingBOE

Quite useful, especially this part:

SAP BW connectivity

For t

- Java开发熟手该当心的11个错误

tomcat_oracle

javajvm多线程单元测试

#1、不在属性文件或XML文件中外化配置属性。比如,没有把批处理使用的线程数设置成可在属性文件中配置。你的批处理程序无论在DEV环境中,还是UAT(用户验收

测试)环境中,都可以顺畅无阻地运行,但是一旦部署在PROD 上,把它作为多线程程序处理更大的数据集时,就会抛出IOException,原因可能是JDBC驱动版本不同,也可能是#2中讨论的问题。如果线程数目 可以在属性文件中配置,那么使它成为

- 正则表达式大全

yang852220741

html编程正则表达式

今天向大家分享正则表达式大全,它可以大提高你的工作效率

正则表达式也可以被当作是一门语言,当你学习一门新的编程语言的时候,他们是一个小的子语言。初看时觉得它没有任何的意义,但是很多时候,你不得不阅读一些教程,或文章来理解这些简单的描述模式。

一、校验数字的表达式

数字:^[0-9]*$

n位的数字:^\d{n}$

至少n位的数字:^\d{n,}$

m-n位的数字:^\d{m,n}$