第一章 手册说明

第一章 手册说明

https://cbvnbb7duj.feishu.cn/docx/W0fudLaJno4nbExEDqbc62NCnGc?from=from_copylink

Intel架构软件开发人员手册包含四卷:

- 第一卷:《基本架构》,介绍了Intel 64和IA-32架构处理器的基本架构及其编程环境;

- 第二卷:《指令集索引》,介绍了处理器指令集和操作码(opcode)结构;

- 第三卷:《系统编程指南》,介绍了Intel 64和IA-32处理器的操作系统支持环境;

- 第四卷:《模型特异的寄存器》,介绍了Intel 64和IA-32处理器模型特异的寄存器;

第一卷和第二卷适用于应用编程人员、操作系统或执行器(executive)编程人员,第三卷面向操作系统和BIOS设计者,另外,卷3B提供了运行操作系统的软件类的编程环境;

1.1 本手册涵盖的Intel 64和IA-32处理器

参见手册

1.2 卷一概述:基本架构

- 第一章:手册说明:对手册四卷内容的概述,介绍了手册中使用的符号惯例,列出了相关的Intel手册和文档;

- 第二章:Intel 64和 IA-32架构:沿着基于其架构的Intel处理器家族,介绍了Intel 64和 IA-32架构;同时简要概述了相关处理器中的一般特性及Intel 64和 IA-32架构的简要历史;

- 第三章:基本执行环境:介绍了内存组织的模型,介绍了应用使用的寄存器;

- 第四章:数据类型:介绍了数据类型和处理器支持的寻址模式,概述了实数和浮点数格式,及浮点异常;

- 第五章:指令集汇总:列出了按技术组划分的所有Intel 64和 IA-32的指令;

- 第六章:过程调用,中断和异常:介绍了程序堆栈,以及用于过程调用,处理中断和异常的机制;

- 第七章:使用通用指令编程:介绍了操作基本数据类型,通用和段寄存器的,基本的加载(load)和存储(store),程序控制,算术和字符串指令;同时介绍了在保护模式下运行的系统指令

- 第八章:使用x87FPU编程(浮点运算单元):介绍了x87浮点运算单元,包括浮点寄存器和数据类型;概述了浮点指令集并介绍了处理器浮点异常情况;

- 第九章:使用Intel MMX(multi media extension)技术编程:介绍了Intel MMX技术,包括MMX寄存器和数据类型;同时概述了MMX指令集;

- 第十章:使用Intel SSE扩展指令集编程(streaming SIMD extension,single instruction multiple data, SIMD):介绍了SSE扩展,包括XMM寄存器,MXCSR寄存器,打包的单精度浮点数据类型(一次可操作多个数据,例如向量加法),简要概述了SSE指令集,给出了使用SSE扩展指令集的编程指南;

- 第十一章:使用Intel SSE2扩展指令集编程:介绍了SSE2扩展,包括包括XMM寄存器和打包的双精度浮点数据类型;概述了SSE2指令集并给出了使用SSE2扩展指令集的编程指南。同时介绍了可由SSE和SSE2指令产生的SIMD单精度浮点异常,同时提供了在操作系统和应用代码中整合SSE和SSE2扩展的通用指南;

- 第十二章:使用SSE3、SSSE3、SSE4和AES-NI(AES new instructions)扩展指令集编程:概述SSE3、SSSE3,SSE4和AES-NI指令集,提供使用这些扩展编程的指南;

- 第十三章:使用XSAVE特征集(feature set)管理状态:介绍了XSAVE特征集,并阐明软件如何激活XSAVE特征集和XSAVE支持的特性;

- 第十四章:使用AVX、FMA和AVX2编程:简要概述了Intel AVX指令集,FMA和Intel AVX2扩展,提供了使用这些扩展指令集的编程指南;

- 第十五章:使用Intel AVX-512编程:简要介绍了AVX-512指令集扩展,提供了使用这些指令集的编程指南;

- 第十六章:使用Intel事务同步扩展编程(Transactional synchronization extension,HTM 硬件事物内存):介绍了该指令集扩展,该指令集使用锁省略(lock elision)技术实现带争用锁的多线程软件性能提升;

- 第十七章:Intel内存保护扩展:简要介绍了Intel内存保护扩展,并给出了使用这些扩展的编程指南;

- 第十八章:控制流实施技术(control-flow enforcement technology):简要介绍了控制流实施技术,并给出了使用这些扩展的编程指南;

- 第十九章:输入/输出:介绍了处理器的IO机制,包括IO端口寻址,IO指令,IO保护机制;

- 第二十章:处理器识别和特性确定:介绍了如何确定CPU类型及CPU可使用的特性的方法;

- 附录A:标志寄存器(EFLAGS corss-reference):总结了IA-32指令如何影响标志寄存器中的标志;

- 附录B:标志寄存器状态码(EFLAGS condition code):总结了条件跳转,MOV,设置状态码(condition code)的相关指令如何使用标志寄存器中的状态标志(OF,CF,ZF,SF,PF);

- 附录C:浮点异常总结:总结了X87FPU和SSE/SSE2/SSE3 浮点指令集引起的异常;

- 附录D:编写SIMD浮点异常处理句柄/处理程序(handler)的指南:给出了编写异常处理程序的指南(由SSE/SSE2/SSE3 浮点指令集产生的异常);

1.3 符号惯例

本手册为数据结构格式,指令的符号表示,16进制和2进制数规定了特殊的符号;

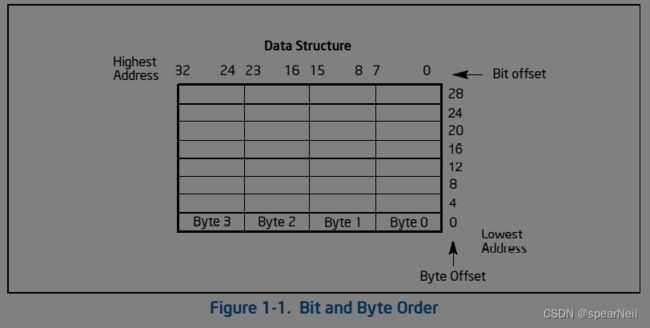

1.3.1 比特和字节顺序

| 在内存数据结构的插图中,地址顺序由下到上递增,小地址位于图底端;比特位从右到左排序,左边的表示高位;Intel 64 和 IA-32处理器使用小端机(即高位放高位字节,低位放低位字节) |

|---|

1.3.2 保留位和软件兼容性

在许多寄存器和内存分布的描述中,一些位会被标注为保留位(reserved)。当比特位被标注为保留位时,对兼容未来的处理器中时非常重要的(在未来的这些处理器中,软件会把这些位视为有作用的一些比特位位,尽管这些作用现在还未知)。保留位的行为不仅应该视为未定义的,也应该视为不可预测的。软件处理这些保留位时应该遵循以下几点:

- 当测试包含保留位的寄存器的值时,不要依赖于任何保留位的状态;而应该在测试前掩盖这些保留位;

- 当向内存或寄存器进行存操作(store)时,不要依赖于任何寄存器状态;

- 不要依赖于保留位可以保留信息的功能,即不要使用保留位存储任何信息;

- 当加载一个寄存器时,保证总是用文档中指定的值加载保留位(如果有的话),否则,用该寄存器中保留位的之前读取的值重新加载保留位;

注:请避免任何软件依赖于保留位的状态,依赖保留位的状态会使得软件依赖于处理器处理保留位的未指定方式,依赖于保留位的程序有和未来处理器不兼容的风险

1.3.2.1 指令操作数(instruction operand)

指令的符号化表示使用IA-32汇编语言的子集,在该子集中指令具有如下格式:

label : mnemonic argument1, argument2, argument3

| label: 跟着冒号的一个标签; mnemonic:具有相同功能的一类指令的保留名字(助记符); argument1, argument2, argument3:可选的操作数(0-3,依赖于操作码);当他们存在于指令中,其格式可以为字面值(literal,常量)或者数据的标识符;操作数标识符可以是寄存器的助记符或者在程序中其他位置已经分配的数据项; |

|---|

当算术或逻辑指令中有两个操作数时:右操作数为源操作数(source),而左操作数为目的操作数(destination)(一些汇编语言使用相反的源和目的操作数顺序,如AT&T汇编)

例如:LOADREG: MOV EAX, SUBTOTAL

1.3.3 16和2进制数

16进制数末尾使用H标注(例:0F82H);二进制数末尾使用B标注(例:1010B);

1.3.4 段寻址

处理器使用字节寻址,这意味着内存以字节序列的方式组织和访问;不管单字节还是多字节的访问,都使用字节寻址定位内存;可寻址的内存范围称为:地址空间

处理器也支持段寻址。段寻址是寻址的一种方式,在这种模式下,一个程序可能有很多独立的地址空间,**称之为段(segment)。**例如一个程序可以将其代码和堆栈分为不同的段,代码寻址永远访问代码空间,堆栈寻址重视访问堆栈空间。下述记号用于表示使用段的字节寻址:

Segment-register : Byte-address

例如:

DS : FF79H (DS寄存器指向的段中的FF79H地址);

CS : EIP (CS寄存器指向代码段,EIP指向具体的指令的地址);

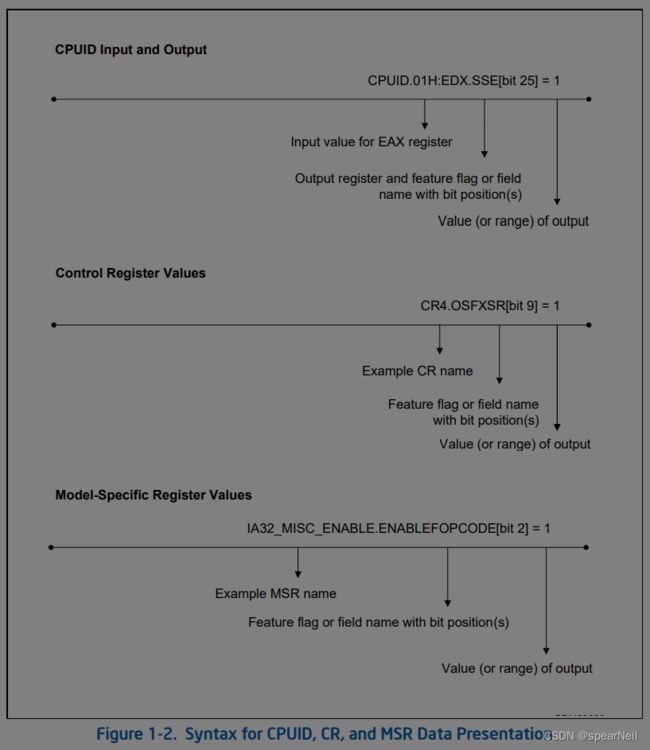

1.3.5 CPUID,CR和MSR值的新语法

通过CPUID指令检查控制寄存器,读取模型特异的寄存器,可以得到特性标志,状态和系统信息;

1.3.6 异常

异常即是在指令出错时发生的事件;例如零除异常。但是,一些异常(例如断点)在其他情况下发生。一些异常类型可能提供错误码。错误码提供了错误的附加信息。例如:

#PF(fault code):缺页错误;

在另外一些情况下,异常可能不能产生提供准确的错误码,此时错误码为0,如:#GP(0)

1.4 相关文档