计算机体系结构实验——Branch-Target Buffers

实验五 Branch-Target Buffers

本次实验的主要目的是加深对Branch-Target Buffers的理解。掌握使用Branch-Target Buffers减少或增加分支带来的延迟的情况。

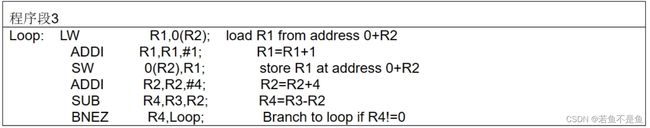

实验内容: 将以下程序段修改为可利用WinMIPS64模拟器运行的程序。假设R3的初始值为R2+40

在使用forwarding的情况下,对比采用BTB与不采用BTB技术时流水线的变化。重点分析两种情况下每次循环的stall周期数,都是由什么原因造成的?重点分析与分支指令相关的stall。采用BTB技术时何时能够减少分支指令带来的暂停?何时会增加暂停?为什么?

实验报告:

将程序段3修改为WinMIPS64模拟器可以运行的程序如下:

.text

main:

DADDI R3,R2,40;

Loop:

LW R1,0(R2)

DADDI R1,R1,1

SW R1,0(R2)

DADDI R2,R2,4

DSUB R4,R3,R2

BNEZ R4,Loop

end: halt

在使用forwarding,不使用BTB技术的情况下造成的暂停以及原因介绍如下:

数据相关:

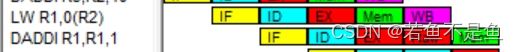

1、由于LW指令取数放入R1中在Mem阶段才能到内存中取到数值,而下一条指令需要使用到R1寄存器的数值,存在RAW相关会造成一个周期的暂停

2、由于DSUB那条指令最后要将结果写到R4中并且在EX阶段结束后才能获得存放到R4中的数值,而跳转指令需要在ID阶段判断是否要跳转,所以会产生RAW相关,暂停一个周期

控制相关:

3、由下图红框中的指令可以看出,它在处理跳转指令的时候采用的是预测转移失败的行为,但在实际指令运行过程中,指令成功转移,所以会清空流水线,重新取指令,造成一个周期的暂停

在使用forwarding技术,并且使用BTB技术的情况下造成的暂停以及原因介绍如下:

数据相关:

由于在这种情况下所产生的数据相关与不使用BTB的情况下的数据相关相同,所以不再加以介绍

结构相关:

1、在第一次循环结束时,由于BTB表为空,预测为转移失败,但实际转移成功。所以在ex段执行中会将转移指令地址连同下一条指令的pc值放入BTB中,并且清空流水线,重新取指执行,造成两个周期的暂停。

2、在第二次循环以及后续的八次循环中,由于该条跳转指令在IF段会查找BTB表,并且会在表中查到对应的指令的地址,所以会预测转移成功,并且将转移地址放入PC中,因此不存在结构相关,不会造成暂停。

3、在最后一次循环时,由于BTB表中存在对应跳转指令的地址,所以会预测转移成功,但实际上会转移失败,所以会在转移指令的EX阶段中删除BTB表中对应的表项,同时在ex阶段执行结束后会清空流水线重新取指来运行,造成两个周期的暂停。

由以上可以发现在:

预测正确的时候可以减少暂停:跳转指令在IF阶段会查找BTB表,如果查找到会将下一条指令的地址放入PC寄存器中。如果预测正确则可以在下一个周期就开始下一条指令的取指阶段,而不需要等待跳转指令的ID段执行结束才能执行下一条指令的取指阶段。

预测错误时会增加暂停:由上述程序第一个阶段和最后一个可以看到,如果预测失败,不仅要清空流水线还要修改BTB表中存储的指令地址以及下一条指令的PC值,会造成两个周期的暂停。