【基于FPGA的可调数字钟设计】

基于FPGA的可调数字钟设计

- 前言

- 一、设计要求

- 二、实现过程

-

- 1.总体设计思想

- 2.设计模块分析

- 三、系统调试

- 结语

前言

近年来由于美国对我国芯片行业的封锁,我国芯片行业迎来了一波发展的浪潮,FPGA这款小众而又实用的芯片也被划在制裁名单中。

一、设计要求

(1)、能在开发板的数码管上显示时间功能

(2)、正常显示时、分、秒

(3)、4个按键:一个作为rst复位,1个作为数字钟调节时的切 换,1个作为按键加,1个作为按键减

(4)、按键切换小时/分钟时对应闪烁

二、实现过程

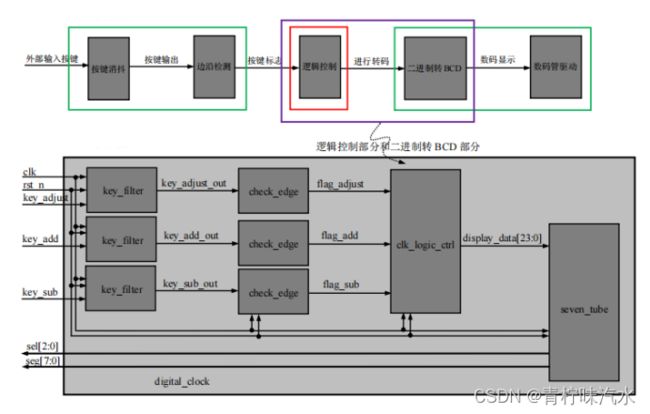

1.总体设计思想

其中的数字钟逻辑控制模块由于涉及设计显示时间的核心设计比较复杂,将数字钟逻辑控制模块拆分为若干个模块:逻辑控制模块(logic_ctrl)、秒控制模块(sec_ctrl)、分钟控制模块(min_ctrl)、小时控制模块(hour_ctrl ) 、二进制转BCD(bin_bcd ) 、 小时闪烁模块(hour_adjust)、分钟闪烁模块(min_adjust)

2.设计模块分析

2.1按键

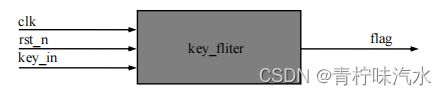

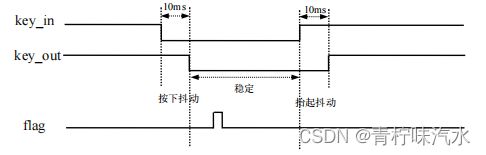

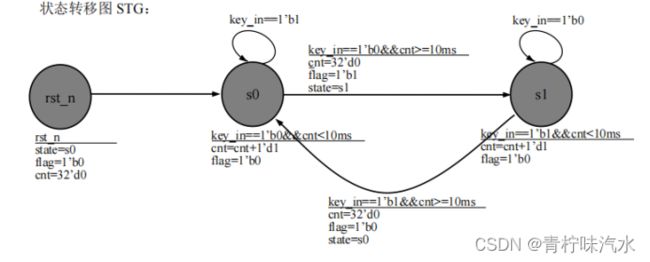

1、按键消抖

目的:避免在按下按键瞬间产生的一系列抖动由此引发按键开关在闭合时不会马上稳定、断开时不会马上断开的现象。

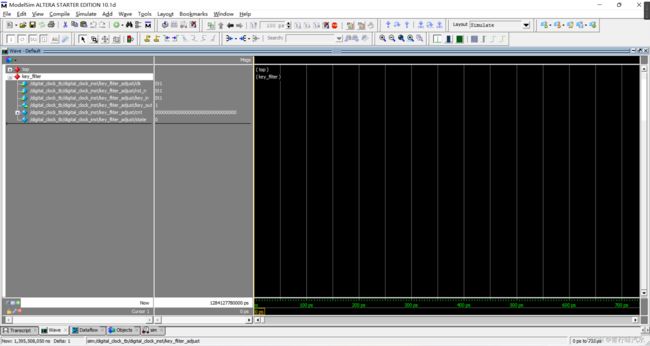

按键消抖时序仿真及分析:

状态机

2、按键的边沿检测

目的:检测输入信号,输入01上升沿,输入10为下降沿

时序仿真:

2.2数字钟逻辑控制

1、逻辑控制模块(logic_ctrl)

统筹按键按下后的基本逻辑功能以及数码管出现的相应现象

5、二进制转BCD(bin_bcd )

该模块用于对编码信息的译码工作,通过二进制转码从而使数码管显示相应的数字。

7、分钟闪烁模块(min_adjust)

2.3数码管显示驱动

1、设计框架

2、仿真测试

三、系统调试

1.Modelsim仿真及下板结果

仿真过程由于用到的代码较多需对每个模块创建一个group

把顶层文件设为TOP组

然后在左下找到sim点开

在这里里面一共有8个模块

右击Add Wave

然后回到Wave里面将这个模块分组

剩余模块重复此操作

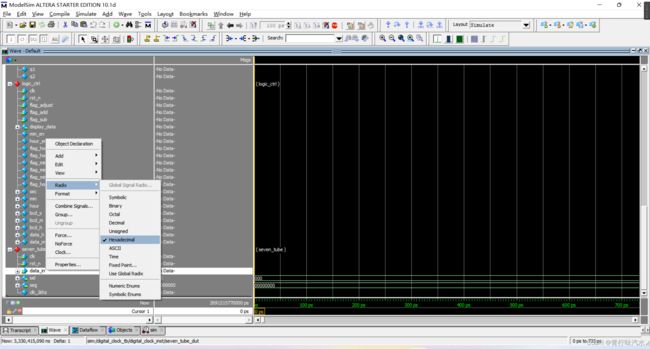

在填入所有模块后还有最重要的一步调试

调整sec位置,并将选中的三个设置成无符号数

data_in改为十六进制

最后得到以下图

仿真分析主要图过adjust按下对应功能闪烁达到预设目的就行

顶层设计代码如下:

module digital_clock(

input clk,

input rst_n,

input key_adjust,

input key_add,

input key_sub,

output [2:0] sel,

output [7:0] seg

);

wire key_adjust_out;

wire key_add_out;

wire key_sub_out;

wire flag_adjust;

wire flag_add;

wire flag_sub;

wire [23:0]display_data;

key_fliter #(.T10ms(4)) key_fliter_adjust(

.clk(clk),

.rst_n(rst_n),

.key_in(key_adjust),

.key_out(key_adjust_out)

);

key_fliter #(.T10ms(4)) key_fliter_add(

.clk(clk),

.rst_n(rst_n),

.key_in(key_add),

.key_out(key_add_out)

);

key_fliter #(.T10ms(4)) key_fliter_sub(

.clk(clk),

.rst_n(rst_n),

.key_in(key_sub),

.key_out(key_sub_out)

);

check_edge check_edge_adjust(

.clk(clk),

.rst_n(rst_n),

.signal(key_adjust_out),

.pos_edge(flag_adjust),

.neg_edge()

);

check_edge check_edge_add(

.clk(clk),

.rst_n(rst_n),

.signal(key_add_out),

.pos_edge(flag_add),

.neg_edge()

);

check_edge check_edge_sub(

.clk(clk),

.rst_n(rst_n),

.signal(key_sub_out),

.pos_edge(flag_sub),

.neg_edge()

);

clk_logic_ctrl clk_logic_ctrl_dut(

.clk(clk),

.rst_n(rst_n),

.flag_adjust(flag_adjust),

.flag_add(flag_add),

.flag_sub(flag_sub),

.display_data(display_data)

);

seven_tube seven_tube_dut(

.clk(clk),

.rst_n(rst_n),

.data_in(display_data),

.sel(sel),

.seg(seg)

);

endmodule

结语

这个项目是学校和企业合作带着我们做的一个项目,对PFGA有兴趣或者想要源码和设计报告的小伙伴可以私聊,我们可以一起学习。