计算机组成原理课程设计-基本模型机的设计与实现

基本模型机的设计与实现

设计目的

1、 综合运用所学计算机组成原理知识,在掌握部件单元电路实验的基础上,进一步将其组成系统构造一台基本的模型计算机.

2、 通过一台模型机的设计过程,明确计算机的控制原理与控制过程,巩固和灵活应用所学的理论知识,掌握计算机组成的一般设计方法,提高学生设计能力和实践操作技能,为从事计算机研制与设计打下基础。

3、 掌握整机概念,并设计机器指令系统,编写相应的微程序,在所设计的模型计算机上调试运行。

实验设备

Dais-CMX16+ 计算机组成原理教学实验系统一台。

设计分析

实验原理

本实验将能在微程序控制下自动产生各部件单元的控制信号,实现特定指令的功能。这里,计算机数据通路的控制将由微程序控制器来完成,CPU从EM主存中取出一条机器指令到指令执行结束的一个指令周期全部由微指令组成的序列来完成,即一条机器指令对应一个微程序。

机器指令格式

表1 指令格式

| 7 6 5 |

4 |

3 2 |

1 0 |

| OP-CODE |

0 |

Rs |

Rd |

| Addr |

|||

| Rs或Rd |

选定的寄存器 |

| 00 01 10 11 |

R0 R1 R2 R3 |

微指令格式

按照系统建议的微指令格式,参照微指令流程图,将每条微指令代码化,译成二进制代码表,并将二进制代码表转换成十六进制格式文件,如表3所示。表3 微指令格式

| M23 |

M22 |

M21 |

M20 |

M19 |

M18 |

M17 |

M16 |

M15 |

M14 |

M13 |

M12 |

M11 |

M10 |

M9 |

M8 |

M7 |

M6 |

M5 |

M4 |

M3 |

M2 |

M1 |

M0 |

| E/M |

IP |

MWR |

R/M |

目的编码 |

OP |

M |

CN |

S2 |

S1 |

S0 |

源编码 |

XP |

W |

ALU |

Iu |

IE |

IR |

Icz |

Ids |

||||

表4 源编码与目的编码指令格式

| 源编码 |

|

目的编码 |

||||||

| M10 |

M9 |

M8 |

功能 |

M19 |

M18 |

M17 |

功能 |

|

| X2 |

X1 |

X0 |

O2 |

O1 |

O0 |

|||

| 1 |

1 |

1 |

禁止 |

1 |

1 |

1 |

禁止 |

|

| 1 |

1 |

0 |

ALU |

1 |

1 |

0 |

MAR |

|

| 1 |

0 |

1 |

SP |

1 |

0 |

1 |

BX |

|

| 1 |

0 |

0 |

IOR |

1 |

0 |

0 |

AX |

|

| 0 |

1 |

1 |

MRD |

0 |

1 |

1 |

SP |

|

| 0 |

1 |

0 |

XRD |

0 |

1 |

0 |

IOW |

|

| 0 |

0 |

1 |

RRD |

0 |

0 |

1 |

XWR |

|

| 0 |

0 |

0 |

PC |

0 |

0 |

0 |

RWR |

|

指令程序设计

指令系统

本实验设计了八条机器指令:IN(输入)、ADD(二进制加法)、SUB(二进制减法)、STA(存数)、OUT(输出)、MOV(传送)、RR(循环右移)、JMP(无条件转移)。

| 助记符 |

机器指令码 |

说明 |

| IN RO,IOL |

00100000 |

I/O(数据开关)偶字节→R0 |

| ADD R0,[addr] |

00000000 XXXXXXXX XXXXXXXX |

R0+[addr] →R0 |

| SUB R0,[addr] |

00000000 XXXXXXXX XXXXXXXX |

R0-[addr] →R0 |

| STA [addr],R0 |

01100000 XXXXXXXX XXXXXXXX |

R0→[addr]1 |

| OUT IOH,[addr] |

10001000 XXXXXXXX XXXXXXXX |

RAM→I/O(奇字节) |

| MOV SP,[addr] |

11100000 XXXXXXXX XXXXXXXX |

[addr] →SP |

| RR R0 |

11000000 |

R0循环右移一位 |

| JMP * |

10100000 XXXXXXXX XXXXXXXX |

addr→PC |

其中IN为单字节(8位)指令,其余为三字节指令,XXXXXXXXXXXXXXXX为addr对应的二进制地址码,XXXXXXXX为立即数。

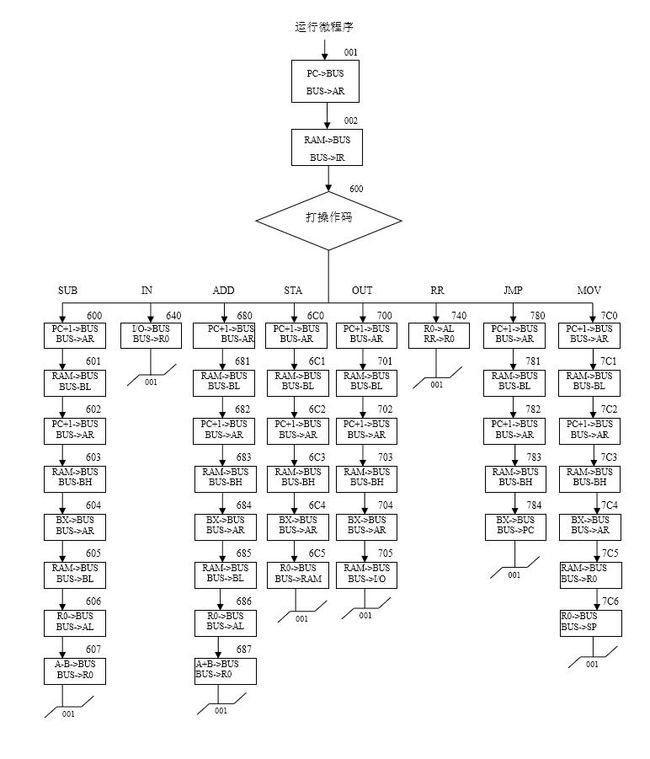

指令流程图

源程序

#LOAD "DEMO.IS" ;预调入指令系统/微程序

#SET RAM 0260h = 1100h ;数据区0260H单元预置数据1100h

#SET RAM 0120h = 2200h

data segment ;将程序装载到数据存储器

assume ds:data

org 0

start: in r0, iol;将IO低位送至R0寄存器

add r0, 0260h;将R0的内容与内存0260单元的内容相加,送回R0

sub r0, 0120h;将R0的内容与内存0260单元的内容相减,送回R0

sta 0261h, r0;将0261单元的内容载入到RAM中

out ioh, 0261h;将内存0261单元的内容输出到IO高位

mov sp,0260h;将内存0260单元的内容传送到SP寄存器

rr r0;将R0寄存器的内容循环右移一位

jmp 0000;将PC的内容置零,返回第一条机器指令

data ends

end start

微程序控制实现过程

所用的机器指令程序

| 地址 |

指令代码 |

助记符 |

功能 |

| 000 |

00 60 02 |

SUB R0,[ADDR] |

R0-RAM→R0 |

| 003 |

20 |

IN R0,IOL |

I/O(数据开关)偶字节 |

| 004 |

40 60 02 |

ADD R0,[ADDR] |

R0+RAM→R0 |

| 007 |

60 61 02 |

STA [ADDR],R0 |

R0→RAM |

| 00A |

80 61 02 |

OUT [ADDR],IOH |

RAM→I/O(奇字节) |

| 00D |

A0 02 02 |

RR R0 |

R0右移→R0 |

| 010 |

C0 00 00 |

JMP 0000H |

RAM→PC |

| 013 |

E0 02 |

MOV R0,SP |

R0→SP |

基本模型机微指令表

由于表格数据太多无法并列列举所以基本模型机微指令表将由表7-1、表7-2、表7-3三个表进行表示。表7-1 M23-M16指令集

| 微地址 |

M23 |

M22 |

M21 |

M20 |

M19 |

M18 |

M17 |

M16 |

代码 |

| E/M |

IP |

MWR |

R/M |

o2 |

o1 |

o0 |

OP |

||

| 000 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

FF |

| 001 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

FC |

| 002 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

7F |

| 600 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

BC |

| 601 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

7A |

| 602 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

BC |

| 603 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

7B |

| 604 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

BC |

| 605 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

7A |

| 606 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

| 607 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

F1 |

| 640 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

B1 |

| 680 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

BC |

| 681 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

7A |

| 682 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

BC |

| 683 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

7B |

| 684 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

BC |

| 685 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

7A |

| 686 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

| 687 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

F1 |

| 6C0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

BC |

| 6C1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

7A |

| 6C2 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

BC |

| 6C3 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

7B |

| 6C4 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

BC |

| 6C5 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

5F |

| 700 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

BC |

| 701 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

7A |

| 702 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

BC |

| 703 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

7B |

| 704 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

BC |

| 705 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

75 |

| 740 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

| 741 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

B1 |

| 780 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

BC |

| 781 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

7A |

| 782 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

BC |

| 783 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

7B |

| 784 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

3F |

| 7C0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

BC |

| 7C1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

7A |

| 7C2 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

BC |

| 7C3 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

7B |

| 7C4 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

BC |

| 7C5 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

70 |

| 7C6 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

F6 |

表7-2 M15-M8指令集

| 微地址 |

M15 |

M14 |

M13 |

M12 |

M11 |

M10 |

M9 |

M8 |

代码 |

| M |

CN |

S2 |

S1 |

S0 |

X2 |

X1 |

X0 |

||

| 000 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

FF |

| 001 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

| 002 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

| 600 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

| 601 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

| 602 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

| 603 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

| 604 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

C6 |

| 605 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

| 606 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

F9 |

| 607 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

6E |

| 640 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

FC |

| 680 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

| 681 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

| 682 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

| 683 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

| 684 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

C6 |

| 685 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

| 686 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

F9 |

| 687 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

66 |

| 6C0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

| 6C1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

| 6C2 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

| 6C3 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

| 6C4 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

C6 |

| 6C5 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

F9 |

| 700 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

| 701 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

| 702 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

| 703 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

| 704 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

C6 |

| 705 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

| 740 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

F9 |

| 741 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

7E |

| 780 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

| 781 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

| 782 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

| 783 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

| 784 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

C6 |

| 7C0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

| 7C1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

| 7C2 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

F8 |

| 7C3 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

| 7C4 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

C6 |

| 7C5 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

FB |

| 7C6 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

F9 |

表7-3 M7-M0指令集

| 微地址 |

M7 |

M6 |

M5 |

M4 |

M3 |

M2 |

M1 |

M0 |

代码 |

| XP |

W |

ALU |

Iu |

IE |

IR |

Icz |

Ids |

||

| 000 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

FF |

| 001 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

3F |

| 002 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

FA |

| 600 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

3F |

| 601 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

DF |

| 602 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1F |

| 603 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

DF |

| 604 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1F |

| 605 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

DF |

| 606 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

DF |

| 607 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

4D |

| 640 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

6D |

| 680 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

3F |

| 681 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

DF |

| 682 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1F |

| 683 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

DF |

| 684 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1F |

| 685 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

DF |

| 686 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

DF |

| 687 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

4D |

| 6C0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

3F |

| 6C1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

DF |

| 6C2 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1F |

| 6C3 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

DF |

| 6C4 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1F |

| 6C5 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

ED |

| 700 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

3F |

| 701 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

DF |

| 702 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1F |

| 703 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

DF |

| 704 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1F |

| 705 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

ED |

| 740 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

DF |

| 741 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

4D |

| 780 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

3F |

| 781 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

DF |

| 782 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1F |

| 783 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

DF |

| 784 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0D |

| 7C0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

3F |

| 7C1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

DF |

| 7C2 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1F |

| 7C3 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

DF |

| 7C4 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1F |

| 7C5 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

DF |

| 7C6 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

6D |

调试过程

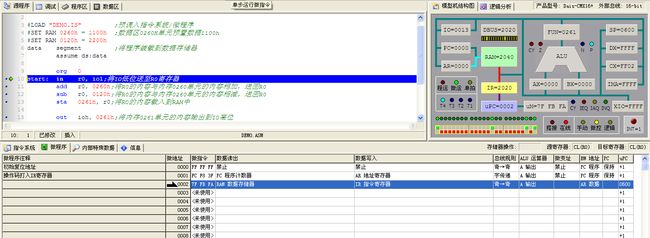

该基本模型机运行如下图2-0至图2-1所示。

图2-1初始化

IN RO,IOL

图2-2IN指令

ADD R0,[addr]

图2-3ADD指令

SUB R0,[addr]

图2-4SUB指令

STA [addr],R0

图2-5STA指令

OUT IOH,[addr]

图2-6OUT指令

MOV SP,[addr]

图2-7MOV指令

RR R0

图2-8RR指令

JMP *

图2-9JMP指令

结果分析

该基本模型机运行的结果如表8所示。

表8 运行结果

| 助记符 |

结果 |

| IN RO,IOL |

R0=13 |

| ADD R0,0260h |

R0=24 |

| SUB R0,0260h |

R0=02 |

| STA 0261h,R0 |

RAM=1102 |

| OUT IOH,0261h |

IOH=02 |

| MOV SP,0260h |

SP=11 |

| RR R0 |

R0=88 |

| JMP 0000 |

μpc=0001 |