使用专用硬件加速深度卷积神经网络

英文论文链接:http://research.microsoft.com/apps/pubs/default.aspx?id=240715

翻译:卜居

转载请注明出处:http://blog.csdn.net/kkk584520/article/details/47711755

【摘要】

最近在多层卷积神经网络的突破导致了识别任务(如大量图片分类和自动语音识别)准确率的大幅提升【1】。这些多层神经网络很大,很复杂,需要大量计算资源来训练和评估【2】。然而这些需求发生在目前这样一个尴尬的时刻,商业处理器性能增长十分缓慢。

专用硬件形式有GPGPU,FPGA和ASIC,提供了通往处理能力和高能效的坦途。微软通过使用FPGA增强型服务器(类似已经集成到微软数据中心的硬件【3】)加速深度卷积神经网络驾驭了专用硬件。

开始只是在中等规模FPGA上实现了单节点CNN加速器,展示了优于遗忘FPGA设计和高端GPGPU的性能,降低了功耗。未来会通过低延迟通信互联多个FPGA,进一步可能训练和评估模型。

【背景】

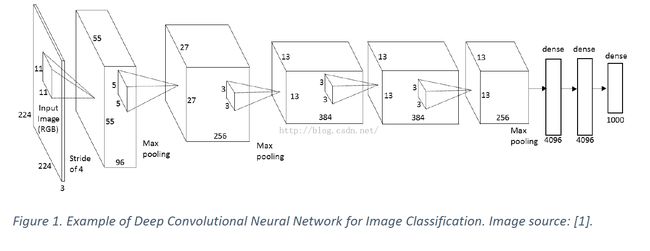

目前深度卷积神经网络一般组织为交替的卷积层、最大池化层后面加一系列稠密的全连接层,如图1中经典的拓扑图所示。

每个3D立方体表示一层的输入,送入下一层会变换为新3D立方体。在例子中有5个卷积层,3个最大池化层,以及3个全连接层。

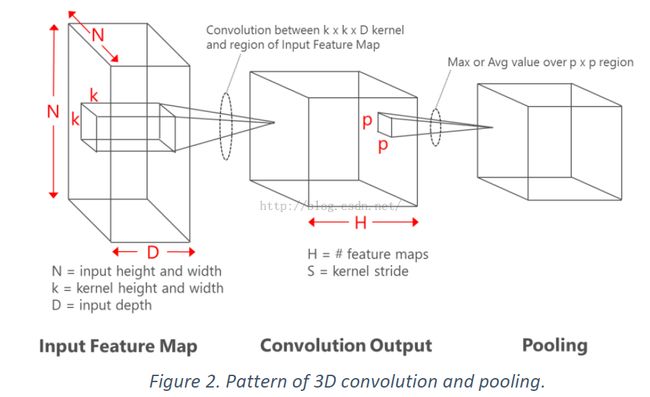

本文中我们主要讨论3D卷积问题,尽管其他操作如pooling和全连接层也会涉及。图2展示了3D卷积的基本模型。一个N x N x D的3D输入立方体被H个k x k x D维的卷积核卷积,输出间隔为S,每个3D核用类似滑动窗口的形式移动(移动偏移量由参数S定义)。每次移动,3D卷积核的每个权值同映射到3D输入立方体的输入值进行乘加,卷积后,可选地进行pooling操作(由参数p和s定义)用来下采样卷积输出,选择窗口的最大值或平均值

【在数据中心加速深度卷积神经网络】

2014年微软宣布了Catapult项目,成功展示了用FPGA在数据中心使Bing Ranking加速了近2倍【3】。利用这个基础,我们团队在微软研究院开发了高吞吐CNN FPGA加速器,在很低的服务器功耗下获得了优异性能。图3给出了用于高效计算卷积层前向传播的CNN FPGA加速器高层次概览。

关键特征如下:

(1)软件可配置的引擎,支持多层运行时配置(无需硬件重编程);

(2)高效数据缓冲体制和片上分发网络,将片外访存降至最低;

(3)处理单元(PE)构成的空间分布阵列,可很容易扩展到上千个单元;

在正常操作下,CNN加速器可以获取输入图像,连续处理多个卷积层。在初始阶段,输入图像像素从本地DRAM流入片上,存储到多个bank输入缓冲区。之后,数据流入多个PE阵列,实现3D卷积步骤中的独立点乘操作。顶层控制器完成序列化、寻址、分发数据到每个PE阵列。最终,累加结果发送到特定片上网络,将计算输出循环送入输入缓冲区用于下一轮的计算(虽然图3中没有显示,但存在额外的逻辑处理pooling和ReLU操作)。

图3中高亮的加速器位于双插槽Xeon服务器,装备一个Catapult FPGA卡,包括中等规模Stratix D5 FPGA和8GB DDR3-1333[3]。每个FPGA卡通过PCIe 3x8支持高达8GB/s带宽,同时本地DRAM支持21.3GB/s带宽。更多硬件描述可参考Catapult论文【3】。

表1显示了使用著名模型(如基于cuda-convnet【4】的CIFAR-10,基于Alex的ImageNet-1K【1】等)进行图像分类(只有前向传播过程)的吞吐情况。我们进一步评估了最大的和最具挑战性的模型:ImageNet-22K,在微软ADAM项目中训练的DCNN【2】。

总体上看,我们目前在装备中等规模Stratix V D5 FPGA的Catapult服务器上获得了最高处理吞吐。相比最近发表的FPGA实现【5】和运行在高端GPGPU上的Caffe+cuDNN【6】。注意GPGPU解决方案需要高达235W功耗【7】,使得部署到功耗限制的数据中心不太现实。相反,FPGA解决方案功耗不超过25W,占整个服务器功耗的不到10%。我们的实现获得了近3倍加速,相对最近发表的利用Virtex 7 485T FPGA的CNN加速器【5】。

(卜居注:【5】只说了处理能力达到61.62GFLOPS,并没有说处理图片速度,这篇文章怎么算的?)

我们参数化的CNN加速器可灵活扩展到更新和更快的FPGA。我们团队正在将设计移植到Altera的最新Arria 10 FPGA上,提供了对浮点处理支持,可以在高能效情况下达到1TFLOPS处理能力【8】。表1列出了我们的预期性能。

总而言之,本文描述了使用FPGA加速深度卷积神经网络的研究。前期结果是很有希望的,显示出专用硬件具有低功耗、高性能的优势。未来我们希望在Arria 10和Stratix 10上设计更高性能的加速器,并考虑多片互联并行训练和评估。