《大话处理器》连载——微架构(12) 指令的相关

相关是影响乱序调度的罪魁祸首,如果指令2的执行需要依赖指令1的结果,我们就说这2条指令是相关的,指令2必须在指令1后面执行,无法乱序。

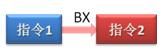

下图描述了指令间的相关性:

指令的相关性

(1) 寄存器相关

当2条语句没有共用寄存器时,它们之间是不相关的,而当2条语句共用寄存器时,它们就有可能相关。

我们以x86汇编来看看指令间的相关性。

1. 先读后读

|

ADD BX, AX ;将AX和BX相加,存放到BX中 (前面的寄存器为目的寄存器) ADD CX, AX ;将AX和CX相加,存放到CX中 |

这2条指令实际上是没有相关性的,调转一下执行顺序,对结果没有影响。

2. 先写后读(Read-After-Write,RAW)

|

ADD BX, AX ;将AX和BX相加,存放到BX中 ADD CX, BX ;将BX和CX相加,存放到CX中 |

这2条指令都用到BX,指令1输出BX给指令2用,它们之间有数据流动,存在依赖性,因此也称为数据相关。

数据相关示例

3. 先读后写(Write -After- Read,WAR)

|

ADD BX, AX ;将AX和BX相加,存放到BX中 MOV AX, CX ;将CX的值赋给AX |

这2条指令都用到AX,指令1读AX,指令2写AX,如果直接将2条语句调转,执行结果自然是不一样的,因此它们具有相关性。不过如果仔细分析一下,这2条语句之间并没有数据流向,在逻辑上并没有相关性,引起它们相关性的原因在于:x86处理器对程序员可见的通用寄存器太少了,指令不得不共用寄存器,这样才导致指令间存在相关。WAR和RAW相反,因此这种相关也称为反相关(Anti Dependencies)。

4. 先写后写(Write -After- Write,WAW)

|

MOV AX, BX ;将BX的值赋给AX MOV AX, CX ;将CX的值赋给AX |

这两条指令都向AX中写,和WAR一样,WAW 的2条指令间也没有数据流动,它们的相关是因为有相同的输出寄存器,因此被称为输出相关(Output Dependencies)。

WAR和WAW没有逻辑上的相关性,只是由于共用了同一个寄存器而存在相关性,它们被称为伪相关(False Dependencies)或者名字相关(Name Dependencies)。

(2) 控制相关

程序中有很多条件跳转,如下面这个例子:

|

MOV CMP JNZ label ADD …… label:XOR |

JNZ是个条件跳转语句,XOR指令的执行需要依赖于JNZ的结果,这种相关性是由指令的控制流决定的,因此被称为控制相关。