七、mini2440裸机程序之定时器中断(2)时钟相关寄存器配置

1.相关寄存器介绍

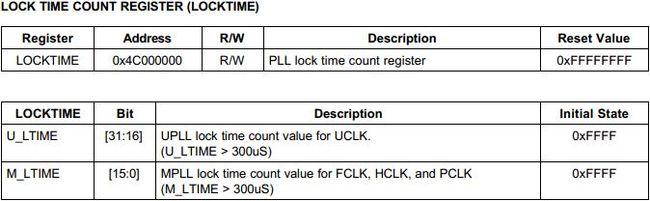

1)LOCKTIME

注:

这个寄存器主要是用于设置upll和mpll 的锁紧时间计数值 ,

一般使用默认值最保险了.

2)MPLLCON和UPLLCON

注:

①Mpll = ( 2*(MDIV+8)*Fin ) / ( (PDIV+2)*(2^SDIV) )

②Upll = ((MDIV+8)*Fin ) / ( (PDIV+2)*(2^SDIV) )

③600MHz<=(2*(MDIV+8)*Fin / (PDIV+2) ) <= 1.2GHz

④200MHz<=(2*(MDIV+8)*Fin / ( (PDIV+2) * 2^SDIV) ) <= 600MHz

⑤1<=(PDIV+2)<=62 , 1<=(MDIV+8)<=248

⑥MDIV和PDIV都不能为0 .

手册已经帮我们准备好了一些设置值, 可以从下表来选择合适的设置值:

注:

对于UPLL来说 : MDIV =0x38 , PDIV = 2 , SDIV = 1. 这样从UPLL倍频出来的频率就能被设置为96.00MHz.

对于MPLL来说 因为mini2440使用的是12MHz的输入频率 , 我们选择输出频率为405MHz就行 所以 : MDIV = 0x7f , PDIV = 2 , SDIV = 1 .

这样从MPLL倍频出来的频率就为405MHz了 .

综上所述 , MPLLCON和UPLLCON的配置如下:(这两个值即使使用默认值也要写入相同值)

UPLLCON = (0x38<<12)|(0x02<<4)|(0x01<<0);(这个寄存器要在设置MPLLCON前设置,并且需要间隔大约7个NOP)

MPLLCON = (0x7f<<12)|(0x02<<4)|(0x01<<0) ;

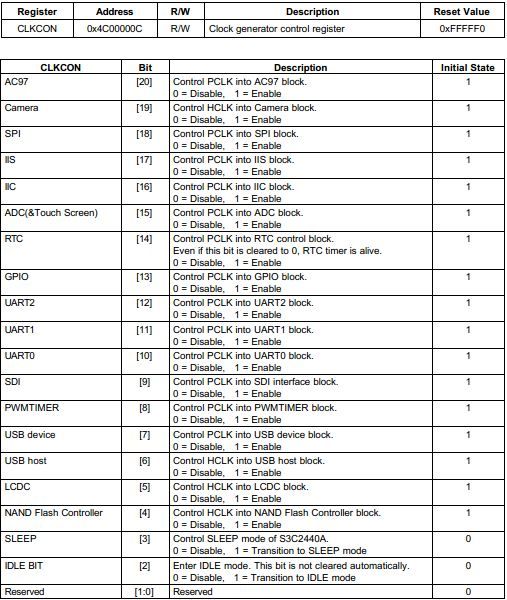

3)CLKCON

注:

这个寄存器用来禁止和使能外设时钟和模式的选择 .

采用默认值就行

4)CLKSLOW

注:

这个寄存器暂时不会被用到

5)CLKDIVN

注:

关于FCLK:HCLK:PCLK的分频比选择 1:4:4 也就是FCLK=405MHz , HCLK=101.25MHz , PCLK=101.25MHz (在上一篇可知HDIVN=2,PDIVN=0,HCLK4_HALF/HCLK3_HALF=0/0)

因为之前选择UPLL时钟为96MHz , 所以DIVN_UPLL=1才能使UCLK为48MHz .

HDIVN = 10b , PDIVN = 0b

综上所述 , CLKDIVN的配置如下:

CLKDIVN =(1<<3)|(2<<1)|(0<<0)

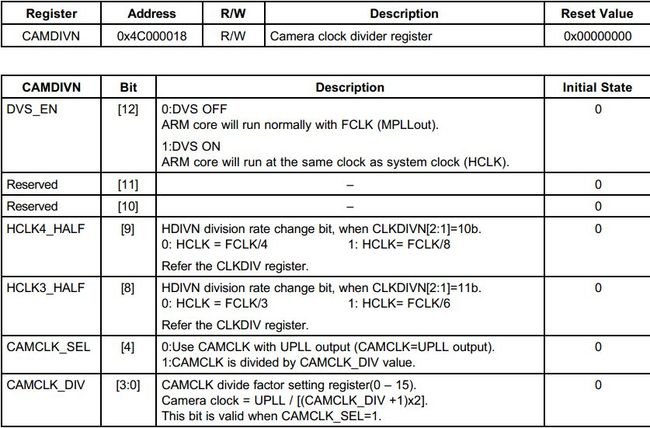

6)CAMDIVN

注:

这里只要把HCLK4_HALF/HCLK3_HALF=0/0就行了.

CANDIVN &= ~(0x03<<8);

7)假如HDIVN不是0 , CPU总线模式必须从高速总线模式改变为异步总线模式通过使用下面指令(S3C2440不支持同步总线模式):

关于这部分,主要涉及到arm920t里面的协处理器的寄存器1 :control register的第30~31位 , 如下所示:

所以里面第二句指令应该为:

Orr r0 , r0 , #0xC0000000