SPI

自己对LPC2131 SPI的总结归纳:

1、时钟极性选择位CPOL:决定SCK的有效位。当CPOL=0时,SCK高有效;当CPOL=1时,SCK低有效;

2、时钟相位选择位CPHA:决定操作的时间沿。所有情况的采样数据时刻为:CPHA=0时,SCK从Idle到Active沿(有效沿);CPHA=1时,SCK从Active到Idle沿(无效沿);

3、驱动第一个数据位:CPHA=0时,在第一个有效沿之前;CPHA=1时,在第一个无效沿(及第二个时钟沿)

驱动其他数据:均是在SCK从Active到Idle沿(无效沿)

----------------------------------------------------------------------

源:http://www.rd3721.com/tech/ShowInfo.asp?InfoID=491&Page=1

SPI 串行外设接口总线,最早由Motorola提出,。SPI接口是一种事实标准,并没有标准协议,大部分厂家都是参照Motorola的SPI接口定义来设计的。但正因为没有确切的版本协议,不同家产品的SPI接口在技术上存在一定的差别,容易引起歧义,有的甚至无法直接互连(需要软件进行必要的修改)。

SPI ( Serial Peripheral Interface )

SPI接口是Motorola 首先提出的全双工三线同步串行外围接口,采用主从模式(Master Slave)架构;支持多slave模式应用,一般仅支持单Master。

时钟由Master控制,在时钟移位脉冲下,数据按位传输,高位在前,低位在后(MSB first);SPI接口有2根单向数据线,为全双工通信,目前应用中的数据速率可达几Mbps的水平。

SPI接口信号线

SPI接口共有4根信号线,分别是:设备选择线、时钟线、串行输出数据线、串行输入数据线。

设备选择线SS-(Slave select,或CS-)

SS-线用于选择激活某Slave设备,低有效,由Master驱动输出。

SCLK:同步时钟信号线,

SCLK用来同步主从设备的数据传输,由Master驱动输出,Slave设备按SCK的步调接收或发送数据。

串行数据线:

SPI接口数据线是单向的,共有两根数据线,分别承担Master到Slave、Slave到Master的数据传输;但是不同厂家的数据线命名有差别。

Motorola的经典命名是MOSI和MISO,这是站在信号线的角度来命名的。

MOSI:When master, out line; when slave, in line

MISO:When master, in line; when slave, out line

比如MOSI,该线上数据一定是Master流向Slave的。因此在电路板上,Master的MOSI引脚应与Slave的MOSI引脚连接在一起。双方的MISO也应该连在一起,而不是一方的MOSI连接另一方的MISO。【232与与之不同,因没有主从】

不过,也有一些产家(比如Microchip)是按照类似SDI,SDO的方式来命名,这是站在器件的角度根据数据流向来定义的。

SDI:串行数据输入

SDO:串行数据输出

这种情况下,当Master与Slave连接时,就应该用一方的SDO连接另一个方的SDI。

由于SPI接口数据线是单向的,故电路设计时,数据线连接一定要正确,必然是一方的输出连接另一方的输入。

数据传输的时序模式

为了适用不同产品接口应用需要,SPI接口定义了多种时序传输模式,并可通过设置接口单元寄存器中的相关控制位来选择。在Motorola的产品中,时序即是由两个控制位(极性控制、相位控制)来控制的。

时钟极性选择位CPOL:

在设备被使能激活后,还未进行数据传输时或两个字节数据传输间歇期间(见图3中的○1与○2处),SCLK处于空闲(Idle)电平,通过"CPOL空闲状态极性控制位"可以选择此空闲电平电平是0还是1。

时钟相位选择位CPHA:

该控制位用来选择数据接收端设备的采样时刻。可能在Idle to Active的跳变沿(见图3中的红色圈处),也可能在Active to Idle的跳变沿(见图3中的蓝色圈处)。在该采样时刻,线上数据必须已经稳定可靠,因此数据发送端设备应提前将数据移出到数据线上。为了降低设计难度,大部分接口电路都是用同一时钟周期中前一个时钟沿(即相反时钟变化方向)将数据移出。

SPI线上的Master,Slave设备必须根据具体情况设置匹配的传输时序模式,时序只有匹配,数据传输才能正常进行。如果设置的不匹配,可能导致数据接收方和发送方在同一时钟沿作用,导致数据传输失败。

我们以手机设计中非常流行的触摸屏控制器TSC2046为例,介绍SPI接口的实际应用。

由于TSC2046采样触摸屏信息并量化出最高位需要一定时间,而SPI总线没有握手机制,为避免Master过早的启动传输,接收无效数据,TSC2046引入了BUSY信号作为TSC2046向Master的指示。

TSC2046是在时钟的第一个Idle to Active沿采集数据(下图1处),而在第一个(下一字节)Active to Idle 沿开始移出数据(下图2处),这导致Master只能在第二个dle to Active沿采集到的数据才是有效的(下图3处),而在第一个Idle to Active沿(下图1处)采集的数据是无效的,因此在软件中需要将该Bit丢弃。

可见,必须根据Master与Slave的实际时序进行匹配,软件也需要进行对应的调整,才能保证数据传输的正常进行。

多Slave的应用

SPI也支持多Slave应用。多个Slave共享时钟线、数据线,可以直接并接在一起;而各Slave的片选线SS则单独与Master连接,受Master控制。在一段时间内,Master只能通过某根SS线激活一个Slave,进行数据传输,而此时其他Slave的时钟线和数据线端口则都应保持高阻状态,以免影响当前数据传输的进行。

SPI Vs I2C

SPI协议没有定义寻址机制,需通过外部SS信号线选择设备,当出现多slave应用时,需要多根SS信号线,实施起来较I2C要复杂。此外,SPI总线不支持总线控制权仲裁,故只能用在单Master的场合;而I2C可以支持多Master的应用。

SPI 协议相对I2C要简单,没有握手机制,数据传输效率高,速率也更快,通常应用中可达几Mbps;此外SPI是全双工通信,可同时发送和接收数据,因此,SPI比较适合用于数据传输的场合。比如需要较大批量数据传输的场合(比如MMC/SD卡的数据传输就支持SPI模式),或者无需寻址传输的场合。

而I2C协议功能较丰富,但也相对复杂,多用在传输一些控制命令字等有意义数据的场合。

比如TSC2046只有一个控制寄存器(一个8bit的命令字),使用SPI接口即可控制,因为无需寻址。而OV的Cmos Sensor内有多个控制寄存器,此时就必须使用I2C接口才能实现寻址控制(哦,确切的是SCCB,一个很像I2C的东东)。

SPI接口属于一种非常基本的外设接口,但是应用却很广泛。SPI也有所发展,比兔NS推出的SPI的精简接口Microwire,满足通常外设的扩展需求。Motorola还推出了扩展功能的QSPI(Queued SPI)接口,应用更为广泛。

---------------------------------------------------------------------

源:http://www.52rd.com/Blog/Detail_RD.Blog_wenqing1025_11280.html

1 SPI通信

SPI信号线:一般的SPI接口使用4条信号线与外围设备接口,其具体功能如下:

- SCLOCK: 主机的时钟线,为数据的发送和接收提供同步时钟信号。每一位数据的传输都需要1次时钟作用, 因而发送或接收1个字节的数据都需要8个时钟作用。主机的时钟可以通过固件进行设置,并和从机的时钟线相连。

- MISO:主机输入/从机输出数据线。主机的MOSO应与从机的发送数据端相连,进行高位在前的数据交换。

- SS:低电平有效的从机选择线。当该线置低时,才能跟从机进行通信。

SPI工作模式:SPI的工作模式分为:主模式和从模式。

- 主模式的特点是不论发送还是接收始终有SCLOCK信号,SS信号不是必需的, 由于SPI只能有一个主机, 因而不存在主机的选择问题。

- 从模式的特点是无论发送还是接收必须在时钟信号SCLOCK的作用下才能进行,并且SS信号必须有效。

不论是在主模式下还是在从模式下,都要在时钟极性和时钟相位的配合下才能有效的完成一次数据传输。

2 SPI接口的单线应用

在标准的SPI接口间进行通信时,SPI总线的四条信号线中: 主机SCLOCK与从机SCLOCK相连; 主机MISO与从机MOSI相连;主机MOSI与从机MISO 相连; 主机控制信号线与从机的SS相连。在SPI接口与非标准接口进行通信时,例如与有的串行RAM 接口,由于双向I/O数据线只有一条,时钟和片选信号线都有,那么如何利用SPI的高速特性进行数据的读出和写入呢?

在这里提出SPI的单线应用方案,其如图1所示。主机的时钟信号SCLOCK 和片选信号SS与从机的对应信号线相连, 不同的是主机的MOSI和MISO信号线分别经过合适的电阻与从机的I/O信号线相连。当主机给从机发送数据时,在时钟信号的作用下,数据从MOSI口线经电阻1到从机的I/O 口线;当主机接收数据时,也需要在时钟信号的作用下,数据从从机的I/O口线经电阻2到主机的MISO口线。该方案中MOSI与MISO连在一起, 由于加了适当的电阻,所以不违反电路设计原则,但如果电阻大小不当会对信号的特性带来影响 。

图1 SPI单线应用方案

3 SPI接口的单线应用举例

本例是作者设计的单片机,ADuC812的SPI总线与射频无线通信模块nRF2401间的通信接口,由于nRF2401只支持I/O数据传输方式,但是为了提高无线通信的数据速率,作者采用单线方式实现了SPI与nRF2401的通信。

电路设计

ADuC812的SPI与nRF2401的连接原理如图2所示。其中ADuC812作为主机,nRF2401作为从机,PWR、CE、CS是nRF2401的工作模式选择信号,他们共同完成从机的片选任务,相当于SS信号。CLK1是ADuC812串行时钟信号。根据信号阻抗匹配原则,通信中选用两个6K 的电阻。ADuC812单片机的SPI接口由SPICON (SPI控制寄存器)、SPIDAT (SPI数据寄存器)来控制, 通过设定SPICON 寄存器的各位实现SPI的各种工作模式。

图2 ADuC812的SPI与nRF2401的连接原理

控制寄存器SPICON中从高到低各位说明如下:

- ISPI: 中断标志位。当发送或接收1字节数据完毕时自动置1.当执行中断服务程序时,硬件自动清除该位。该位也可以通过软件控制。

- WCOL:写冲突错误标志位。

- SPE:SPI使能位。若SPE=0,则I2C串行口工作;若SPE=1,则SPI串行口工作。

- SPIM:主模式选择位。若SPIM=0,则SPI工作于从模式;若SPIM=1,则SPI工作于主模式。

- CPOL:时钟极性选择位。CPOL=0,在主机时钟下降沿时读取数据,各数据字节之间传输时,时钟处于高电平空闲状态;CPOL=1,在主机时钟上升沿时读取数据,各数据字节之间传输时,时钟处于低电平空闲状态。

- CPHA;时钟相位选择位。CPHA=0,传输数据的最高位在SS的下降沿出现,在时钟第1个前沿读入,之后的下一个数据位在时钟后沿出现,

在下一个前沿读入,直到8位数据读完;CPHA=1,传输数据在时钟前沿出现,在同一时钟周期的后沿读入。 - SPR1、SPR0:SPI波特率选择位。

接口程序设计 固件程序主要包括:SPI口初始化程序INITSPI,送数据程序SENDDATA,接收数据程RECEIVEDATA。

在SPI初始化程序中,控制寄存器SPICON设置为33H, 即CPOL=0,CPHA=0, 当设置CPOL= 1,CPHA=1时, 由于干扰脉冲的存在,ADuC812与NRF2401不能很好的同步。

在发送数据子程序中,向数据寄存器SPIDAT写数据,如产生中断标志,说明数据传输完毕,则可以发送下一个数据。

在接收子程序中, 由于nRF2401送数据的时钟是由ADuC812的SCLOCK 产生的, 所以执行接收数据指令MOVA,SPIDAT时先要对数据寄存器SPIDAT 写数据0,也就是执行指令MOVA,SPIDAT,其目的是为了产生接收数据时的时钟信号, 当单片机向SPIDAT 写数据0时,nRF2401通过DATA 口向单片机送数据,改写SPIDAT 的内容,这就是所接收的数据。

SPI单线方案在实际应用应注意以下问题:

(1)时钟相位与时钟极性的设置。其设置要跟从机的数据读写时序相一致, 在一致时也要注意干扰问题。

(2)所加电阻值的大小。阻值的大小关系到信号传输的阻抗匹配问题,同时也影响数据传输的速率,所以在选用电阻时一般取几K 的电阻。

--------------------------------------------------------------

http://hi.baidu.com/chinaunion/blog/item/604065605befdf42eaf8f823.html

在SPI传输中,数据是同步进行发送和接收的。数据传输的时钟基于来自主处理器的时钟脉冲,摩托罗拉没有定义任何通用SPI的时钟规范。然而,最常用的时钟设置基于时钟极性(CPOL)和时钟相位(CPHA)两个参数,CPOL定义SPI串行时钟的活动状态,而CPHA定义相对于SO-数据位的时钟相位。CPOL和CPHA的设置决定了数据取样的时钟沿。

数据方向和通信速度

SPI传输串行数据时首先传输最高位。波特率可以高达5Mbps,具体速度大小取决于SPI硬件。例如,Xicor公司的SPI串行器件传输速度能达到5MHz。

SPI总线接口及时序

SPI总线包括1根串行同步时钟信号线以及2根数据线。

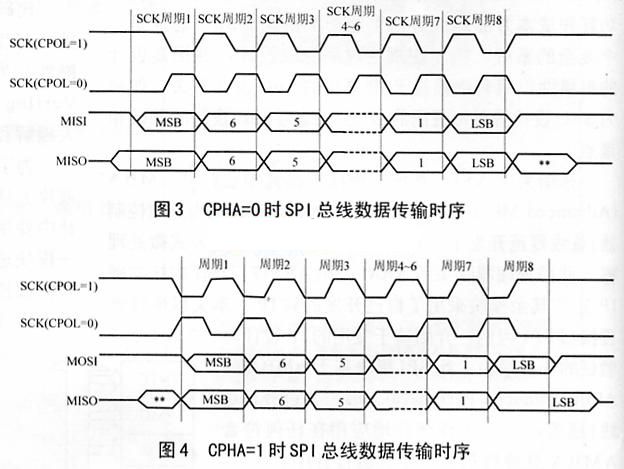

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。SPI主模块和与之通信的外设应时钟相位和极性应该一致。SPI接口时序如图3、图4所示。

SPI是一个环形总线结构,由ss(cs)、sck、sdi、sdo构成,其时序其实很简单,主要是在sck的控制下,两个双向移位寄存器进行数据交换。

假设下面的8位寄存器装的是待发送的数据10101010,上升沿发送、下降沿接收、高位先发送。

那么第一个上升沿来的时候数据将会是sdo=1;寄存器=0101010x。下降沿到来的时候,sdi上的电平将所存到寄存器中去,那么这时寄存器=0101010sdi,这样在8个时钟脉冲以后,两个寄存器的内容互相交换一次。这样就完成里一个spi时序。

例子:

假设主机和从机初始化就绪:并且主机的sbuff=0xaa,从机的sbuff=0x55,下面将分步对spi的8个时钟周期的数据情况演示一遍:假设上升沿发送数据

| 脉冲 | 主机sbuff | 从机sbuff | sdi | sdo |

| 0 | 10101010 | 01010101 | 0 | 0 |

| 1上 | 0101010x | 1010101x | 0 | 1 |

| 1下 | 01010100 | 10101011 | 0 | 1 |

| 2上 | 1010100x | 0101011x | 1 | 0 |

| 2下 | 10101001 | 01010110 | 1 | 0 |

| 3上 | 0101001x | 1010110x | 0 | 1 |

| 3下 | 01010010 | 10101101 | 0 | 1 |

| 4上 | 1010010x | 0101101x | 1 | 0 |

| 4下 | 10100101 | 01011010 | 1 | 0 |

| 5上 | 0100101x | 1011010x | 0 | 1 |

| 5下 | 01001010 | 10110101 | 0 | 1 |

| 6上 | 1001010x | 0110101x | 1 | 0 |

| 6下 | 10010101 | 01101010 | 1 | 0 |

| 7上 | 0010101x | 1101010x | 0 | 1 |

| 7下 | 00101010 | 11010101 | 0 | 1 |

| 8上 | 0101010x | 1010101x | 1 | 0 |

| 8下 | 01010101 | 10101010 | 1 | 0 |

这样就完成了两个寄存器8位的交换,上面的上表示上升沿、下表示下降沿,sdi、sdo相对于主机而言的。其中ss引脚作为主机的时候,从机可以把它拉底被动选为从机,作为从机的是时候,可以作为片选脚用。根据以上分析,一个完整的传送周期是16位,即两个字节,因为,首先主机要发送命令过去,然后从机根据主机的名准备数据,主机在下一个8位时钟周期才把数据读回来

SPI 总线是Motorola公司推出的三线同步接口,同步串行3线方式进行通信:一条时钟线SCK,一条数据输入线MOSI,一条数据输出线MISO;用于CPU与各种外围器件进行全双工、同步串行通讯。SPI主要特点有:可以同时发出和接收串行数据;可以当作主机或从机工作;提供频率可编程时钟;发送结束中断标志;写冲突保护;总线竞争保护等。图3示出SPI总线工作的四种方式,其中使用的最为广泛的是SPI0和SPI3方式(实线表示):

图2 SPI总线四种工作方式

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。SPI主模块和与之通信的外设音时钟相位和极性应该一致。SPI接口时序如图3、图4所示。

二.SPI功能模块的设计

根据功能定义及SPI的工作原理,将整个IP Core分为8个子模块:uC接口模块、时钟分频模块、发送数据FIFO模块、接收数据FIFO模块、状态机模块、发送数据逻辑模块、接收数据逻辑模块以及中断形式模块。

深入分析SPI的四种传输协议可以发现,根据一种协议,只要对串行同步时钟进行转换,就能得到其余的三种协议。为了简化设计规定,如果要连续传输多个数据,在两个数据传输之间插入一个串行时钟的空闲等待,这样状态机只需两种状态(空闲和工作)就能正确工作。