汇编写启动代码之开iCache

《朱老师物联网大讲堂》学习笔记

学习地址:www.zhulaoshi.org

前两节老师讲了一句话,我忘记写上来了,今天补上。

SOC基本上都是通过类似GPIO,内存控制器等对外设进行读写控制。

也有特殊的,像看门狗,就没有外设与之对应。

好了接下来开始我们今天的主题icache

那么,什么是icache呢

它是一种内存,虽然目前接触了好几种内存,寄存器,DDR等,它们在物理上的工作原理虽然不同,但是访问属性却很像。

在速度上

CPU > 寄存器 > Cache > DDR

在容量上

CPU < 寄存器 < Cache < DDR

整个系统中,CPU的供应链由:寄存器+cache+DDR+硬盘/flash 四阶组成。

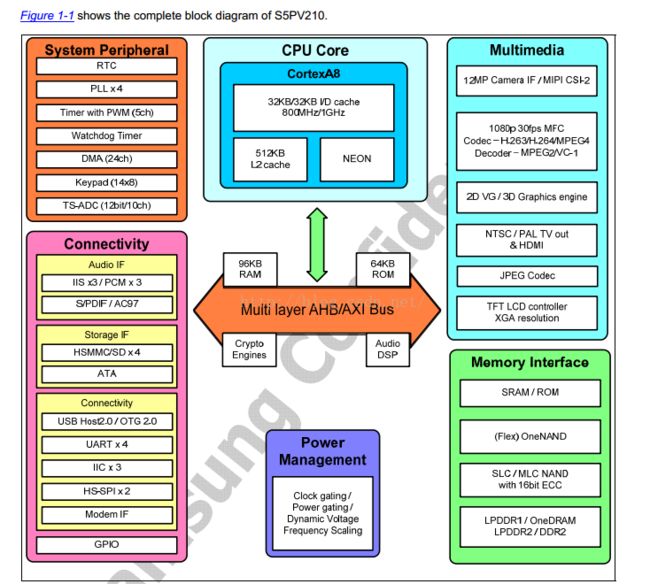

210内部有32KB的icache和32KB的dcache(见CPU Core中 32KB/32KB I/D cache 800MHz/1GHz)

icache用来缓存指令,

dcache用来缓存数据,目前裸机部分用不到,操作系统MMU才用得到。

CPU设计有一个基本原理:旧代码执行的时候,下一句执行当前一句代码旁边的代码的可能性要大很多。

若不是的话,就需要清理旧缓存,重新装载新的缓存。

在这里,目前icache的一切都是自动的,不需要我们去做什么。

我们只需要打开或者关闭icache。

IROM中的BL0已经打开了icache。(第二步:Initialize the instruction cache)

那我们具体该如何进行设置呢?有没有想到之前讲汇编指令提到的协处理器~

这里我们就是通过CP15协处理器来控制icache。

汇编代码读写CP15以开关icache

mrc p15,0,r0,c1,c0,0 // 读出cp15的c1到r0中 bic r0, r0, #(1<<12) // bit12 置0 关icache orr r0, r0, #(1<<12) // bit12 置1 开icache mcr p15,0,r0,c1,c0,0;

通过开关icache,可以看到上节LED实验中,灯闪烁的速度会变化。