SDRAM引入和初始化

《朱老师物联网大讲堂》学习笔记

学习地址:www.zhulaoshi.org

SDRAM在系统中属于SOC的外接设备

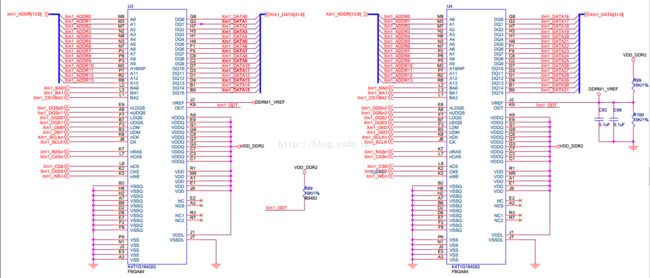

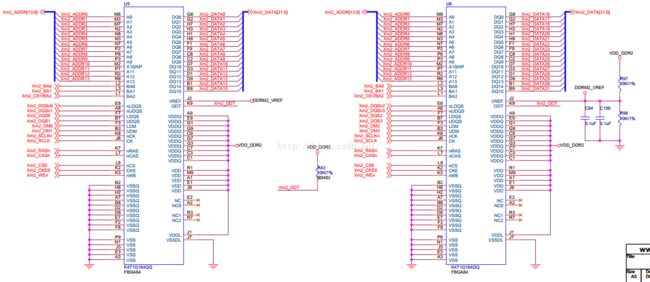

DRAM0:内存地址范围:0x20000000~0x3FFFFFFF(512M),对应的引脚为Xm1xxxx

DRAM1:内存地址范围:0x40000000~0x7FFFFFFF(1024M),对应的引脚为Xm2xxxx

上面的计算可以得出512+1024=1536,

也就是说210最多支持内存为1.5GB,如果给更多就无法识别,

目前我们用的只有512M,连接方法是DRAM0端口分布256M,DRAM1端口分布256M。

裸机上使用的是物理地址,所以对内存要特别了解。

因为图片太大,上面那个图片没有截完整,

Xm1_ADDR0~Xm1_ADDR13就是我们端口1的地址总线,总共14位,

Xm2_ADDR0~Xm2_ADDR13就是我们端口2的地址总线,总共14位,

Xm1_DATA0~Xm1_DATA31就是我们端口1的数据总线,总共32位,

Xm2_DATA0~Xm2_DATA31就是我们端口2的数据总线,总共32位,

图上地址总线和数据总线中间的就是控制总线,涉及到DDR的时序,比较麻烦,现阶段我们还理解不了,

由此也可以看出每个DDR的端口都由3类总线构成,

从数据总线的位数可以看出我们的内存是32位的(从物理上来说)。

下面这幅图是芯片的原理图1

这是4个芯片的原理图,其中VDD部分是电源部分,是硬件工程师处理的。

在每个芯片上,地址总线的位数都是一样的,和本节最开始那张内存端口是一致的,

但是为什么数据总线是16位,而不是32位呢?

16 + 16 = 32,并联处理的。

在原理图上横向的两个芯片是并联的,接在Xm1上,可以把它们理解为1个,虽然它们在物理上是分开的,

每一片是128MB,4片加起来就是512MB,要补充的一点帮助下面一点内容理解的是128MB = 1Gb,(明白了!B代表Byte,b代表bit)

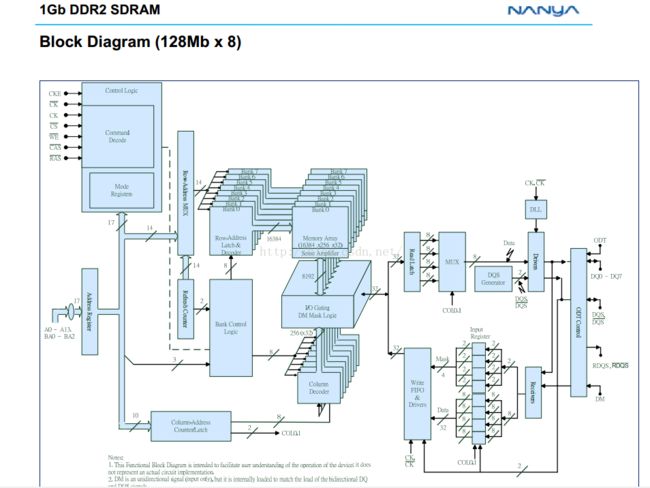

下面这幅图是具体到一个芯片内部了

看到这幅图的最上面了吗?

1Gb DDR2 SDRAM 就是我们刚刚说的128MB,

它的结构是Block Diagram (128Mb x 8),

8指的是8bank,128Mb指的是每个bank上的容量,

这里的8从何而来呢?

看到左边的BA0~BA2了吗?这是210的DDR端口,在芯片原理图的控制总线上也有这个,

代表的意思是2^3也就是8,通过这些总线进行选片。

那128Mb从何而来?

自己看,能看到上图中有row address(14位)和column address(10位),

这就好比坐标系中的x和y,

一共可以寻址的范围是(2^14)*( 2^10) = 2^24,

你去算算就是128MB,和我们前面说的单片内存容量是128MB是一致的,

这里B和b的区别,容易让人混淆,这么说吧,128Mb*8 = 128MB,

这下理解更顺畅了。

吃饭!去!