Tiny210(S5PV210) U-BOOT(四)----Nand Flash原理(1)

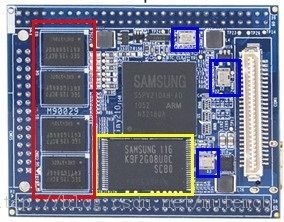

我在上次讲系统时钟的时候,提过一下,在S5PV210下面的那一片就是Nand Flash,旁边的那4片是DDR,我的型号是K9F2G08UOB

查找三星芯片的命名手册,这个网上有,PDF名称叫----三星_Nand_Flash_芯片型号命名规则.pdf,打开,查找K9F2G08UOB所代表的具体参数如下:

芯片类型:Nand Flash

Small Classification:SLC Normal

容量:2G/8bit

Technology:Normal

Organization:x8

Vcc:2.7V~3.6V

Mode:Normal

Generation:3rd Generation

整理一下信息:Nand Flash , 容量256M(2G/8bit) , 是用SLC存储(Single Level Cell单层存储) , 总线为8bit , 工作电压为2.7V~3.6V , 第3批次。

2.存储原理

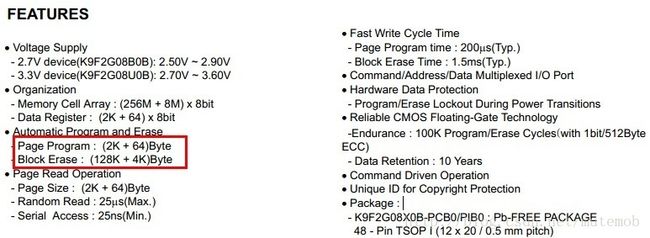

打开K9F2G08UOB芯片手册的P6页

由芯片手册上可知,这款NAND FLASH,页大小2K,块大小128K,意思就是读写操作,每次最小为2K,擦除操作每次最小为128K。什么原理呢,继续向下看。

由上图可知:1page = 2K, 1 block = 128K, 1Block=64Page, 芯片有128K

现在开始计算:

1 Block = 64*2 = 128K

那么我们FLASH的容量就2K * 128K = 256M (图中每个页还有Page都有保留区,所以实际上我们用不到256M),这里就有一个问题,为啥要设计成这样?

因为Nand Flash是用于设计成嵌入式系统的内存,程序进行内存的寻址时,为了提搞速度,所以,将线性的内存在逻辑上进行分块,分页,形成逻辑上的立体结构,这样,寻址就会方便,先找到是哪一块,再找到是哪一页,最后找到是这一页的哪个位置,这要比起从头到尾遍历,就要快很多了。

到这里,存储原理基本弄清楚了,Nand Flash的擦除操作是以block块为单位的,与此相对应的是其他很多存储设备,是以bit位为最小读取/写入的单位,Flash是一次性地擦除整个块:在发送一个擦除命令后,一次性地将一个block,常见的块的大小是128KB/256KB,全部擦除为1,也就是里面的内容全部都是0xFF了。这里就有了一个新问题,为什么擦除是写1,而不是写0呢?这和我们正常的逻辑怎么是个反的?

所谓1和0的介定,在存储器中,是通过向存储单元中施加电压来控制向里面是充电荷还是释放电荷。所以,本质上来说,数据0和1的表示,就是存储单元上的电压否超过一个特定的电压值,通常叫阈值,超过了这个阈值,就是1,没超过,就是0。所以说,全部擦除为1,也就意味着对整个block进行一次全部的充电。那这里,我们又有新问题了,那为什么不把擦除做成统一放电呢?

关于这个,我也没找到资料,书上也没有查到相关的,如果有人知道,麻烦也一并指点下我。我个人的理解是放电是时时刻刻存在的,放电比充电容易。就像我们的这些存储芯片,你充了一次电以后,是不是就一直为1了?不可能,能量是会衰减的,所以,你充一次电以后,隔了一段时间,不管你愿意不愿意,电荷必然会慢慢释放掉,那么,如果你要保证你的数据的正解性,仍然为1,不会被认为是0,你还得再充一次电,这个时间大概是多少,我在网上查了一下,存储体中电容的数据有效保存期上限是64ms(单位毫秒,也就是1/1000s)。那么,现在我们再来理解一下,SRAM和DRAM的区别,百度百科里查一下SRAM的介绍----SRAM不需要刷新电路即能保存它内部存储的数据。而DRAM(Dynamic Random Access Memory)每隔一段时间,要刷新充电一次,否则内部的数据即会消失,因此SRAM具有较高的性能。但是SRAM也有它的缺点,即它的集成度较低,相同容量的DRAM内存可以设计为较小的体积,但是SRAM却需要很大的体积,且功耗较大。

到这里,大家是不是有点明白了,为什么SRAM不需要刷新电路,你不需要刷新电路,那你怎么解决电荷释放的问题?这世上没有天上掉馅饼的事儿,别人不给你,那就自己带一个呗,所以SRAM是自己带有刷新电路的,所以,它体积大,所以它容量做不上去。所以,SRAM和DRAM的区别,就非常好理解了,一个带充电电路,一个不带,而DRAM的充电是由内存控制器隔一段时间去充电的。

所以,到这里,我理解的Nand Flash为什么擦除是擦为1,就是因为放电比充电容易,你控制每个存储单元去放电,肯定比控制每一个存储单元去充电要容易的多,硬件实现也要简单的多吧。

3.原理图和引脚分析

CLE(COMMAND LATCH ENABLE): 指示当前数据为控制命令,CLE输入控制路径发送到命令寄存器。

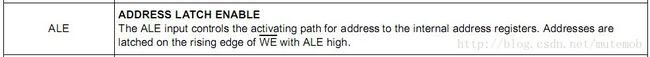

ALE(ADDRESS LATCH ENABLE): 指示当前数据为地址

CE#(CHIP ENABLE):芯片使能,俗称片选信号,表示flash chip是否被系统选中为当前操作芯片,低电平表示选中

RE#(READ ENABLE): 读使能,RE是串行数据输入,低电平时读取data到I/O总线,RE下降沿时读取数据有效,同时internal column address counter(内部列地址计数器)加1

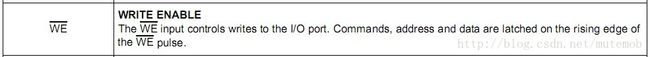

WE#(WRITE ENABLE): 写使能,低电平时向I/O中写入Command,address和data,在上升沿时操作完成。

WP#(WRITE PROTECT): 写保护,在电源置换过程中处于有效的低电平状态,保护flash里面的数据不受改写。当WP低电平有效时,高电平产生复位

R/B#(READY/BUSY OUTPUT): 读/忙状态输出,表示芯片是处于Read还是Busy状态,低电平表示Busy,返回高电平时表示处理完成。当芯片未被选中或无法输出数据时不会处于high-z状态,仍可用于检测芯片的闲忙状态

Vcc/Vss/N.C(POWER/GROUND/NO CONNECTION):Vcc是供电电压,Vss接地,N.C没定义

FAQ: 为什么要有CLE和ALE?

比如命令锁存使能(Command Latch Enable,CLE)和地址锁存使能(Address Latch Enable,ALE),那是因为,Nand Flash就8个I/O,而且是复用的,也就是,可以传数据,也可以传地址,也可以传命令,为了区分你当前传入的到底是啥,所以,先要用发一个CLE(或ALE)命令,告诉nand Flash的控制器一声,我下面要传的是命令(或地址),这样,里面才能根据传入的内容,进行对应的动作。否则,nand flash内部,怎么知道你传入的是数据,还是地址,还是命令啊,也就无法实现正确的操作了。那么,为什么不多几个I/O呢?

FAQ:Nand Flash为什么只设计8个I/O引脚,有什么好外?

1) 减少外围引脚:相对于并口(Parellel)的Nor Flash的48或52个引脚来说,的确是大大减小了引脚数目,这样封装后的芯片体积,就小很多。现在芯片在向体积更小,功能更强,功耗更低发展,减小芯片体积,就是很大的优势。同时,减少芯片接口,也意味着使用此芯片的相关的外围电路会更简化,避免了繁琐的硬件连线。

2) 提高系统的可扩展性,因为没有像其他设备一样用物理大小对应的完全数目的addr引脚,在芯片内部换了芯片的大小等的改动,对于用全部的地址addr的引脚,那么就会引起这些引脚数目的增加,比如容量扩大一倍,地址空间/寻址空间扩大一倍,所以,地址线数目/addr引脚数目,就要多加一个,而对于统一用8个I/O的引脚的Nand Flash,由于对外提供的都是统一的8个引脚,内部的芯片大小的变化或者其他的变化,对于外部使用者(比如编写nand flash驱动的人)来说,不需要关心,只是保证新的芯片,还是遵循同样的接口,同样的时序,同样的命令,就可以了。这样就提高了系统的扩展性。

4.Nand原理分析

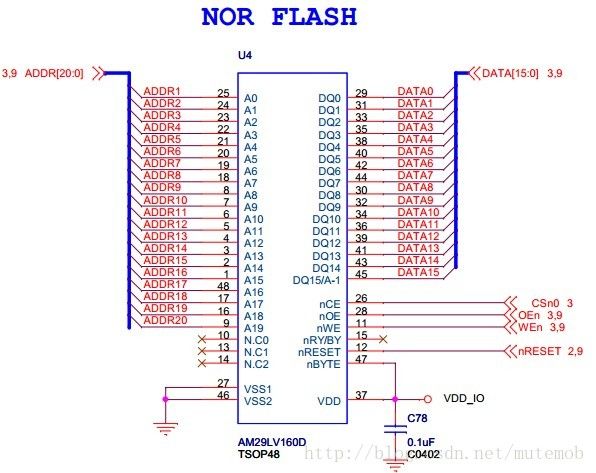

Nand Flash是一个典型的串口通信的芯片,我们知道,总线的三大元素地址、命令、数据。先看一个NOR FLASH的原理图:

上图中,地址线,数据线,命令线,三者清清楚楚,再来看我们的NAND FLASH的原理图,只有8根Data线,大部分线都是NC,未连接状态。

现在我们对照上面的Nand Flash的图来分析一下:

1)Nand Flash原理图上只有8根线Data0-Data7,是典型的串口通信,因为只有8根线,所以地址线、数据线肯定是复用的。

2)Nand Flash K9F2G08UOB容量为256M * 8bit,它的地址应该有28位,原理图上只有Data0-Data7,所以需要发出多次地址信号,下面是地址时序图,A0-A28,一共要发送五次,每次发8bit。

3)Nand Flash不能像内存一样直接读写,要先发命令,再发地址,再读写数据

很容易看出,我们要读取数据,要用到Read命令,该命令需要2个周期,第一个周期发0x00,第二个周期发0x30。在这个过程,你发了一个命令,对方能否立刻变接收到,并做出反应呢,肯定不行,所以,这得需要一个维持时间,这样才能保证你的数据的有效性。

4)CLE为高电平时,Data0-Data7发的是命令;

ALE为高电平时,Data0-Data7发的是地址;

CLE/ALE都为低电平时,Data0-Data7发的是数据,nWE,表示写,nRE,表示读。