ARM处理器的寄存器,ARM与Thumb状态,7种运行模式

ARM处理器工作模式一共有 7 种 :

USR 模式

正常用户模式,程序正常执行模式

FIQ模式(Fast Interrupt Request)

处理快速中断,支持高速数据传送或通道处理

IRQ模式

处理普通中断

SVC模式(Supervisor)

操作系统保护模式,处理软件中断swi reset

ABT 中止(Abort mode){数据、指令}

处理存储器故障、实现虚拟存储器和存储器保护

UND 未定义(Undefined)

处理未定义的指令陷阱,支持硬件协处理器的软件仿真

SYS 系统模式(基本上=USR)(System)

运行特权操作系统任务

用户模式和特权模式

除了用户模式之外的其他6种处理器模式称为特权模式

特权模式下,程序可以访问所有的系统资源,也可以任意地进行处理器模式的切换。

特权模式中,除系统模式外,其他5种模式又称为异常模式。

大多数的用户程序运行在用户模式下,此时,应用程序不能够访问一些受操作系统保护的系统资源,应用程序也不能直接进行处理器模式的切换。

用户模式下,当需要进行处理器模式切换时,应用程序可以产生异常处理,在异常处理中进行处理器模式的切换。

ARM处理的工作状态

在 ARM 处理器中,内核同时支持 32 位的 ARM 指令 和 16 位的 Thumb 指令。

对于 ARM 指令来说,所有的指令长度都是 32 位,并且执行周期大多为单周期,指令都是有条件执行的。

而 THUMB 指令的特点如下:

1,指令执行条件经常不回使用。

2,源寄存器与目标寄存器经常是相同的。

3,使用的寄存器数量比较少。

4,常数的值比较小。

5,内核中的桶式移动器(barrel shifter)经常是不使用的。

也就是说 16 位的 Thumb 指令一般可以完成 和 32 位 ARM 指令相同的任务。

ARM指令和 THUMB指令的关系:

THUMB指令是ARM指令的子集

可以相互调用,只要遵循一定的调用规则

Thumb指令与ARM指令的时间效率和空间效率关系为:

存储空间约为ARM代码的60%~70%

指令数比ARM代码多约30%~40%

存储器为32位时ARM代码比Thumb代码快约40%

存储器为16位时Thumb比ARM代码快约40~50%

使用Thumb代码,存储器的功耗会降低约30%

ARM指令和 THUMB指令之间切换(Interworking)的基本概念和切换时的子函数调用

处理器模式可以通过软件进行切换,也可以通过外部中断或者异常处理过程进行切换。

当应用程序发生异常中断时,处理器进入相应的异常模式。在每一种异常模式下都有一组寄存器,供相应的异常处理程序使用,这样就可以保证在进入异常模式时,用户模式下的寄存器不被破坏。

系统模式并不是通过异常进入的,它和用户模式具有完全一样的寄存器。但是系统模式属于特权模式,可以访问所有的系统资源,也可以直接进行处理器模式切换。它主要供操作系统任务使用。通常操作系统的任务需要访问所有的系统资源,同时该任务仍然使用用户模式的寄存器组,而不是使用异常模式下相应的寄存器组,这样可以保证当异常中断发生时任务状态不被破坏。

Thumb指令低密度及窄存储器时性能高的特点使得其在大多数基于 C 代码的系统汇中有非常广泛的应用,但是有些场合中系统只能使用 ARM 指令,比如:

1,如果对于速度有比较高的要求,ARM指令在宽存储器中会提供更高的性能。

2,某些功能只能由 ARM 指令来实现,比如:

访问 CPSR 寄存器来 使能/禁止 中断或改变处理器工作模式;

访问协处理器CP15;

执行 C 代码不支持的 DSP 算术指令;

异常中断(Exception)处理。在进入异常中断后,内核自动切换到 ARM 状态。即在异常中断处理程序人口的一些指令是ARM指令,然后根据需要,程序可以切换到 Thumb 工作状态,在异常中断处理程序返回前,程序在切换到 ARM 工作状态。

注:当处理器处于Thumb状态时发生异常(如IRQ、FIQ、Undef、Abort、SWI等),则异常处理返回时,自动切换到Thumb状态。

ARM 处理器总是 从 ARM 工作状态开始执行的。因此,如果要在调试器重运行 Thumb 程序,必须为 该 Thumb 程序添加一个 ARM程序头,然后再切换到Thumb工作状态,调用该 Thumb程序。

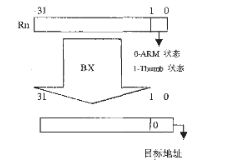

在实际系统中,内核状态需要经常的切换(Interworkong)来满足系统性能要求。具体的切换是通过 Branch Exchange,即 BX 指令来实现的。指令格式为:

Thumb 工作状态 BX Rn

ARM 工作状态 BX<condition> Rn

其中Rn可以是寄存器 R0 ~ R15 中的任意一个。指令可以通过将寄存器Rn的内容,拷贝到程序计数器 PC 来完成在 4GB地址空间中的绝对跳转,如果操作数寄存器的状态位 Bit0 = 0,则进入 ARM 工作状态;如果 Bit0 = 1,则进入 Thumb 工作状态。

ARM寄存器一共有 37 个寄存器:

ARM处理器工作工作模式下的寄存器:

不分组寄存器R0~R7

在所有的运行模式下,未分组寄存器都指向同一个物理寄存器,他们未被系统用作特殊的用途,因此,在中断或异常处理进行运行模式转换时,由于不同的处理器运行模式均使用相同的物理寄存器,可能会造成寄存器中数据的破坏,这一点在进行程序设计时应引起注意。

分组寄存器R8~R12

每次所访问的物理寄存器与处理器当前的运行模式有关

R8~R12:每个寄存器对应两个不同的物理寄存器

当使用fiq模式时,访问寄存器R8_fiq~R12_fiq

当使用除fiq模式以外的其他模式时,访问寄存器R8_usr~R12_usr。

R13、R14:每个寄存器对应6个不同的物理寄存器

其中的一个是用户模式与系统模式共用,另外5个物理寄存器对应于其他5种不同的运行模式

采用以下的记号来区分不同的物理寄存器:

R13_<mode>

R14_<mode>

mode为以下几种之一:usr、fiq、irq、svc、abt、und。

堆栈指针—R13/sp

R13在ARM指令中常用作堆栈指针,但这只是一种习惯用法,用户也可使用其他的寄存器作为堆栈指针。

sub sp, sp, #4 ;reserved for PC

stmfd sp!, {r8-r9}

由于处理器的每种运行模式均有自己独立的物理寄存器R13,在初始化部分,都要初始化每种模式下的R13,这样,当程序的运行进入异常模式时,可以将需要保护的寄存器放入R13所指向的堆栈,而当程序从异常模式返回时,则从对应的堆栈中恢复。

子程序连接寄存器—R14/lr

R14也称作子程序连接寄存器或连接寄存器LR。当执行BL子程序调用指令时,可以从R14中得到R15(程序计数器PC)的备份。其他情况下,R14用作通用寄存器。

在每一种运行模式下,都可用R14保存子程序的返回地址,当用BL或BLX指令调用子程序时,将PC的当前值拷贝给R14,执行完子程序后,又将R14的值拷贝回PC,即可完成子程序的调用返回。

BL SUB1

……

SUB1:

……

MOV PC,LR /*完成子程序返回等 同于BX LR */

程序计数器—R15/PC

虽然 R15 也可以用作通用寄存器,但要注意有一些特殊限制,如果违法了这些限制,指令执行的结果将是不可预料的。

程序状态寄存器(CPSR/SPSR)

CPSR(当前程序状态寄存器)

SPSR(备份的程序状态寄存器)

所有处理器模式下都可访问当前的程序状态寄存器CPSR。

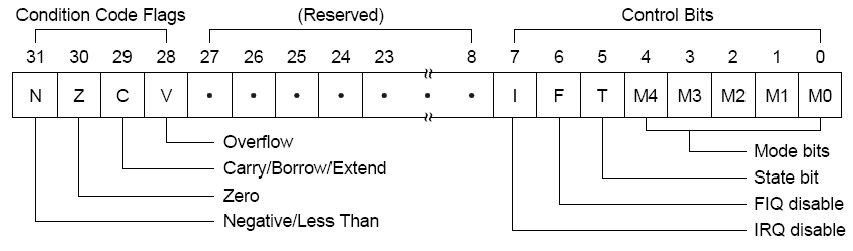

CPSR:程序状态寄存器(current program status register) (当前程序状态寄存器),在任何处理器模式下被访问。它包含了条件标志位、中断禁止位、当前处理器模式标志以及其他的一些控制和状态位。

CPSR在用户级编程时用于存储条件码。

SPSR:程序状态保存寄存器(saved program status register),每一种处理器模式下都有一个状态寄存器SPSR,SPSR用于保存CPSR的状态,以便异常返回后恢复异常发生时的工作状态。当特定 的异常中断发生时,这个寄存器用于存放当前程序状态寄存器的内容。在异常中断退出时,可以用SPSR来恢复CPSR。由于用户模式和系统模式不是异常中断 模式,所以他没有SPSR。当用户在用户模式或系统模式访问SPSR,将产生不可预知的后果。

CPSR格式如下所示。SPSR和CPSR格式相同

程序状态寄存器的条件码标志

N、Z、C、V均为条件码标志位。它们的内容可被算术或逻辑运算的结果所改变,并且可以决定某条指令是否被执行

在ARM状态下,绝大多数的指令都是有条件执行的。

在Thumb状态下,仅有分支指令是有条件执行的。

状态寄存器的低8位(I、F、T和M[4:0])称为控制位,发生异常时这些位可以被改变。如果处理器运行特权模式,这些位也可以由程序修改。

中断禁止位I、F:

I=1 禁止IRQ中断;

F=1 禁止FIQ中断。

T标志位:该位反映处理器的运行状态

ARM体系结构v5及以上的版本的T系列处理器,当该位为1时,程序运行于Thumb状态,否则运行于ARM状态。

ARM体系结构v5及以上的版本的非T系列处理器,当该位为1时,执行下一条指令以引起未定义的指令异常;当该位为0时,表示运行于ARM状态。

运行模式位M[4:0]是模式位,决定处理器的运行模式

THUMB状态下的寄存器组织

Thumb与ARM状态下的寄存器关系