时钟约束

设计一个计数程序,使用时钟clk,在这个clk的上升沿计数。

硬件上该时钟由50MHz晶振提供,因此设计时钟就要约束为50MHz,20ns时钟周期。

编译工程后打开quartus II TimeQuest:

点击Netlist -> Create Timing Netlist:

点击OK,点击菜单栏Constraints -> Create Clock:

设置period为20ns,设置Targets为clk,点击Run完成约束设置。

依次点击task栏里的Update Timing Netlist 和 Write SDC File

点击OK,工程目录中的ti_me.out.sdc文件里便出现了所添加的约束:

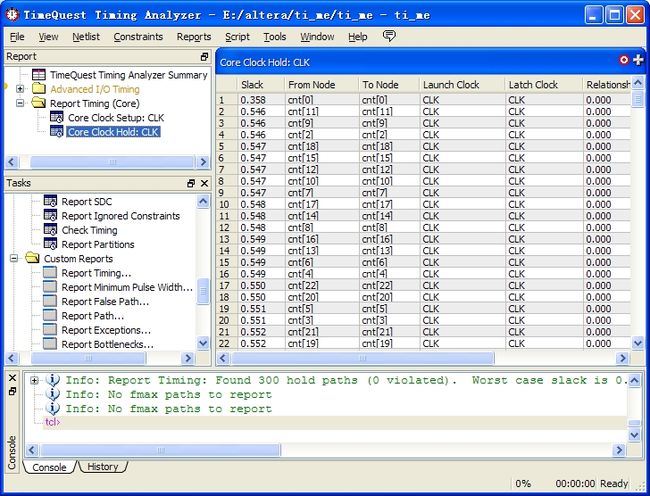

重新编译工程,重新进入TimeQuest,点击Report All Core Timings:

在report窗口出现Report Timing (Core),可以看到Setup路径和Hold路径:

点击Report Timing,选择Setup:

Setup详细路径分析:

Data Arrival Time = Launch Edge + Tc2t + Tco + Tc2r = 0 + 2.541 + 0.199 + (2.655-0.199)

Data Required Time = Latch Edge + Tc2r – Tsu = 20 + 2.476 – (-0.015)

Setup time slack = Data Required Time – Data Arrival Time = 22.491 – 5.196 = 17.295ns

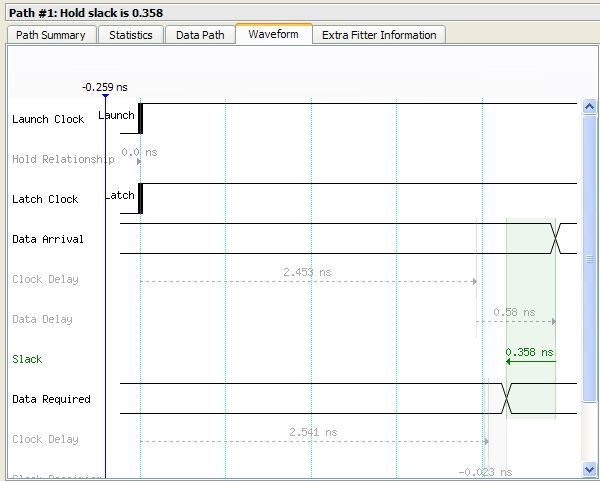

点击Report Timing,选择Hold:

Hold详细路径分析:

Data Arrival Time = Launch Edge + Tc2t + Tco + Tc2r = 0 + 2.453 + 0.199 + (0.580-0.199)

Data Required Time = Latch Edge + Tc2r + Th = 0 + 2.518 + 0.157

Setup time slack = Data Arrival Time – Data Required Time= 3.033– 2.675= 0.358ns

Tco表示数据在被锁存后在寄存器内所经过的延时;

Tc2t表示时钟源到源寄存器reg1所经过的时钟网络延时;

Tc2r表示时钟源到目的寄存器reg2所经过的时钟网络延时;

Tr2r表示数据从源寄存器的输出端到目的寄存器的输入端所经过的延时;