用行为级描述方式实现一个加法器电路(基于ISE的设计)(2输入1位全加器电路)

准备

先用行为级描述方式实现一个2输入一位全加器电路

由于后面需要使用综合工具进行综合,这里先声明使用的FPGA是Virtex-7系列的:

目的很单纯,就是熟悉一下使用ISE进行FPGA设计的一般流程。

硬件语言描述

首先使用行为级描述方式的硬件描述语言(HDL)设计一个一位全加器电路,Verilog HDL设计代码如下:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 14:24:53 08/13/2018

// Design Name:

// Module Name: adder

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module adder(SUM, C_OUT, A, B, C_IN );

input A, B, C_IN;

output SUM, C_OUT;

assign {C_OUT, SUM} = A + B + C_IN;

endmodule

测试文件

添加一个仿真文件,也就是行为仿真:

`timescale 1ns / 1ps

////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 14:28:27 08/13/2018

// Design Name: adder

// Module Name: G:/ISE_file/adder/adder_tb.v

// Project Name: adder

// Target Device:

// Tool versions:

// Description:

//

// Verilog Test Fixture created by ISE for module: adder

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////

module adder_tb;

// Inputs

reg A;

reg B;

reg C_IN;

// Outputs

wire SUM;

wire C_OUT;

// Instantiate the Unit Under Test (UUT)

adder uut (

.SUM(SUM),

.C_OUT(C_OUT),

.A(A),

.B(B),

.C_IN(C_IN)

);

initial begin

// Initialize Inputs

A = 0;

B = 0;

C_IN = 0;

// Wait 100 ns for global reset to finish

#100 A = 1'b1; B = 1'b1;

#100 A = 1'b0; B = 1'b1;

#100 C_IN = 1'b1;

end

endmodule

行为仿真图

使用ISE自带的仿真器仿真图如下:

符合要求。

综合

下面对这个设计进行综合:

综合是将设计输入翻译成由与、或、非门和RAM、触发器等基本逻辑单元组成的逻辑网表,并根据设计目标和条件约束优化所生成的逻辑连接,生成EDF文件。

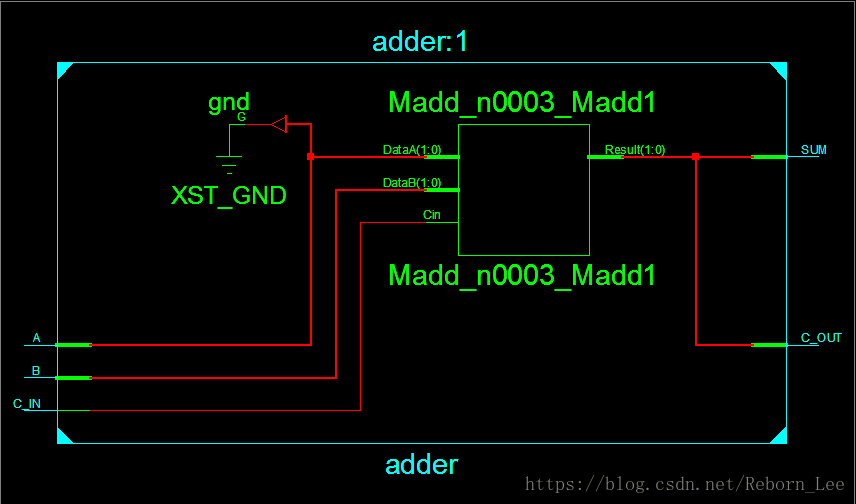

查看寄存器传输级电路:

这个RTL Schematic看的不是太清楚,那从PlanAhead中查看:

查看Technology Schematic

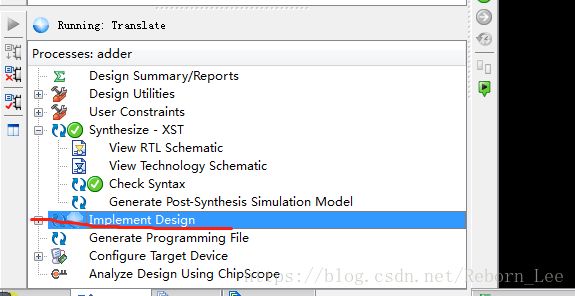

实现(Implement)

实现过程主要包括转换(Translate)、映像(Map)、布局布线(Place&Route)和时间参数提取(Timing)等几个方面。

Translate:在转换过程中,多个设计文件和约束文件将被合并为一个NGD文件,并同时输出BLD文件。其中NGD文件包含当前设计中的全部逻辑描述,BLD文件是转换的运行报告,转换可以接收的设计文件包括EDN、ENF、EDIF和SEDIF文件,转换的约束文件包括UCF、NCF、NMC、NGC文件。

Map:在映像过程中,当前设计的NGD文件将被映像为模板器件的特定物理单元,如CLB、IOB等,并保存在NCD文件中。

Place&Route:通过读取当前设计的NCD文件,布局布线将映像产生的物理单元在目标器件上放置和连接,并提取相应的时间参数。

布局布线的输入文件包括NCD、PCF和NGD(可选)模板文件,输出文件包括NCD、DLY、PAD和PAR文件。

在布局布线的输出文件中,NCD文件包含当前设计的全部物理实现信息,DLY文件包含当前设计的网络延时信息,PAD文件包含当前设计的I/O管脚配置信息,PAR文件是布局布线的运行报告。

时间参数提取:时间参数提取将生成当前设计的含有时间参数的反标网表,该反标网表将用于时序仿真。时间参数提取的输入文件包括NCD和PCF(可选)文件。时间参数提取输出的时序报告可以反映当前设计是否满足时序约束。

如下图,双击Implement Design,即可进行实现过程:

出现了一些毛病,解决后再接着写。