基于FPGA实现的流水灯项目

基于FPGA实现的流水灯实验

一、开发环境

软件环境:Quartus Prime 17.1 ,notepad++,gvim,modelsim-SE,TimeGen3

硬件环境:DE2-115(Intel FPGA Cyclone IV,EP4CE115F29C7N)

二、实验目的

1.掌握Quartus Prime 17.1的开发环境及FPGA的开发流程。

2.熟悉开发板(DE2-115)的硬件资源及其使用方法。

3.掌握二进制译码器、计数器的设计与实现方法。

三、实验原理

译码是将具有特定含义的二进制码转换成对应的输出信号,具有译码功能的逻辑电路称为译码器。译码器分为两种类型,一种是将一系列代码转换成与之一一对应的有效信号。这种译码器可称为二进制译码器或唯一地址译码器,它常用于计算机中对存储器单元地址的译码,即将每一个地址代码转换成一个有效信号,从而选中对应的单元。另一种是将一种代码转换成另一种代码,所以也称为代码变换器。例如BCD至七段显示译码器执行的动作就是把一个4位BCD码转换成为七段码输出,以便在七段显示器上显示出这个十进制数。

计数器一种用于对时钟脉冲进行计数的电路,它还可用于分频、定时、产生节拍脉冲以及其他时序信号。计数器的种类不胜枚举,按触发器动作分类,可分为同步计数器和异步计数器;按编码数值增减分类,可分为递增计数器、递减计数器和可逆计数器;按编码分类,又可分为二进制码(简称二进制)计数器、BCD计数器、循环码计数器。

计数器运行时,依次遍历规定的各状态后完成一次循环。它所经过的状态总数称为计数器的“模”(Modulo),并用M表示。若某个计数器在n个状态下循环计数,通常则称之为模n计数器。有时也把模n计数器称为容量为n的计数器或n进制计数器。

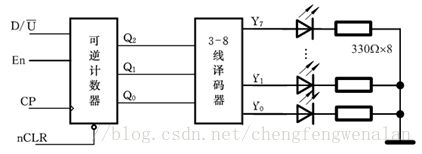

本实验将把二进制译码器与计数器结合起来,按照框图1.1组成一个流水灯电路,实现依次循环点亮8个LED的功能。要求用VerilogHDL进行设计,并在FPGA开发平台上最终实现该电路。

图1.1 流水灯电路的组成框图

四、实验步骤

4.1 3/8线译码器的设计与实现

设计一个带使能端的3线-8线译码器,其功能表4.1所示。

表4.1 3/8线译码器逻辑功能表

| 输 入 |

输 出 |

||||||||||

| EN |

A2 |

A1 |

A0 |

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 |

| 0 |

x |

x |

x |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| 1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| 1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

| 1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

| 1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

| 1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

| 1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

| 1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

| 1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

实验步骤与要求

1.新建工程前的准备

在桌面上创建一个文件夹EDA_Lab,再在里面新建文件夹Lab1A,再在Lab1A里新建文件夹prj(项目),sim(仿真),src(源文件)三个文件夹,最后再src文件夹里新建decoder3_8.v文件,如图4.1所示

图4.1 新建工程前的准备

2.建立新工程

*打开quartus Prime 软件,点击File->new->New Quartus Prime Project。

* 工程项目命名:点击OK->Next,出现命名的界面。(最好文件名、模块名一致)

*一直选择Next直至出现add Files界面,添加之前编写好的.v文件到工程中

*继续选择Next直至出现硬件选择界面,选择正确的芯片型号(在开发板上可以找到的)

*继续点击Next->Next->Finish,就完成了工程的建立。如图4.2所示

图4.2 新建工程步骤

3.编写.v文件代码

*建议使用notepad++或者gvim编写代码,编写好了再添加到项目工程中即可。如图4.3所示

图4.3 编写.v文件代码

4.绑定引脚和编译

*对于输出、输入端口进行管脚绑定,选择菜单栏上Assignments---PINS,打开引脚分配器界面。在location一栏选择相对应的管脚(对应管脚在光盘中的芯片引脚分配图上查找),这个自己试一下就可以了,本实验采用导入引脚文件的方式,以后的实验将都采用这种方式。

*修改设置,设置三态无用管脚和nCEO常用I/O设置

选项Assignments----选Device----点Device and Pins Options,在选项卡中选Unused Pins---在Reserve allunused pins:点下拉菜单。中选 As input tri-state,在选项卡中选择 Dual-Purpose Pins 在nCEO 点下拉菜单选Us as regular I/O---确定----OK

*依次点击Analysis&Sythesis 和 Assembler即可生成.sof文件,该文件可以下载到开发板上。如图4.4所示

图4.4 绑定引脚和编译

5.下载.sof文件到FPGA开发板上

*点击Program Device,然后选择好usb_blaster和相应的.sof文件,再点击start即可。如图4.5所示

图4.5 下载.sof文件到FPGA开发板上

5.测试译码器

得到的实验结果如图所示。注意g1,g2,g3位使能信号,当g1=1,g2=0,g3=0时,译码器才会正常工作。a0,a1,a2是译码器的输入端。例如当a0=1,a1=1,a2=1时,LEDG7将被点亮。如图4.6所示

图4.6 译码器实验现象

4.2 计数器器的设计与实现

设计一个同步可逆二进制计数器。其功能要求如下:

① 计数器循环计数,其计数范围为0~7;

② 设置一个加/减计数的控制开关M,当M=0时,进行循环递增计数;当M=1时,进行循环递减计数。

③ 具有异步清零和暂停计数的功能。

扩展功能:去掉开关M,实现自动加、减可逆计数,即0,1,2,3,4,5,6,7,6,5,4,3,2,1,0,1,2,…。

实验步骤与要求

①创建一个子目录E:\EDA_Lab\Lab1B,并新建一个工程项目,与前面一样的思路

②使用Verilog HDL描述计数器的逻辑功能。

③根据FPGA开发板使用说明书,对设计文件中的输入、输出信号分配引脚。即电路的时钟clk输入用1hz时钟信号,其他输入用拨动开关,电路的输出用LED指示(或者七段数码显示器)。

④重新编译电路,并下载到FPGA器件中。改变拨动开关的位置,并观察LED的亮、灭状态,测试电路功能。

⑤根据实验流程和实验结果,写出实验总结报告,并对实验现象进行说明。

4.3流水灯电路设计

电路设计功能要求如下:

按照总体框图1.1,将上述设计的计数器模块和译码器模块连接起来,实现依次循环点亮8个LED的功能。

实验步骤与要求

①创建一个子目录E:\EDA_Lab\Lab1C,并新建一个工程项目。步骤和前面的一样

②复制上述两个文件到当前项目子目录中,再建立一个Verilog HDL顶层文件,调用可逆计数器和译码器子模块,描述图1.1所示电路功能。并将这3个文件都添加到工程项目中,再编译整个项目。接着,对设计项目进行时序仿真,记录仿真波形图。

③对设计顶层文件进行引脚分配。

④重新编译电路,并下载到FPGA器件中。改变拨动开关的位置,并观察LED的亮、灭状态,测试电路功能。

⑤根据实验流程和实验结果,写出实验总结报告,并对波形图和实验现象进行说明。

⑥完成实验后,关闭所有程序,并关闭计算机。

5.福利

本实验的所有源代码和.sof都已经发布到了github上,下载后,自己把.sof下载到板子上,看看效果。

下载链接:下载流水灯源码 。如图5.1所示

图5.1 github下载界面