Verdi基础知识整理

Verdi主要在以下方面使用

Verdi使用情形:

- IC验证工程师(Debug)

- IC设计工程师(Review)

学习目标主要以下三方面:

- 能够生成fsdb波形;

- 能够查看fsdb波形;

- 能够追踪RTL代码。

生成FSDB波形

- 三个变量

- VERDI_HOME/NOVAS_HOME:仿真器默认,且为设置PATH做准备

- PATH:让系统(Linux)找到verdi

- LD_LIBRARY_PATH:让系统(Linux)能够找到Verdi需要的库文件.

- 三个命令

- echo(可配合sed):查询环境变量

- echo $PATH | sed ‘s/\:/\n/g’

- echo $LD_LIBRARY_PATH | sed ‘s/\:/\n/g’

- echo(可配合sed):查询环境变量

/home/.tools/synopsys/Verdi3_L-2016.06-1/share/PLI/libLINUX64

/home/.tools/synopsys/Verdi3_L-2016.06-1/share/PLI/IUS/LINUX64/boot

/home/.tools/synopsys/Verdi3_L-2016.06-1/share/PLI/libLINUX64

/home/.tools/synopsys/Verdi3_L-2016.06-1/share/PLI/IUS/LINUX64/boot

/home/.tools/synopsys/Verdi3_L-2016.06-1/share/PLI/libLINUX64

/home/.tools/synopsys/Verdi3_L-2016.06-1/share/PLI/IUS/LINUX64/boot

+ which :查询当前软件是否设置,若设置成功,会显示软件路径

+ uname -i:查询当前系统信息,如硬件平台64bit为x86_64/amd64,32bit平台为i386

- 两大方法

- 使用Verilog系统函数

initial begin

$fsdbDumpfile("top_tb.fsdb");

$fsdbDumpvars(0,"tob_tb");

end* 使用UCLI、TCL接口(VCS使用tcl脚本,irun、questa与该脚本类似)

global env

fsdbDumpfile "$env(demo_fifo).fsdb"

fsdbDumpvars 0 "top_tb"

run- Dump波形的两类主要方法优缺点比较

| … | 基于系统函数 | 基于ucli/tcl接口 |

|---|---|---|

| 优点 | 1.新员工熟悉Verilog代码,接受较快 | 1.不需要重新编译仿真顶层; 2.使用高级语言接口,容易完成复杂处理,例如传递变量,例如使用正则表达式;3.交互式接口,控制灵活,仿真过程可修改dump信息,如dumpon/dumpoff |

| 缺点 | 1.需要重新编译系统,浪费时间(不使用 value v a l u e plusargs时);2.Verilog是低级语言,对于文本处理比较困难,不支持正则表达式 | 1.新员工大多不熟悉Tcl,接受较慢 |

+ 三大EDA厂商

* Synopsys:VCS + Verdi

* Cadence :irun + Verdi

* Mentor :Questa + Verdi

VCS脚本:与Verdi有关的为注释内容,使用ucli接口

com:

vcs -full64 \

-sverilog \

-debug_pp \ # 使能UCLI命令

-LDFLAGS \ # 传递参数给VCS的linker,与以下三行配合使用

-rdynamic \ # 指示需加载的动态库,如libsscore_vcs201209.so

-P ${VERDI_HOME}/share/PLI/VCS/${PLATFORM}/novas.tab \ # 加载表格文件

${VERDI_HOME}/share/PLI/VCS/${PLANTFORM}/pli.a \ # 加载静态库

-f ../${demo_name}/tb_top.f \

+vcs+lic+wait \

-l compile.log

sim:

./simv \

-ucli -i ../scripts/dump_fsdb_vcs.tcl \ # ucli的输入文件(-i)为tcl脚本

+fsdb+autoflush \ # 命令行参数autoflush,一边仿真一边dump波形,如果没有该参数,那么不会dump波形,需要在ucli命令run 100ns后键入fsdbDumpflush才会dump波形

-l sim.log- 其中dump_fsdb_vcs.tcl(ucli脚本为tcl语言)

global env # tcl脚本引用环境变量,Makefile中通过export定义

fsdbDumpfile "$env(demo_name).fsdb" # 设置波形文件名,受环境变量env(demo_name)控制 # demo_name在makefile中使用export demo_name=demo_fifo

fsdbDumpvars 0 "tb_top" # 设置波形的顶层和层次,表示将tb_top作为顶层,Dump所有层次

run # 设置完dump信息,启动仿真(此时仿真器被ucli控制) 可以run 100ns会在仿真100ns的时候停下来下来- 也可以使用交互式仿真:注释内容可以在仿真过程中键入

global env

fsdbDumpfile "$env(demo_name).fsdb"

fsdbDumpvars 0 "top_tb"

run 200ns

#fsdbDumpoff

#run 100ns

#fsdbDumpon

#runirun编译运行脚本:

com:

irun \

-elaborate \

-access +r \ # 表示需要有读的权限

-f ../${demo_name}/tb_top.f \

-top tb_top \

-licqueue \

-l compile.log

sim:

irun \

-R \

-input ../scripts/dump_fsdb_irun.tcl \

+fsdb+autoflush \

-licqueue \

-l sim.log- dump_fsdb_irun.tcl

global env

call fsdbDumpfile "$env(demo_name).fsdb" # 需要使用call,与vcs区别之一

call fsdbDumpvars 0 "tb_top"

run

quit # 需要使用quit,irun不自动结束questa脚本

compile:

vlib work

vmap work work

vlog \

-64 \

-sv \

+acc \ # +acc使加载PLI有效

-f ../${demo_name}/tb_top.f \

-l com.log

run:

vsim \

-64 \

-batch \

-novopt \

-pli ${VERDI_HOME}/share/PLI/MODELSIM/${PLATFORM}/novas_fli.so \ # 加载共享对象

work.tb_top \

-do ../scripts/dump_fsdb_questa.tcl \

+fsdb_autoflush \

-l sim.log- dump_fsdb_questa.tcl

gloal env

fsdbDumpfile "$env(demo_name).fsdb"

fsdbDumpvars 0 "tb_top"

run -all

quit -sim不同场景dump波形的需求

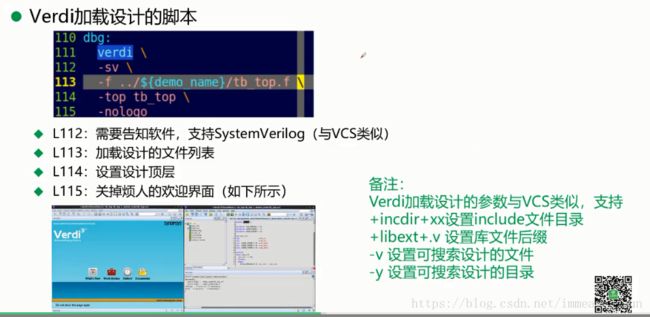

verdi 加载设计的脚本

debug:

verdi \

-sv \ # 支持sv

-f ../${demo_name}/tb_top.f \ # 加载设计文件列表

-top tb_top \ # 指定设计顶层

-nologo # 关掉欢迎界面- PS:

- Verdi加载设计的参数与VCS类似

- 支持+incdir+xx 设置include文件目录

- +libext+.v 设置库文件后缀

- -v 设置可搜索设计的文件

- -y 设置可搜索设计的目录

加载FSDB波形

dbg:

verdi -sv \ #支持SV

-f ../${demo_name}/tb_top.f \ #加载设计文件列表

-top tb_top \ #设置设计顶层

-ssf ${waveform} \

-nologo #关闭欢迎界面verdiLog文件夹里面的compile.log是verdi编译信息

重复加载设计和波形:(reload)

- 避免重复开关gui

- 避免频繁申请license(license资源问题,手中掌握资源,霸占…)

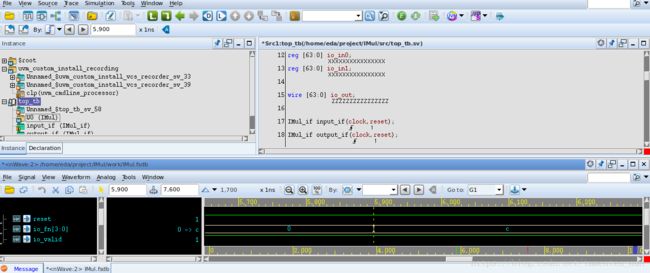

- verdi界面

- ntrace:file -> reload design,一般重新加载设计的同时会重新load wave

- nwave :file -> reload

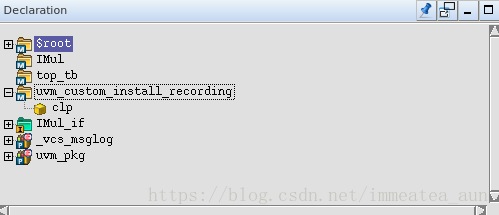

- 拓扑结构:topology(在nTrace)

- 源码(nTrace)

选择信号方式:

- 在设计中选择信号,按快捷键ctrl+w

- 在nWave界面使用通配符,可以选择in/out/inout/net(wire)/register等信号

查看波形

目标 快捷键 鼠标操作 100%波形 F 点击100%符号 缩小波形 z(推荐) - 放大波形 shift+z 左键拖选放大范围(推荐) 移动信号 中键选择位置+信号+M 鼠标中键按住信号拖拽 拷贝波形 ctrl+p 右键选择 粘贴信号 中间选择位置+Ins 右键选择 删除信号 Del 右键选择 显示结构 h(开/关) - 时间差

+ nWave:waveform -> marker 标记 :输入名字,然后add

* nWave:waveform -> Signal Value Radix修改进制;

* nWave:waveform -> Signal Value Notation设置信号。无符号unsigned,有符号一般选择Signed 2's Complement

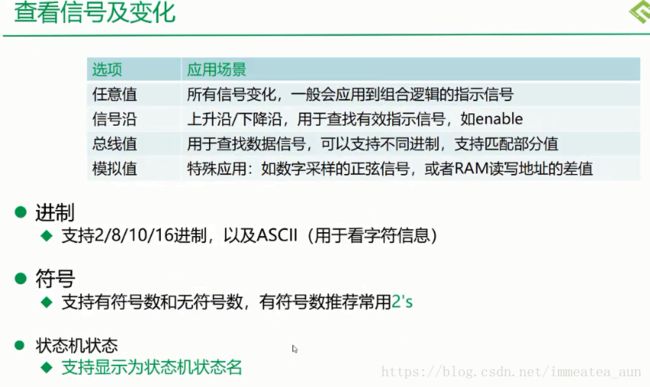

查看信号变化:

save和restore

- 存储当前查看波形的工程

- 将当前所有信号存成一个*.rc文件

- 重新打开波形界面时,restore信号

- nwave:file -> Save Signal/Restore Signal

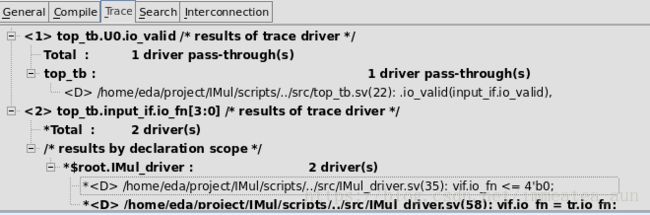

debug 追踪波形

快速熟悉一个设计:双击RTL中的信号,追踪波形

- 掌握设计拓扑结构:通过nTrace界面获取

- 熟悉设计的输入、输出

- Trace(Input)

- 哪些信号驱动了当前信号

- Load(Output)

- 当前信号驱动了哪些信号

- Trace(Input)

- 找到ntrace中的L、D

- 同时可以在trace界面右键Collapse All,Expand All,save等操作

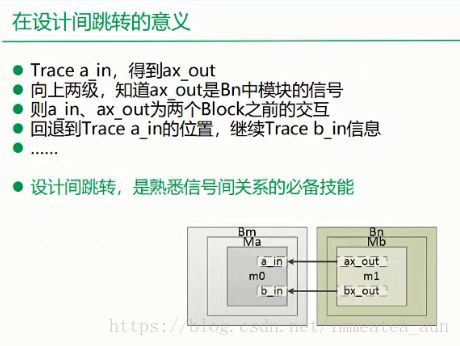

- 在设计之间跳转,回退 上、下、前、后等

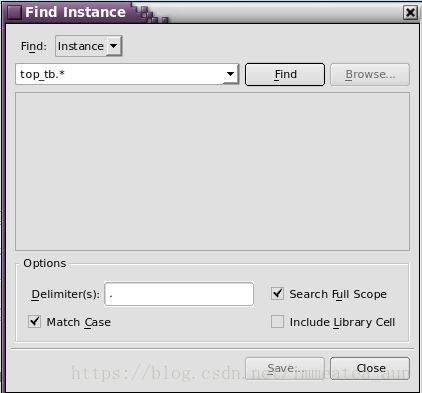

快速找到应用实例:nTrace : Source -> Find Signal/Instance/Instport

- 勾选Search Full Scope ,选择输入要例化的模块(支持通配符)

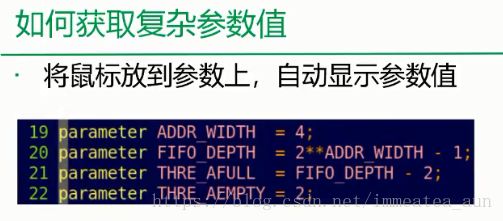

+ 获取波形里面的信号数值:nTrace:source -> Active Annotation,将所有的信号标值