随着工艺节点的不断发展(现在普遍是28nm,22nm,16nm,14nm,甚至有的都在做7nm),芯片的性能需求越来越高,规模也越来越大,数字IC设计工程师对芯片的功耗也越来越关心了,特别是移动端的消费类电子产品,对芯片的功耗要求特别高,一旦功耗太大,整个产品可能就是一个暖手宝,甚至整个芯片的性能会大大地打折扣,无法满足实际应用需求。那么,今天小编就带领大家一起来回顾下功耗的定义及其组成部分,并总结降低功耗的若干种常用方案。

芯片功耗分为动态功耗和静态功耗两大部分。

图1 动态功耗示意图

动态功耗是电路在工作时(翻转时)所消耗的能量。对于CMOS电路来说,它又分为开关功耗和短路功耗。开关功耗为电路翻转时对负载电容充电的功耗,短路功耗为输入翻转时,PMOS和NMOS同时打开的瞬间电流形成的功耗。用公式描述可写为:

Pdyn = (CL * Vdd2 * Ptran * F) + (ttran * Vdd * Ipeak * F)

其中,CL为电路总负载电容;Vdd为工作电压;Ptran为工作电路所占比例;F为工作时钟频率;ttran为PMOS,NMOS同时导通时间;Ipeak为短路电流。

公式中第一部分为开关功耗,第二部分为短路功耗。一般来说,只要gate的slew足够小,也就是ttran足够快,短路功耗一般可以忽略。

从公式中可以看到降低动态功耗的思路,可以从Vdd、F、CL和降低gate翻转次数等方面来设计降低功耗的方案。

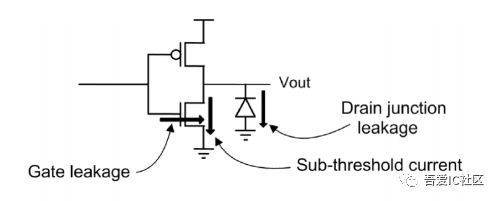

再来说说静态功耗。静态功耗是电路在没有翻转时,晶体管中漏电流造成的功耗。根据重要性可以分为以下四个部分:

1.亚域值漏电流Isub: 从Drain经过弱反形层流向Source的电流

2. 栅电流Igate:由于隧道效应和热载流子效应,由Gate经薄栅氧流向Sub的电流

3. 由Gate引起的Drain电流IGIDL:由于Drain端的强电场引起的由Drain流向Sub的电流

4.结反偏电流Irev:反偏结耗尽区少子漂移和电子空穴对产生形成的由Drain、Source到Sub的电流。

图2 leakage电流示意图

那么,在数字IC设计中,我们常见的降低功耗的方法有哪些呢?小编特地做了一个小归纳,方法如下:

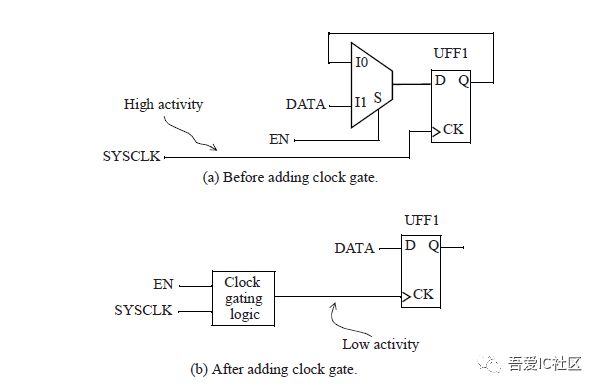

1.clock gating 门控时钟技术。众所周知,在数字IC设计中,时钟信号的翻转率是比较高的,因此它的功耗约占整个芯片功耗的20-30%。传统的设计方法是时钟信号一直是存活着的(常开),门控时钟技术就是根据设计,将暂时不用的模块的时钟信号通过一个控制信号gating住,降低这个模块的时钟信号翻转率,从而降低芯片功耗的一种技术。clock gating的加法也有很多,有在rtl级就例化进来的gating(往往是比较root的gating),也有综合阶段工具自动加进来的。从数字前端设计的角度,clock gating是想越靠近root端越好(因为一个gating可以控制更多的寄存器或者时钟单元),一旦将某个gating关掉,能够节省较多的功耗。因此,在数字后端实现过程中,经常会碰到到gating使能端E pin的setup比较难meet,主要原因是这类gating比较靠近root导致的。关于如何fix clock gating使能端的setup会在后续更新文章中做详细的分析。

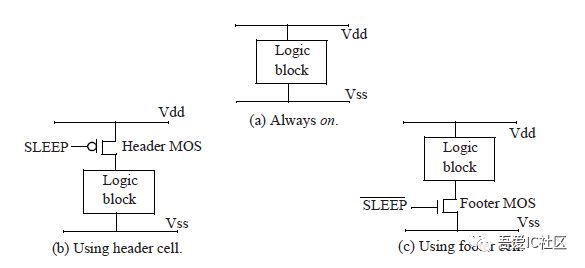

2.power gating。在数字IC后端设计中,经常采用这个策略降低功耗。在后端实现过程中,加入MTCMOS来控制标准单元的开关。

3.Multi vt cells 。这个就是在数字IC后端设计实现过程中,将某些不是critical path的地方尽量用HVT或者RVT,降低leakage。当然这个需要与performance,area做一个tradeoff。因为用HVT或者RVT,由于timing不好meet,工具优化的比较困难,可能反而会导致面积越优化越大。

4.DVFS技术。DVFS(Dynamic Voltage and Frequency Scaling)动态电压频率调节本质上是一种低功耗技术,目的是根据的芯片当时的实际功耗需要设定工作电压和时钟频率,这样可以保证提供的功率既满足要求又不会过剩,从而可以降低功耗。比如数字芯片中,CPU模块(比如8核cpu),在需要跑分的时候,将给cpu供电的电压通过软件调节到更高的电压(overdrive),获得一个更高的频率。在实际某个应用场景下,可能cpu只需要一个较低的频率时,可以将电压调节成一个较低的电压(underdrive)来实现。

一味的降频降压当然是不能降低功耗的,因为低频下运行可能使系统处理任务的时长增加,从而整体上可能反而增加了功耗。所以DVFS的核心是动态调整的策略,其目的是根据当时的系统负载实时调整,从而提供满足当时性能要求的最低功率,也就达到了最低功耗。制定调整策略前,先找出系统中的耗电大户即CPU GPU这些模块。需要统计出这些模块的负载情况,基本的策略当然是工作负载增加则升频升压,工作负载降低则降频降压。

5.Well bias。这个方法可以动态调整偏置电压,从而实现降低功耗的目的。

好了,今天的码字就到这里了,原创不容易,喜欢的可以帮忙转发,小编在此先谢过!