【连载】计算机组成原理 --- 第四章指令系统

本章主要内容:

(一)指令格式

1.指令的基本格式

2.定长操作码指令格式

3.扩展操作码指令格式

(二)指令的寻址方式

1.有效地址的概念

2.数据寻址和指令寻址

3.常见寻址方式

(三)CISC和RISC的基本概念

4.1指令格式

指令(又称机器指令)是指示计算机执行某种操作的命令,是计算机运行的最小功能单位。一台计算机的所有指令的集合构成该机的指令系统,也称为指令集。指令系统是计算机的主要属性,位于硬件和软件的交界面上。

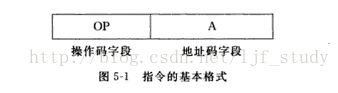

4.1.1 指令的基本格式

一条指令就是机器语言的一个语句,它是一组有意义的二进制代码,指令的基本格式如:操作码字段+地址码字段,其中操作码指明了指令的操作性质及功能,地址码则给出了操作数或操作数的地址

一条指令实际上包括两种信息即操作码和地址码。操作码(OperationCode,OP)用来表示该指令所要完成的操作(如加、减、乘、除、数据传送等),其长度取决于指令系统中的指令条数。地址码用来描述该指令的操作对象,它或者直接给出操作数,或者指出操作数的存储器地址或寄存器地址(即寄存器名)。

指令包括操作码域和地址域两部分。根据地址域所涉及的地址数量,常见的指令格式有以下几种。

①三地址指令:一般地址域中A1、A2分别确定第一、第二操作数地址,A3确定结果地址。下一条指令的地址通常由程序计数器按顺序给出。

②二地址指令:地址域中A1确定第一操作数地址,A2同时确定第二操作数地址和结果地址。

③单地址指令:地址域中A 确定第一操作数地址。固定使用某个寄存器存放第二操作数和操作结果。因而在指令中隐含了它们的地址。

④零地址指令:在堆栈型计算机中,操作数一般存放在下推堆栈顶的两个单元中,结果又放入栈顶,地址均被隐含,因而大多数指令只有操作码而没有地址域。

⑤可变地址数指令:地址域所涉及的地址的数量随操作定义而改变。如有的计算机的指令中的地址数可少至 0个,多至6个。

4.1.2 扩展操作码指令格式

参考 : http://blog.csdn.net/u011240016/article/details/52717315

需要建立的一种直观的认知是:既然是扩展操作码,就意味着操作码的位数越变越多!

之所以这么强调,是因为常常混淆了操作码的扩展方向。

再看扩展的原理:

假设指令字长是16位,平均劈开成4份,高位4位用作操作码,低12位分别用作三个地址码。那么操作码的个数就是四个二进制所能表达的离散数目:2^4=16

OK,如果地址码只能做地址码,这是最终的结局了。

但是,如果地址码可以化身为操作码,这并不难对吧,毕竟都是二进制的数位而已。

非常粗略的认为,现在第一个地址4位也用作操作码,那么总的看来就是高8位用作操作码,低8位用作两个地址码了。

按理说2^8=256,即,共计有256种操作码。

虽然,用8位和用4位各自表达操作码,互不干扰的。但是,实际上呢,单操作码只有15条,且二地址的操作码只有16条,如果还要继续扩展,二地址的也只有15条了!

为什么差别这么大? 答案是两个原则不可以破:

不允许短码是长码的前缀

各指令的操作码一定不能重复

为了满足第一条,我们看8位操作码的时候,前面四位全是四位操作码已经出现过的!

所以,设计思路只能变成:前面四位只用15种离散状态,保留一个给二地址扩展用。因此,8位操作码,实际上限定了高4位的值,只是低四位可以离散,共16种状态,要想再继续扩展,自己最多只敢用15种,还得保留一个种子呢!

4.2 指令的寻址方式

参考: http://blog.csdn.net/hanchaoman/article/details/9187093(先存着慢慢看。。)

一、立即寻址方式

操作数作为指令的一部分而直接写在指令中,这种操作数称为立即数,这种寻址方式也就称为立即数寻址方式。立即数可以是8位、16位或32位,该数值紧跟在操作码之后。如果立即数为16位或32位,那么,它将按“高高低低”的原则进行存储。例如:

MOV AH, 80H ADD AX, 1234H MOV ECX, 123456H

MOV B1, 12H MOV W1, 3456H ADD D1, 32123456H

其中:B1、W1和D1分别是字节、字和双字单元。

以上指令中的第二操作数都是立即数,在汇编语言中,规定:立即数不能作为指令中的第二操作数。该规定与高级语言中“赋值语句的左边不能是常量”的规定相一致。

立即数寻址方式通常用于对通用寄存器或内存单元赋初值。图是指令“MOV AX, 4576H”存储形式和执行示意图。

二、寄存器寻址方式

指令所要的操作数已存储在某寄存器中,或把目标操作数存入寄存器。把在指令中指出所使用寄存器(即:寄存器的助忆符)的寻址方式称为寄存器寻址方式。

指令中可以引用的寄存器及其符号名称如下:

8位寄存器有:AH、AL、BH、BL、CH、CL、DH和DL等;

16位寄存器有:AX、BX、CX、DX、SI、DI、SP、BP和段寄存器等;

32位寄存器有:EAX、EBX、ECX、EDX、ESI、EDI、ESP和EBP等。

寄存器寻址方式是一种简单快捷的寻址方式,源和目的操作数都可以是寄存器。

1、源操作数是寄存器寻址方式

如:ADD VARD, EAX ADD VARW, AX MOV VARB, BH等。

其中:VARD、VARW和VARB是双字,字和字节类型的内存变量。在第4章将会学到如何定义它们。

2、目的操作数是寄存器寻址方式

如:ADD BH, 78h ADD AX, 1234h MOV EBX, 12345678H等。

3、源和目的操作数都是寄存器寻址方式

如:MOV EAX, EBX MOV AX, BX MOV DH, BL等。

由于指令所需的操作数已存储在寄存器中,或操作的结果存入寄存器,这样,在指令执行过程中,会减少读/写存储器单元的次数,所以,使用寄存器寻址方式的指令具有较快的执行速度。通常情况下,我们提倡在编写汇编语言程序时,应尽可能地使用寄存器寻址方式,但也不要把它绝对化。

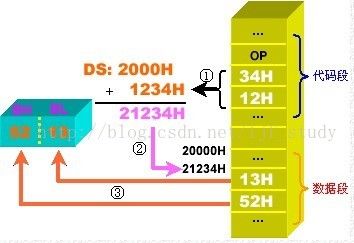

三:直接寻址方式

指令所要的操作数存放在内存中,在指令中直接给出该操作数的有效地址,这种寻址方式为直接寻址方式。

在通常情况下,操作数存放在数据段中,所以,其物理地址将由数据段寄存器DS和指令中给出的有效地址直接形成,但如果使用段超越前缀,那么,操作数可存放在其它段。

例:假设有指令:MOV BX, [1234H],在执行时,(DS)=2000H,内存单元21234H的值为5213H。问该指令执行后,BX的值是什么?

解:根据直接寻址方式的寻址规则,把该指令的具体执行过程用下图来表示。

从图中,可看出执行该指令要分三部分:

由于1234H是一个直接地址,它紧跟在指令的操作码之后,随取指令而被读出;

访问数据段的段寄存器是DS,所以,用DS的值和偏移量1234H相加,得存储单元的物理地址:21234H;

取单元21234H的值5213H,并按“高高低低”的原则存入寄存器BX中。

所以,在执行该指令后,BX的值就为5213H。

由于数据段的段寄存器默认为DS,如果要指定访问其它段内的数据,可在指令中用段前缀的方式显式地书写出来。

下面指令的目标操作数就是带有段前缀的直接寻址方式。

MOV ES:[1000H], AX

直接寻址方式常用于处理内存单元的数据,其操作数是内存变量的值,该寻址方式可在64K字节的段内进行寻址。

注意:立即寻址方式和直接寻址方式的书写格式的不同,直接寻址的地址要写在括号“[”,“]”内。在程序中,直接地址通常用内存变量名来表示,如:MOV BX, VARW,其中,VARW是内存字变量。

试比较下列指令中源操作数的寻址方式(VARW是内存字变量):

MOV AX, 1234H MOV AX, [1234H] ;前者是立即寻址,后者是直接寻址

MOV AX, VARW MOV AX, [VARW] ;两者是等效的,均为直接寻址

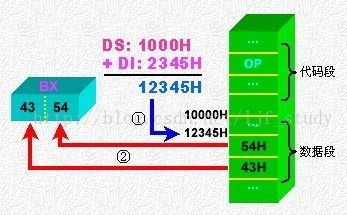

四:寄存器间接寻址方式

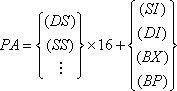

操作数在存储器中,操作数的有效地址用SI、DI、BX和BP等四个寄存器之一来指定,称这种寻址方式为寄存器间接寻址方式。该寻址方式物理地址的计算方法如下:

寄存器间接寻址方式读取存储单元的原理如图所示。

在不使用段超越前缀的情况下,有下列规定:

若有效地址用SI、DI和BX等之一来指定,则其缺省的段寄存器为DS;

若有效地址用BP来指定,则其缺省的段寄存器为SS(即:堆栈段)。

例:假设有指令:MOV BX,[DI],在执行时,(DS)=1000H,(DI)=2345H,存储单元12345H的内容是4354H。问执行指令后,BX的值是什么?

解:根据寄存器间接寻址方式的规则,在执行本例指令时,寄存器DI的值不是操作数,而是操作数的地址。该操作数的物理地址应由DS和DI的值形成,即:

PA=(DS)*16+DI=1000H*16+2345H=12345H。

所以,该指令的执行效果是:把从物理地址为12345H开始的一个字的值传送给BX。

其执行过程如图所示。

五:寄存器相对寻址方式

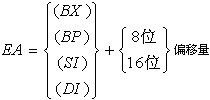

操作数在存储器中,其有效地址是一个基址寄存器(BX、BP)或变址寄存器(SI、D

I)的内容和指令中的8位/16位偏移量之和。其有效地址的计算公式如公式所示。

在不使用段超越前缀的情况下,有下列规定:

若有效地址用SI、DI和BX等之一来指定,则其缺省的段寄存器为DS;

若有效地址用BP来指定,则其缺省的段寄存器为SS。

指令中给出的8位/16位偏移量用补码表示。在计算有效地址时,如果偏移量是8位,则进行符号扩展成16位。当所得的有效地址超过0FFFFH,则取其64K的模。

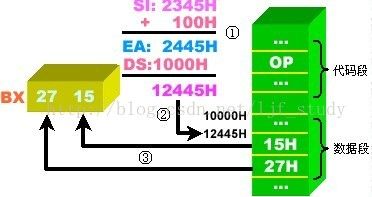

例:假设指令:MOV BX, [SI+100H],在执行它时,(DS)=1000H,(SI)=2345H,内存单元12445H的内容为2715H,问该指令执行后,BX的值是什么?

解:根据寄存器相对寻址方式的规则,在执行本例指令时,源操作数的有效地址EA为:

EA=(SI)+100H=2345H+100H=2445H

该操作数的物理地址应由DS和EA的值形成,即:

PA=(DS)*16+EA=1000H*16+2445H=12445H。

所以,该指令的执行效果是:把从物理地址为12445H开始的一个字的值传送给BX。

其执行过程如图所示。

六:基址加变址寻址方式

操作数在存储器中,其有效地址是一个基址寄存器(BX、BP)和一个变址寄存器(SI、DI)的内容之和。其有效地址的计算公式如公式所示。

在不使用段超越前缀的情况下,规定:如果有效地址中含有BP,则缺省的段寄存器为SS;否则,缺省的段寄存器为DS。

例:假设指令:MOV BX, [BX+SI],在执行时,(DS)=1000H,(BX)=2100H,(SI)=0011H,内存单元12111H的内容为1234H。问该指令执行后,BX的值是什么?

解:根据基址加变址寻址方式的规则,在执行本例指令时,源操作数的有效地址EA为:

EA=(BX)+(SI)=2100H+0011H=2111H

该操作数的物理地址应由DS和EA的值形成,即:

PA=(DS)*16+EA=1000H*16+2111H=12111H

所以,该指令的执行效果是:把从物理地址为12111H开始的一个字的值传送给BX。

其执行过程如图所示。

七:相对基址加变址寻址方式

操作数在存储器中,其有效地址是一个基址寄存器(BX、BP)的值、一个变址寄存器(SI、DI)的值和指令中的8位/16位偏移量之和。其有效地址的计算公式如公式所示。

在不使用段超越前缀的情况下,规定:如果有效地址中含有BP,则其缺省的段寄存器为SS;否则,其缺省的段寄存器为DS。

指令中给出的8位/16位偏移量用补码表示。在计算有效地址时,如果偏移量是8位,则进行符号扩展成16位。当所得的有效地址超过0FFFFH,则取其64K的模。

例:假设指令:MOV AX, [BX+SI+200H],在执行时,(DS)=1000H,(BX)=2100H,(SI)=0010H,内存单元12310H的内容为1234H。问该指令执行后,AX的值是什么?

解:根据相对基址加变址寻址方式的规则,在执行本例指令时,源操作数的有效地址EA为:

EA=(BX)+(SI)+200H=2100H+0010H+200H=2310H

该操作数的物理地址应由DS和EA的值形成,即:

PA=(DS)*16+EA=1000H*16+2310H=12310H

所以,该指令的执行效果是:把从物理地址为12310H开始的一个字的值传送给AX。其执行过程如图所示。

从相对基址加变址这种寻址方式来看,由于它的可变因素较多,看起来就显得复杂些,但正因为其可变因素多,它的灵活性也就很高。比如:

用D1[i]来访问一维数组D1的第i个元素,它的寻址有一个自由度,用D2[i][j]来访问二维数组D2的第i行、第j列的元素,其寻址有二个自由度。多一个可变的量,其寻址方式的灵活度也就相应提高了。

相对基址加变址寻址方式有多种等价的书写方式,下面的书写格式都是正确的,并且其寻址含义也是一致的。

MOV AX, [BX+SI+1000H] MOV AX, 1000H[BX+SI]

MOV AX, 1000H[BX][SI] MOV AX, 1000H[SI][BX]

但书写格式BX [1000+SI]和SI[1000H+BX]等是错误的,即所用寄存器不能在“[“,”]”之外,该限制对寄存器相对寻址方式的书写也同样起作用。

相对基址加变址寻址方式是以上7种寻址方式中最复杂的一种寻址方式,它可变形为其它类型的存储器寻址方式。

4.3 CISC和RISC的基本概念

参考 : http://mengx.blog.51cto.com/157987/47506

复杂指令集计算机(CISC)

长期来,计算机性能的提高往往是通过增加硬件的复杂性来获得.随着集成电路技术.特别是VLSI(超大规模集成电路)技术的迅速发展,为了软件编程方便和提高程序的运行速度,硬件工程师采用的办法是不断增加可实现复杂功能的指令和多种灵活的编址方式.甚至某些指令可支持高级语言语句归类后的复杂操作.至使硬件越来越复杂,造价也相应提高.为实现复杂操作,微处理器除向程序员提供类似各种寄存器和机器指令功能外.还通过存于只读存贮器(ROM)中的微程序来实现其极强的功能 ,傲处理在分析每一条指令之后执行一系列初级指令运算来完成所需的功能,这种设计的型式被称为复杂指令集计算机(ComplexInstruction Set Computer-CISC)结构.一般CISC计算机所含的指令数目至少300条

以上,有的甚至超过500条.

CISC特点:(1)指令系统复杂庞大,指令数目一般为200条以上;(2)指令的长度不固定,指令格式多,寻址方式多;(3)可以访存的指令不受限制;(4)各种指令使用频度相差很大(5)各种指令执行时间相差很大,大多数指令需多个时钟周期才能完成。(6)控制器大多采用微程序控制(7)难以用优化编译生成高校的目标代码程序。

精简指令集计算机(RISC)

CISC存在许多缺点.首先.在这种计算机中.各种指令的使用率相差悬殊:一个典型程序的运算过程所使用的80%指令.只占一个处理器指令系统的20%.事实上最频繁使用的指令是取、存和加这些最简单的指令.这样一来,长期致力于复杂指令系统的设计,实际上是在设计一种难得在实践中用得上的指令系统的处理器.同时.复杂的指令系统必然带来结构的复杂性.这不但增加了设计的时间与成本还容易造成设计失误.因而.针对CISC的这些弊病.帕特逊等人提出了精简指令的设想即指令系统应当只包含那些使用频率很高的少量指令.并提供一些必要的指令以支持操作系统和高级语言.按照这个原则发展而成的计算机被称为精简指令集计算机(ReducedInstruction Set Computer-RISC)结构.简称RISC.

(1)大多数指令在单周期内完成,便于流水线操作执行;(2)采用固定长度的指令格式,指令归整、简单、基本寻址方式只有 2~3 种;(3)硬布线控制逻辑,不用或少用微程序控制。使得大多数指令在单周期内执行完成,以减少指令解释时间;(4)大量使用寄存器,数据处理指令只对寄存器进行操作,只有LOAD/STORE指令可以访问存储器,以提高指令的执行效率;(5)优化编译技术。

比较:CISC更加专注于高性能但同时高功耗的实现,而RISC则专注于小尺寸低功耗领域。实际上也有很多事情CISC更加合适,而另外一些事情则是RISC更加合适,比如在执行高密度的运算任务的时候CISC就更具备优势,而在执行简单重复劳动的时候RISC就能占到上风。