Vivado入门使用指南之----按键消抖(仿真与在线逻辑分析仪仿真-不使用ip)

本博文参考米联客提供的教程,不太适合一点基础都没有的小白,不会讲解代码思路,只是编译工具的使用

1,概述

本实验对前文没有进行的仿真进行测试以及在线逻辑分析使用的尝试(不使用IP)。本文通过(*mark_debug = "true"*) 进行对信号的捕捉检测。

2,代码

module key #

(

parameter CLK_FREQ = 100000000

)

(

input clk_i,

input key_i,

output key_cap

);

//10ms

parameter CNT_10MS = (CLK_FREQ/100 - 1'b1);

parameter KEY_S0 = 2'd0;

parameter KEY_S1 = 2'd1;

parameter KEY_S2 = 2'd2;

parameter KEY_S3 = 2'd3;

reg [24:0] cnt10ms = 25'd0;

(*mark_debug = "true"*) reg [1:0] key_s = 2'b0;

(*mark_debug = "true"*) reg [1:0] key_s_r = 2'b0;

(*mark_debug = "true"*) wire en_10ms ;

assign en_10ms = (cnt10ms == CNT_10MS);

assign key_cap = (key_s==KEY_S2)&&(key_s_r==KEY_S1);

always @(posedge clk_i)

begin

if(cnt10ms < CNT_10MS)

cnt10ms <= cnt10ms + 1'b1;

else

cnt10ms <= 25'd0;

end

always @(posedge clk_i)

begin

key_s_r <= key_s;

end

always @(posedge clk_i)

begin

if(en_10ms)

begin

case(key_s)

KEY_S0:

begin

if(!key_i)

key_s <= KEY_S1;

end

KEY_S1:

begin

if(!key_i)

key_s <= KEY_S2;

else

key_s <= KEY_S0;

end

KEY_S2:

begin

if(key_i)

key_s <= KEY_S3;

end

KEY_S3:

begin

if(key_i)

key_s <= KEY_S0;

else

key_s <= KEY_S2;

end

endcase

end

end

endmodule

以上代码中,首先把系统时钟做分频,产生 10ms 的分配时钟使能信号。在设计的状态机中,分 4 个状态

KEY_S0:判断按键是否按下,如果是,转移到状态 KEY_S1;

KEY_S1:10ms 后再次判断按键是否按下,如果是,转移状态到 KEY_S2,否则继续回到 KEY_S0;

KEY_S2:判断按键是否抬起,如果是,转移状态到 KEY_S3

KEY_S1:10ms 后再次判断按键是否抬起,如果是,转移状态到 KEY_S0,否则继续回到 KEY_S2;

当状态从 KEY_S1 转到 KEY_S2 代表依次按钮按下 key_cap 输出一次高电平。

调用 key 模块

module Key_Jitter(

input clk_i,

input rst_n_i,

input key_i,

output [3:0] led_o

);

(*mark_debug = "true"*) reg [3:0] led_o;

(*mark_debug = "true"*) wire key_cap;

always @(posedge clk_i)

begin

if(!rst_n_i)

begin

led_o <= 4'b0000;

end

else

if(key_cap)

begin

led_o <= ~led_o;

end

end

key#(

.CLK_FREQ(100000000))key0

(

.clk_i(clk_i),

.key_i(key_i),

.key_cap(key_cap)

);

endmodule

每次 key_cap 有效,都会翻转一次 LED 的输出。

仿真代码

module Key_Jitter_TB;

// Inputs

reg clk_i;

reg rst_n_i;

reg key_i;

wire [3:0] led_o;

// Instantiate the Unit Under Test (UUT)

Key_Jitter uut (

.clk_i(clk_i),

.rst_n_i(rst_n_i),

.key_i(key_i),

.led_o(led_o)

);

initial

begin

// Initialize Inputs

clk_i = 0;

forever

#5 clk_i=~clk_i;

end

initial

begin

// Initialize Inputs

rst_n_i = 0;

#100;

rst_n_i=1;

key_i = 1;

#10000;

forever

begin

key_i = 0;

// Wait 100 ns for global reset to finish

#100;

key_i=1; #1000;

key_i=0; #1000;

key_i=1; #2000;

key_i=0; #5000;

#50000000;

key_i=1;

key_i=0; #1000;

key_i=1; #2000;

key_i=0; #1000;

key_i=1; #2000;

#50000000;

key_i=0;

end

end

endmodule

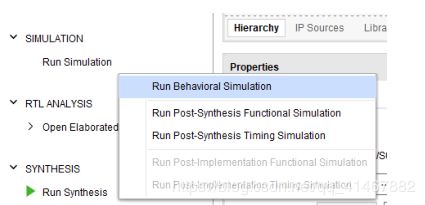

接下来进行仿真

3,仿真

进入后即可。添加信号,或是重新进行仿真等待和ISE很像,可以使用简单的命令语句或者直接在UI界面进行操作都很简单。

![]()

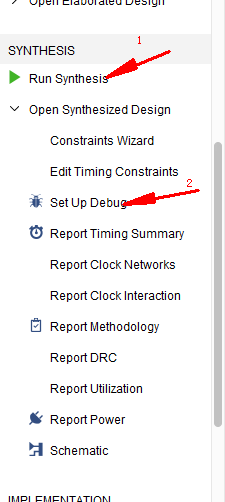

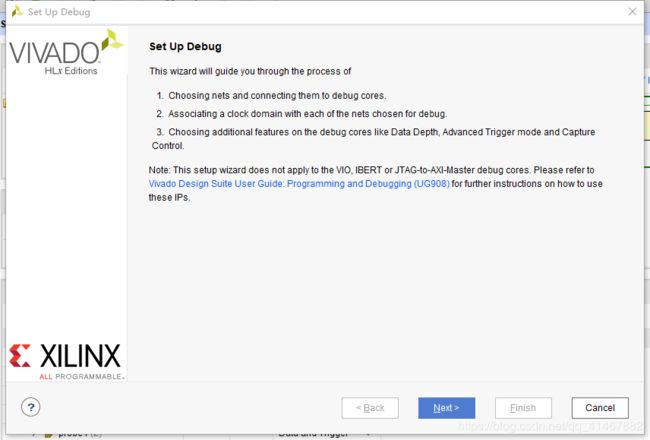

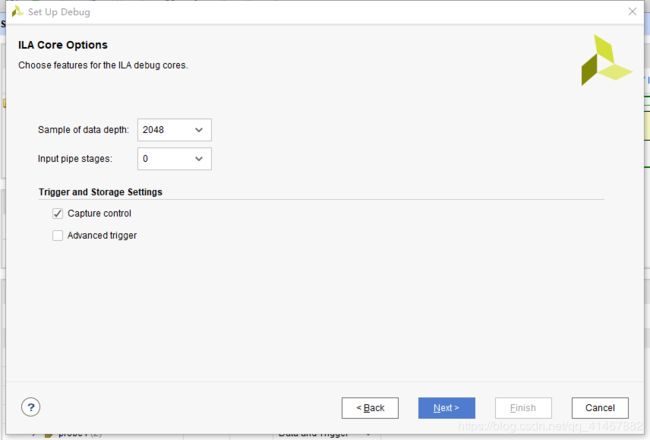

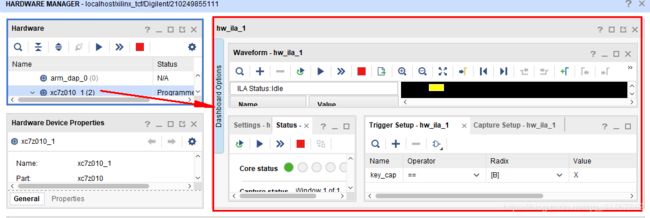

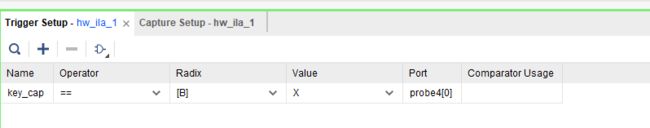

4,Chipscope 在线逻辑分析仪仿真

将(*mark_debug = "true"*)添加到需要观察的信号前面即可,前面代码以给出。

step1,点击next

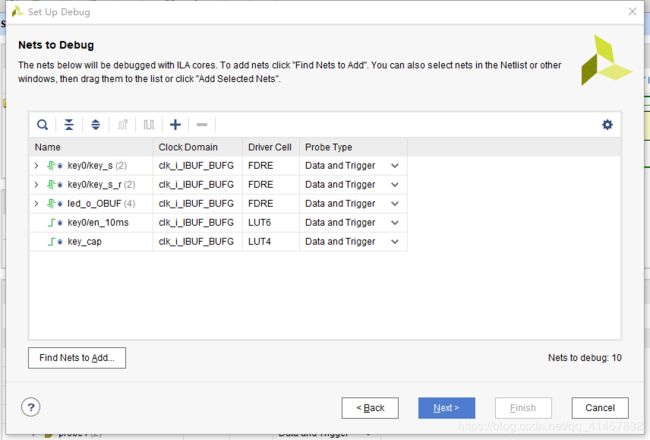

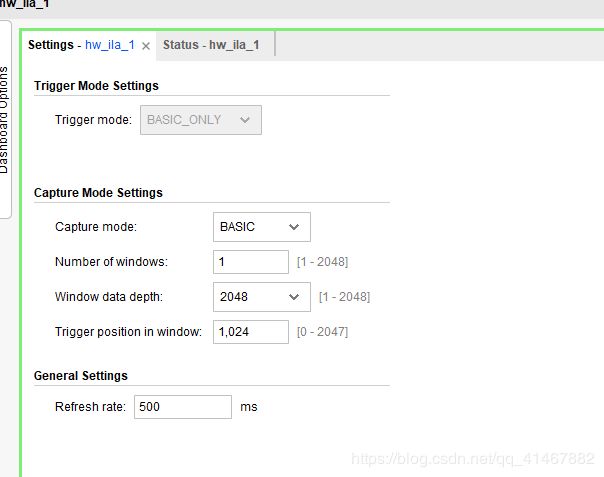

step2,设置

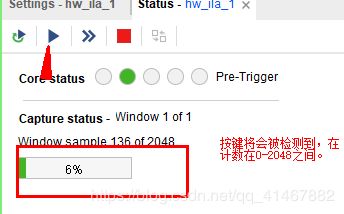

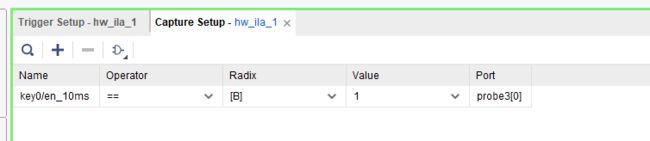

以下是这只在线逻辑分析仪的采样深度,使用的是 FPGA 的 BRAM,以及设置 Captrue control,对于这种超慢信号,

XILINX 的在线逻辑分析低于 20M 采样速度的,波形窗口就不会显示波形,这个 XILINX 也没有特别说明过,但是

通过设置 Captrue control,可以用我们这里的 en_10ms 来作为扑捉控制,而采样时钟依然用系统时钟。

以上是教程中的原话,不是很理解。以后补上。

最后点击结束即可。

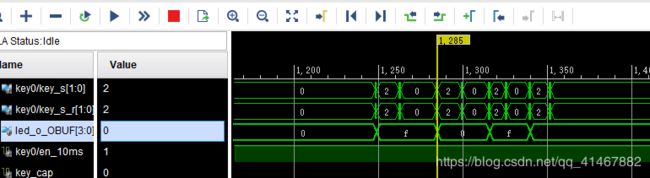

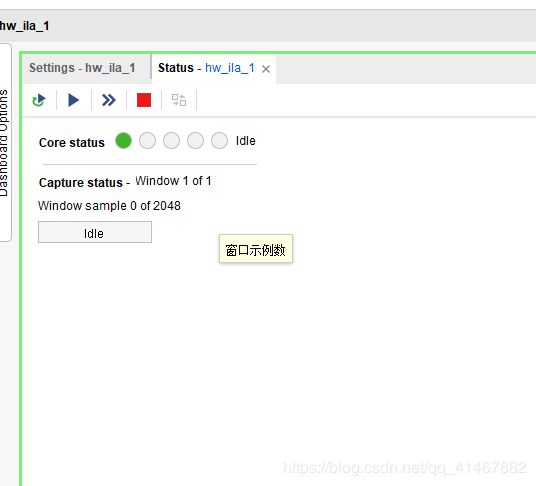

5,结果观察

这里没有给出管脚约束。前面教程有。下来直接连接下载到开发板即可自动弹出一个界面。

Captrue mode 一定要设置为 BASIC

Window data depth 为采样深度设置为 2048 最大

Trigger position inwindow 设置为 1024

以上参数都可以根据需要用户自行设置

随意按下按键

等待到2048即可观察到检测的信号,这里是状态机的跳转强情况