ZYNQ7000 pl330DMA vs CPU读DDR速率分析

单核freeRtos环境:

Zynq7045芯片平台,core0单核freeRtos系统。此环境不需要特殊修改,自带的两个demo均可跑过。

在freertos的bsp中的描述文件system.mss可找到如下的两个相关demo。

![]()

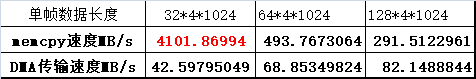

根据帧长的不同,通过CPU读和PL330MDA读两个不同方式,做了如下验证:

linxu+freeRtos AMP双核环境:

首先解决DMA在AMP环境下无法正常运行的问题:

问题现象:通过DMA搬运数据时,数据概率性搬运成功。

问题分析:首先排除了中断相关的配置,中断配置与单核环境一致,排除此原因;

查看DMA搬运数据的过程中发现有L2cache相关的操作,由于SCU不能保证L2cache的同步性,在DMA传输时需要软件保证数据的一致性。而在amp环境下core1 freertos BSP定义了-DUSE_AMP=1 ,此定义导致了操作L2cache的接口无效。做了如下代码中的修改,DMA终于可以成功搬运数据了。

涉及的代码及两个接口的区别:

int XDmaPs_Start(XDmaPs *InstPtr, unsigned int Channel,

XDmaPs_Cmd *Cmd,

int HoldDmaProg)

{

......

if (Cmd->ChanCtrl.SrcInc && XDmaPs_IsCacheable(Cmd->BD.SrcAddr)) {

//Xil_DCacheFlushRange(Cmd->BD.SrcAddr, Cmd->BD.DstLength); 替换为重新封装的接口

Xil_DCacheFlushRange_OpenAMP(Cmd->BD.SrcAddr, Cmd->BD.DstLength);

}

if (Cmd->ChanCtrl.DstInc && XDmaPs_IsCacheable(Cmd->BD.DstAddr)) {

//Xil_DCacheInvalidateRange(Cmd->BD.DstAddr, Cmd->BD.DstLength);

Xil_DCacheInvalidateRange_OpenAMP(Cmd->BD.DstAddr, Cmd->BD.DstLength);

}

.....

}

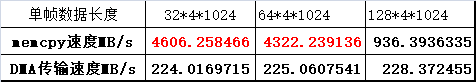

AMP测试条件1:

Zynq7045芯片平台,Core0跑Linux,Core1跑FreeRTOS,通过OpenAMP框架来启动Core1-FreeRTOS和核间通信。L2cache LockdownbyMaster分配256K给core0,256K给core1。

AMP测试条件2:

Zynq7045芯片平台,Core0跑Linux,Core1跑FreeRTOS,通过OpenAMP框架来启动Core1-FreeRTOS和核间通信。L2cache LockdownbyMaster分配256K给core0,256K给core1,core0 memtester 100M 100:

对比以上测试数据可得出如下结论:

1.不管是单核环境还是双核环境CPU搬运数据速率远大于pl330DMA搬运数据速率

2.单核环境与双核环境速率对比,cache的大小对cpu搬运数据和对pl330DMA搬运数据影响都较明显

3.core0对内存资源的占用率影响core1的pl330DMA数据传输速率,而对core1的cpu搬运数据影响不大

4.单核128K,256K,双核128K速率异常高,应该是数据在L2cache完成交换

5.第3行拷贝速度下降,可能是Core0做memtester影响到Core1访问总线或DDR的时延了