ZYNQ7000双核AMP工作方式下如何共享L2 Cache

运行环境:

Zynq7045芯片平台,Core0跑Linux,Core1跑FreeRTOS,通过OpenAMP框架来启动Core1-FreeRTOS和核间通信。

问题现象:

目前发现Core0-Linux执行2MB以上DDR数据的memcpy操作或者memtester 1M 1,Core1-FreeRTOS的运行性能就会受到影响。

可能的原因:

在AMP模式中,core 0与core 1共用512K L2 Cache,这势必会引起两个核的Cache竞争问题。

通常情况下,L2 Cache被core 0,core 1共享。core 0的内存访问操作可能会清除core 1所使用的L2缓存内容,从而使core 1的软件性能有不确定性。

尤其是架构为AMP时,这种不确定性会造成系统运行不正常。

问题验证步骤:

1.Core0-Linux初始化L2-cache,Core1-FreeRTOS BSP不对L2-cache初始化,Core1-FreeRTOS DMA搬运数据

core0的memtester 100M 1 操作影响core1的响应速度

2.Core0-Linux不初始化L2-cache,Core1-FreeRTOS BSP对L2-cache初始化,Core1-FreeRTOS DMA搬运数据

core0的memtester 100M 1 操作影响core1的响应速度

3.Core0-Linux不初始化L2-cache,Core1-FreeRTOS BSP对L2-cache初始化,lockdown by master方法,将L2-Cache空间一半用于Core0-Linux,一半用于缓存Core1-FreeRTOS的数据,Core1-FreeRTOS DMA搬运数据

网口不通,core0的memtester 100M 1 操作影响core1的响应速度

4.Core0-Linux不初始化L2-cache,Core1-FreeRTOS BSP对L2-cache初始化,lockdown by master方法,将L2-Cache空间全部用于缓存Core1-FreeRTOS的数据,Core1-FreeRTOS DMA搬运数据

core0网口OK,core0启动速度变慢,core0的memtester 100M 1操作影响core1的响应速度

5.Core0-Linux不初始化L2-cache,Core1-FreeRTOS BSP对L2-cache初始化,lockdown by master方法,将L2-Cache空间全部用于缓存Core1-FreeRTOS的数据,Core1-FreeRTOS CPU搬运数据

网口OK,core0启动速度变慢,core0的memtester 100M 1 对core1没有明显的影响

6.Core0-Linux初始化L2-cache,Core1-FreeRTOS BSP不对L2-cache初始化,Core1-FreeRTOS CPU搬运数据

网口OK,core0启动速度不受影响,memtester 100M 1操作影响core1的响应速度

7.Core0-Linux初始化L2-cache,Core1-FreeRTOS BSP不对L2-cache初始化,Core1-FreeRTOS BSP配置lockdown相关寄存器 将L2-Cache空间一半用于Core0-Linux,一半用于缓存Core1-FreeRTOS的数据,CPU搬运数据

网口OK,core0启动速度不受影响,core0的memtester 100M 1 对core1没有明显的影响

core1 boot.s中划分L2 cache的代码:

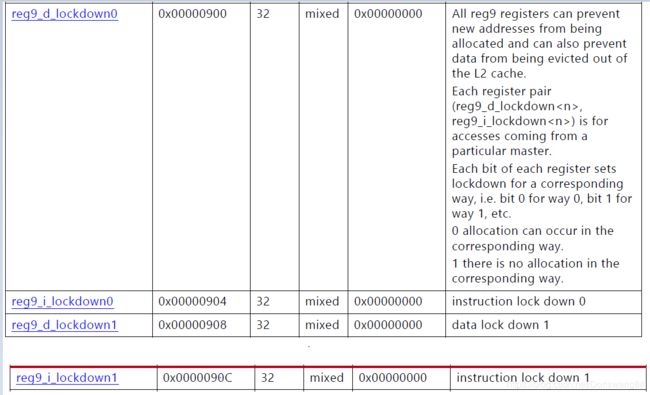

ldr r0, =L2CCDLockdown0 /* Load L2CC base address base + reg9_d_lockdown0 register*/

ldr r1, =0x0f

str r1, [r0] /* lockdown by cpu0 */

ldr r0, =L2CCILockdown0 /* Load L2CC base address base + way register*/

ldr r1, =0x0f

str r1, [r0] /* lockdown by cpu0 */

ldr r0, =L2CCDLockdown1 /* Load L2CC base address base + reg9_d_lockdown1 register */

ldr r1, =0xf0

str r1, [r0] /* lockdown by cpu1 */

ldr r0, =L2CCILockdown1 /* Load L2CC base address base + reg9_i_lockdown1 register */

ldr r1, =0xf0

str r1, [r0] /* lockdown by cpu1 */

结论:

- Core0-Linux和Core1-FreeRTOS共用了L2 Cache空间,导致Core0-Linux执行clean/invalidate的操作影响了Core1-FreeRTOS在L2 Cache中数据的一致性。-- 将DMA读FPGA数据改成CPU读,就不存在一致性问题了

- Core0-Linux读写DDR数据量大时,会比Core1-FreeRTOS占用更多的L2 Cache空间。所以Core0-Linux执行memtester 2M 1,会影响到Core1-FreeRTOS的实时性性能。-- Core0/Core1各lockdown一半的L2 Cache空间,这样Core0/Core1固定只占用一半的L2 Cache空间。不会引起Core0读写DDR数据量大时,占用过多的L2 Cache空间

L2 Cache硬件原理、操作方法研究得不太透彻。以上是实测验证解决的,希望对后来的小伙伴也有些帮助!