Vivado18.3-Zynq PL的开发流程 学习笔记

本文内容学习自正点原子ZYNQ领航者FPGA视频-P6

1.打开软件

安装完成Vivado18.3 SE之后桌面会有4个快捷方式(DE没有System Generator)

Vivado 2018.3:这就是最常用的。也是对PS和PL端开发的主要工具。

Vivado HLS 2018.3:这是HLS(High Level Synthesis)工具,可以实现直接使用 C,C++ 以及 System C 语言对Xilinx的FPGA器件进行编程。用户无需手动创建 RTL,通过高层次综合生成HDL级的IP核,从而加速IP创建。

System Generator:System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,开发DSP用的。

DocNav:Documentation Navigator就是文档导航器,查询官方文档用的。也可以直接在Xinlinx官网找文档。

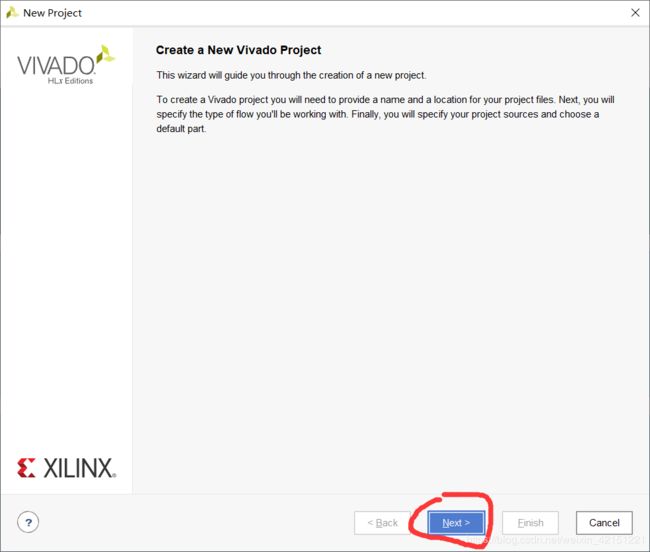

2.创建工程

2.1 打开软件之后点击Creat Project 创建一个新的工程。

2.2工程向导

这里点击Next即可。

2.3设置工程名和路径

选择Create project subdirectory 会自动创建一个和工程名一致的子目录。

点击Next。

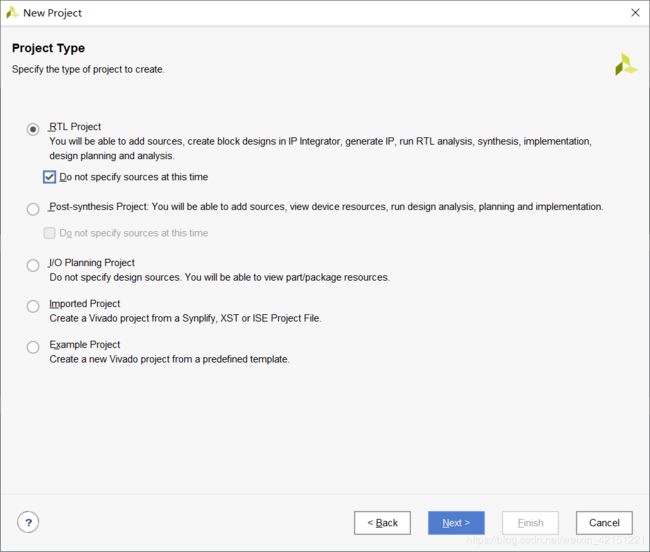

2.3选择工程类型

2.3选择工程类型

RTL Project:普通的工程,需要自己写代码或者添加源文件然后分析、综合、实现。

Post-synthesis Project:设计综合后的工程,需要导入源文件和一些设计综合后的文件等。

I/O Planning Project:![]()

Imported Project:导入一个工程。

Example Project:配置一个示例工程。

我们这里选择RTL Project 并且不添加源文件,创建完工程之后再添加。 然后点击Next。

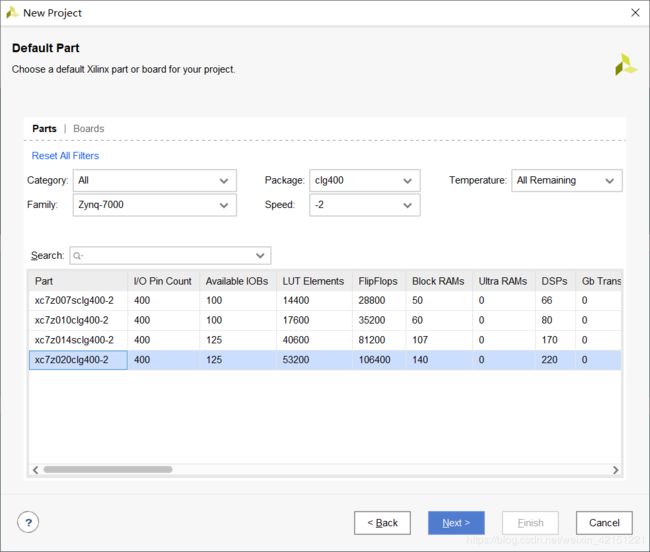

2.4选择器件

参考的是正点原子的教学视频,所以和正点原子的开发板一致。选用xc7z020clg400-2,然后点击Next。

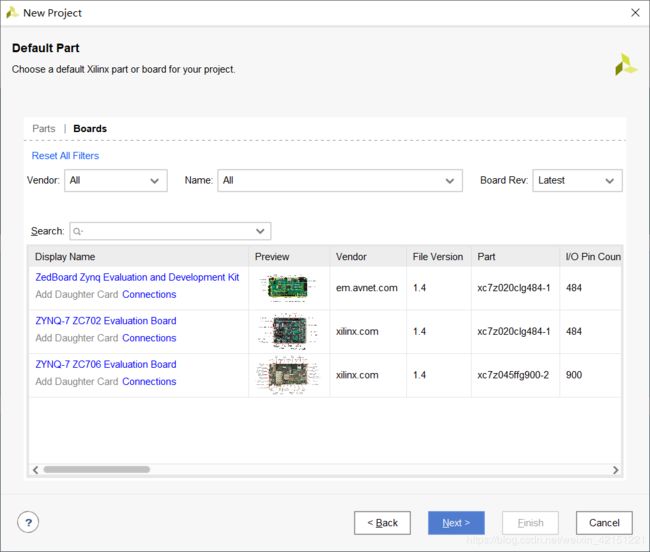

这里除了选择芯片之外,还可以选择Xilinx官方出的开发板。

2.5创建工程的总结

点击Finish完成工程创建。

3.设计输入

3.设计输入

3.1添加/创建源文件

点击Add Sources

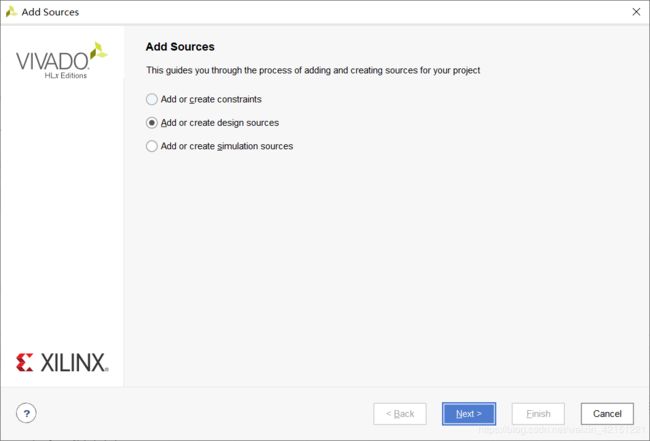

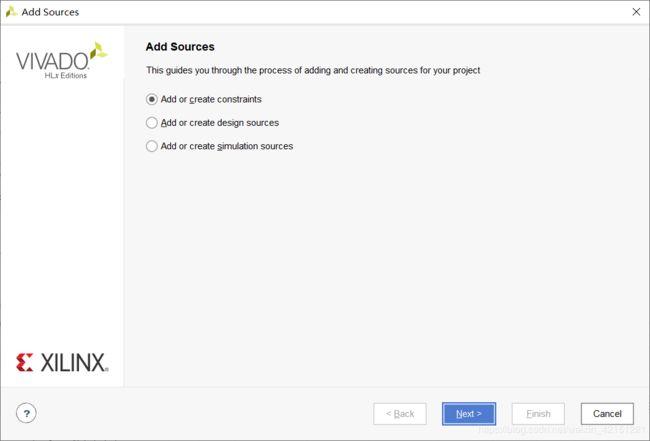

这三个分别是

1.添加/创建约束文件

2.添加/创建设计文件(也就是Verilog文件)

3.添加/创建仿真文件

我们选择添加设计文件。

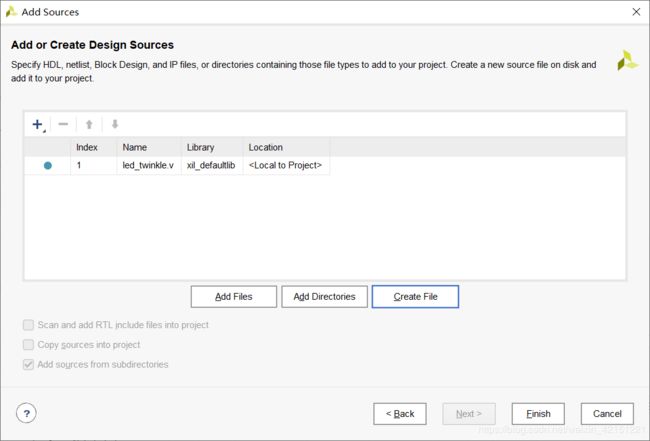

这里可以添加现有的设计文件,也可以选择创建一个全新的文件。选择Create File。

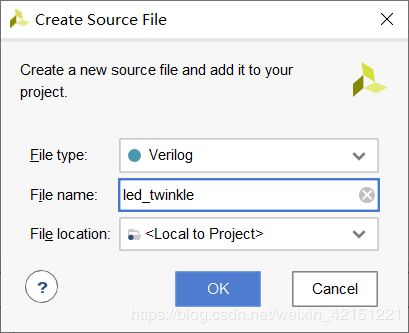

设置文件名和路径,一般将顶层文件名和工程名一致。

添加完成后,这里就多了刚才创立的文件。你可以选择接着添加,或者点击Finish,完成文件的添加。

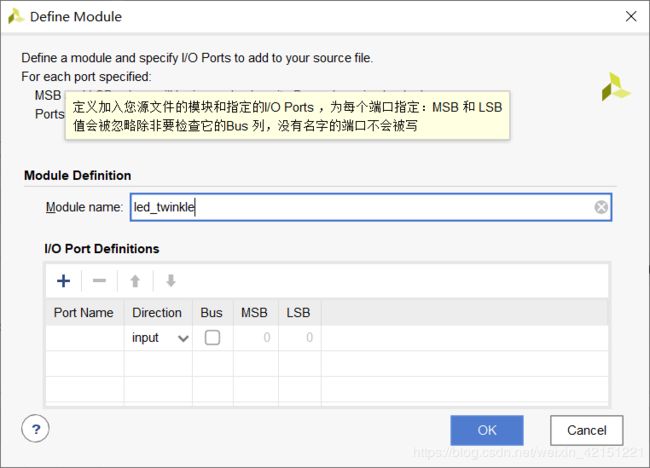

这里提示我们定于模块的端口,可以在文件中用Verilog语言定义,这里直接点击Ok不管他。

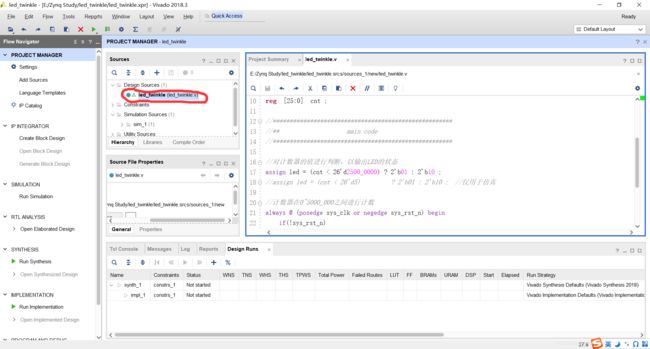

打开新建的文件,然后讲led闪烁的代码复制进去并保存。

4.分析

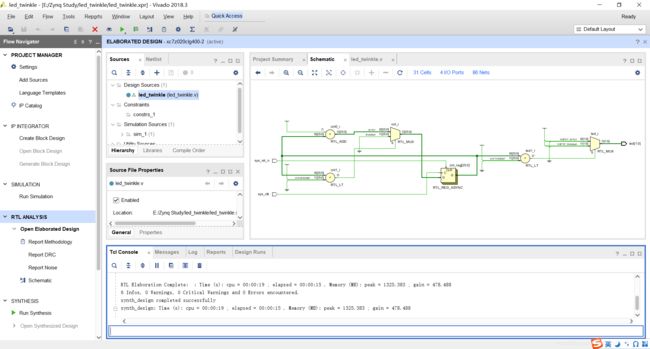

点击Flow Navigator里的Open Elaborated Design开始分析和综合。会对代码进行检错,然后生成RTL原理图。

右侧即为生成的RTL原理图。

5.约束输入

5.1.手动分配管脚。

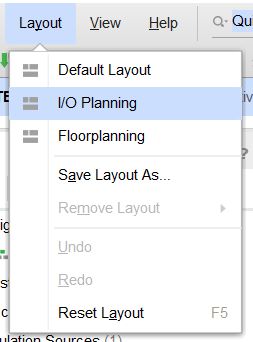

然后点击I/O Planing 分配管脚。

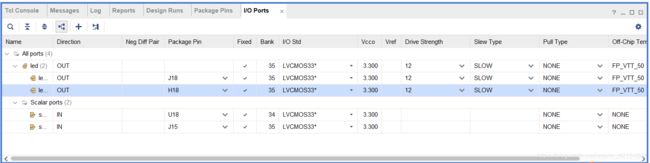

查找原理图选择对应的引脚,因为我们Zynq的PL部分一般都是3.3v,所以这里都选3.3v。然后Ctrl+S 保存。

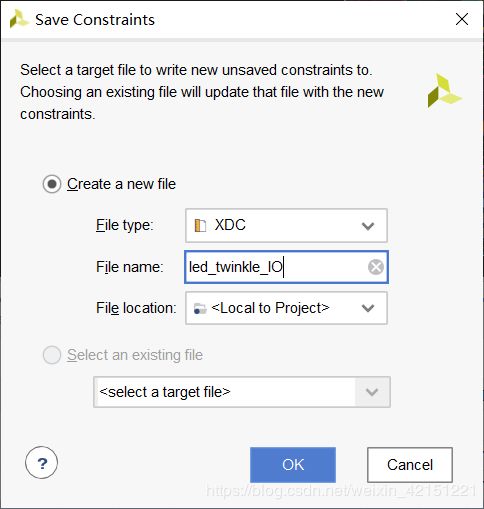

这里是让你给这个引脚分配文件起个名字。

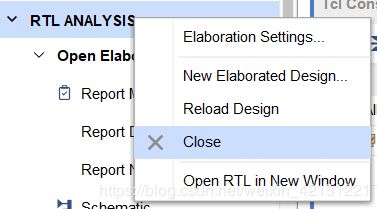

然后就可以将分析页面关闭了

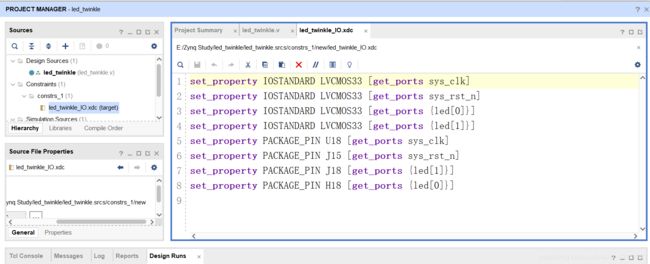

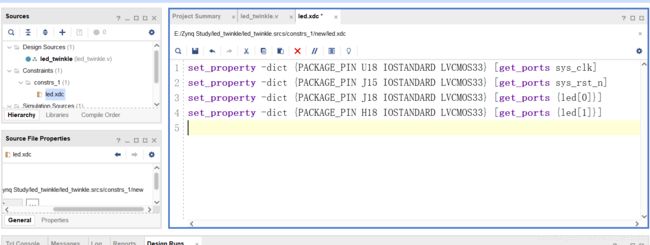

然后就可以在Constraint约束一栏看到我们刚才分配的引脚。引脚分配文件会保存为一个.xdc文件。

5.2 直接创建约束文件

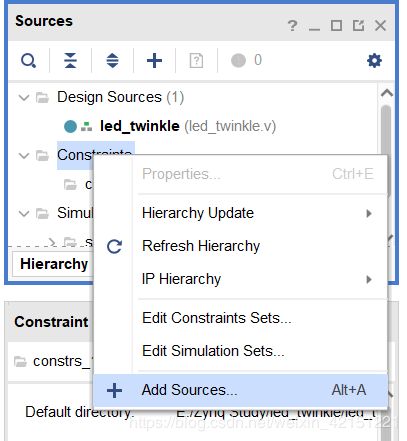

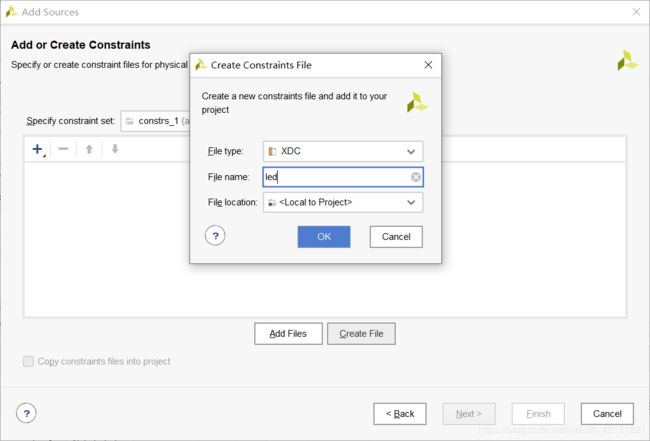

右键Constraints 点击Add Sources

选择第一个添加或创建约束文件。

然后点击Create File 并给他起个名字。

然后将准备好的xdc里的约束复制进去。

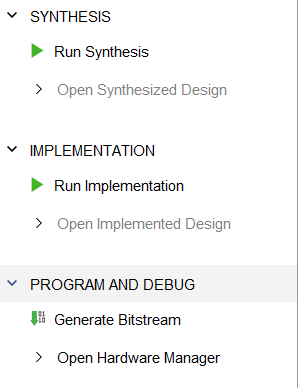

6.综合、实现和生成bit流

直接点Generate Bitstream 综合和实现会自动进行。

这里是设置电脑运行使用的芯片核心数。

点击Project Summary可以查看编译进度。

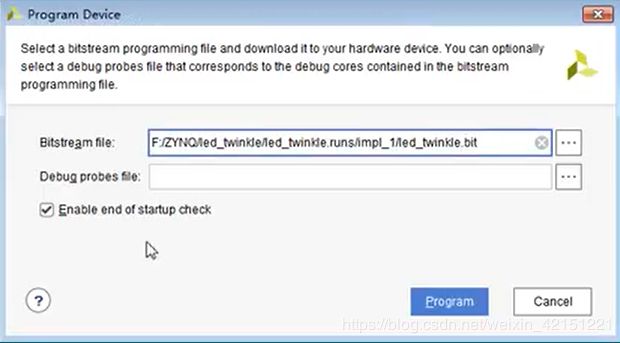

6.下载Bit流

点击Open Hardware Manager

点击Program Device弹出我们的芯片,然后再点xc7z020。

然后我们刚才生成的bit流文件自动就被识别到了。点击Program,即可下载程序。

这样完整的Zynq PL端的开发流程就结束了。

总结一下就是,约束输入也可以放在设计输入之后。