第三章 运算方法与运算器

文章目录

- 定点补码加减法运算

- 补码加减法运算方法

- 溢出及检测

- 溢出检测

- 操作数与运算结果的符号位是否一致

- 最高位的进位和符号位的进位是否一致

- 变形补码

- 补码加减法的逻辑实现

- 移码加减运算及实现逻辑

- 移码的加法运算

- 移码加减法的溢出判断

- 直接采用移码运算的溢出判断方法

- 采用双符号判断

- 定点乘法运算

- 机器数的移位操作

- 原码一位乘法

- 原码一位乘法

- 符号位的确定

- 乘积的数值

- 补码一位乘法

- 运算规则(booth算法)

- 阵列乘法器

- 定点除法运算

- 原码一位除法

- 原码恢复余数法

- 原码不恢复余数法

- 不恢复余数的补码一位除法

- 浮点运算

- 浮点数加减运算

- 阶码和尾数采用补码表示的浮点数加减运算

- IEEE 754浮点数的加减运算

- 浮点数乘法运算

- 浮点数除法运算

- 逻辑运算

- 运算器

- 定点运算器

- 运算前的基本组成单元

- 算术逻辑运算单元

- 通用寄存器组

- 输入输出数据选择控制

- 内部总线

- 运算器的基本结构

- 单总线

- 双总线

- 三总线

- 浮点运算器

- 基本算术逻辑单元的设计

- 基本算术、逻辑部件

- 基本算术逻辑运算单元设计

- 串行进位加法器

- 并行加法器

定点补码加减法运算

补码加减法运算方法

- 补码加法:

[x]补 + [y]补 = [x + y]补 mod M - 补码减法:

[x]补 - [y]补 = [x - y]补 mod M

溢出及检测

运算结果超出数据类型所能表示数据范围的现象称为溢出

溢出检测

操作数与运算结果的符号位是否一致

只有符号相同的数相加,才有可能产生溢出,因此检测运算结果的符号位,是否与操作数一致

设操作数为S1XXXX和S2XXXX,其中S1和S2为他们的符号位,结果为SXXXX,S是结果的标志位,V是溢出标志位,那么

V = S1 && S2 && !S + !S1 && !S2 && S

如果符号位不同,则S1和S2必定是0和1的组合,其结果V一定为0

如果符号位相同,则可能同时为0或者同时为1,这时就要看结果的符号位S了

最高位的进位和符号位的进位是否一致

最高位C和符号位S的进位,如果不同步,则发生了溢出

V = C ^ S

变形补码

变形补码就是用两个位来表示符号位,正数符号位00,负数符号位11

如果运算后的结果为01,则上溢,10则下溢

补码加减法的逻辑实现

- 利用一位全加器(FA)作为基本的加法单元,低位FA的进位,直接送到相邻高位FA的进位输入,构成一个串行进位链

- 进行加法运算时,直接送入全加器,进行减法运算时,减数先求补

- 采用基于变形补码的双符号位溢出检测方法

- 不支持逻辑运算

移码加减运算及实现逻辑

移码的加法运算

- 公式1:

[x]移 + [y]移 = [x + y]移 + 2^n - 公式2:

[x]移 + [y]移 = [x + y]补 - 公式3:

[x]移 + [y]补 = [x + y]移 mod 2^(n+1)

求移码的加法有三种方式

- 直接对两数的移码求和,然后将高位取反

- 直接求出两数和的补码,然后将高位取反

- 用一个数的移码,加另一个数的补码

移码加减法的溢出判断

直接采用移码运算的溢出判断方法

只有符号相同的加法,才会溢出

正数的移码,符号位为1,如果两个正数的移码相加,符号位1+1=0,结果的符号位变成0

因此,移码相加后,符号位与操作数相同,则发生了溢出

采用双符号判断

- S1S2 = 00,结果为负,未溢出

- S1S2 = 01,结果为正,未溢出

- S1S2 = 10,上溢

- S1S2 = 11,下溢

定点乘法运算

机器数的移位操作

移位操作是乘法实现过程的基本操作,又分为逻辑移位和算术移位

逻辑移位:左移和右移,空出来的位置都补0

算术移位:左移时低位补0,右移时高位补符号位

原码一位乘法

原码一位乘法

符号位的确定

两个乘数符号位的异或

乘积的数值

- 由于符号位已经单独处理了,所以乘积就是绝对值相乘

- 用循环累加和移位操作实现乘法运算

- 两个n位数参加乘法运算,要做n次加法和移位操作

补码一位乘法

运算规则(booth算法)

- 被乘数一般取双符号位参与运算

- 乘数末位增设附加位Y(n+1),初值为0

- 利用Y(n+1) 与 Yn 的差,决定下一步的具体运算

- 按照上述算法进行n+1步累加操作,n步右移操作

| Y(n+1) - Yn | 操作 |

|---|---|

| 0 | 部分积右移一位 |

| 1 | 部分积加[x]补后,右移一位 |

| -1 | 部分积加[-x]补后,右移一位 |

阵列乘法器

一位乘法通过逐位判断、右移、循环累加来实现,速度较慢,为了提高乘法速度,可以采用硬件方式实现阵列乘法器,其基本思想是采用类似手工乘法运算的方法,用大量与门产生手工乘法中的各乘积项,同时将大量一位全加器按照手工乘法算式中需要进行加运算的各相关项的排列方式组成加法器阵列

定点除法运算

除法运算与乘法运算的处理思想相似,通常是将n位数的除操作转换成若干次的加减和移位来实现

原码一位除法

原码恢复余数法

被除数(余数)减去除数,如果为正则够减商1,如果为负则不够减商0,而且被除数(余数)要恢复到减之前的值,这就叫恢复余数法

为了防止溢出,除法运算(x / y)一定要满足(|x| < |y|),保证商的绝对值不超过1,因此第一次上商的值,要放在商的符号位,后面上的商,从小数点后依次排列,商的位数一般与除数相等,因此最后一次上商后,就不用做减法和移位了

原码不恢复余数法

与恢复余数法相比,进行比较后,如果商1则算法不变,如果商0则不恢复余数,先移位再加上除数

- 当余数为正时,商1,余数左移一位,减去除数

- 当余数为负时,商0,余数左移一位,加上除数

不恢复余数的补码一位除法

算法规则如下

- 被除数与除数同号,被除数减去除数;被除数与除数异号,被除数加上除数

- 余数与除数同号,商1,余数左移一位减去除数;余数与除数异号,商0,余数左移一位加上除数

一般情况下,对于商的精度没有特殊要求,商的末位“恒置1”

如果要求提高精度,则多求一位商,再用校正的办法对商进行处理

- 当刚好能除尽时,如果除数为正,则商不必修正;如果除数位负,则商需要校正

- 当不能除尽时,如果商为正,则不必修正;如果商为负,则商需要校正

求得n位商后,得到的余数往往是不正确的,正确的余数常需要根据具体情况做适当的处理

- 若商为正,当余数与被除数符号相同,则不需处理;当余数与被除数异号时,则应将余数加上除数进行修正才能获得正确的余数

- 若商为负,当余数与被除数同号时,则余数不需要处理;当余数与被除数异号时,则余数需要减去除数进行校正

余数之所以需要校正,是因为补码不恢复余数法除法运算过程中先比较上商的缘故

浮点运算

浮点数常用规格化数进行运算

浮点数加减运算

阶码和尾数采用补码表示的浮点数加减运算

- 对阶:对阶的原则是小的阶码向大的看齐,因为小阶码增大时,尾数部分右移而减小,损失的是最低位,对精度影响不大

- 尾数运算:对阶完成后,按照定点数的加减法运算执行尾数加减操作

- 结果规格化:为了处理方便,一般取两位符号位,当尾数符号位01或10时,需要向右规格化,将尾数右移一位,同时阶码加一;当尾数为11.1xxx或00.0xxx时,需要左移规格化,左移次数不固定,直到尾数部分出现11.0xx或00.1xx为止

- 舍入:在对阶右移和结果规格化右移时,会丢掉末尾的值,常用的舍入方法

- 末位恒置1法:只要右移时丢失过1,则末位置1

- 0舍1入法:当丢失位数最高位为1时,尾数末尾加1

- 溢出判断:只有阶码溢出时,才产生溢出,阶码符号位为01和10时溢出

IEEE 754浮点数的加减运算

IEEE 754浮点数的阶码采用移码表示,尾数采用原码表示,且尾数的最高位隐藏,因此算法与之前都采用补码的形式不同

- 对阶和规格化过程中,阶码的运算采用移码的加减运算

- 尾数的运算采用原码运算法则,且隐藏位要参与尾数运算

- 隐藏位参与尾数规格化判断及尾数规格化过程

- 溢出判断,上溢时阶码全1,下溢时阶码全0

浮点数乘法运算

- 阶码相加

- 尾数相乘

- 结果规格化

浮点数除法运算

- 尾数调整:检查被除数的尾数是否小于除数的尾数(考察绝对值),如果被除数的尾数大于除数尾数,则将被除数的尾数右移一位并调整阶码。由于操作数在运算前是规格化数,所以最多做一次调整,这步操作将防止商的尾数出现混乱,其实就是要求进行除法后,商是绝对值小于1的

- 阶码求差

- 尾数相除

逻辑运算

逻辑非:求反

逻辑乘:求与

逻辑加:求或

逻辑异:异或

运算器

运算器是对数据进行加工处理的部件,它具体实现数据的算术运算和逻辑运算,所以又称做算术逻辑运算部,记为ALU(Arithmetic logic unit),它是中央处理器CPU的重要组成部分

定点运算器

运算前的基本组成单元

算术逻辑运算单元

对数据进行加工处理的部件,主要完成算术运算和逻辑运算,也常作为数据传送的通路

通用寄存器组

运算器内通用寄存器组的作用大致可以分为3类:

- 用来暂存参与运算的数据和运算结果,尽量减少指令执行过程中访问主存的次数,提高运算速度

- 作为状态寄存器,保存运算过程中设置的状态,如进位、溢出、结果为负等,这些状态可以用于程序执行流程的控制

- 可作变址寄存器、堆栈指示器使用,不同的机器对这组寄存器的使用情况和设置个数不相同

输入输出数据选择控制

输入数据选择控制是对送入运算器的数据进行选择和控制,起作用包括:

- 选择数据送入运算器

- 控制数据以何种编码方式(原码、反码、补码等)送入运算器

输出数据控制电路是对运算器输出的数据进行控制,该电路一般还具有移位功能,并具有将运算器输出的数据输送到运算器、通用寄存器的通路和送往总线的控制电路

内部总线

是连接各个部件的信息通道

运算器的基本结构

运算器的基本结构与运算器中总线结构以及运算器各部件与总线的连接方式紧密相关,不同的连接构成不同的数据通路,形成不同结构的运算器

单总线

可以看出,所有部件与总线IB连接,因此需要在ALU输入端设置缓冲器LA和LB,单总线结构运算器的主要缺点是操作速度慢

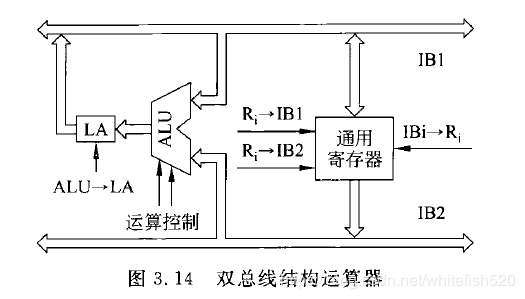

双总线

ALU与通用寄存器都连接在总线IB1和IB2上,因此可以同时通过两组总线传输数据

三总线

在执行双操作数运算时,可同时通过三组总线传输数据,不仅速度快,而且不需要设置缓冲器,图中的旁路器作用是不通过ALU实现通用寄存器之间的数据传输

浮点运算器

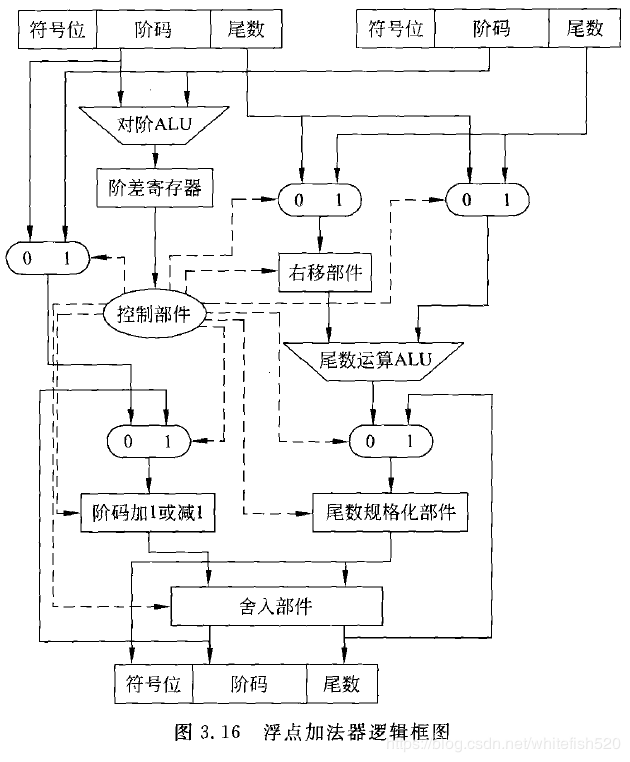

如图是浮点加法运算部件的逻辑结构图,最上面是两个浮点数据寄存器,左上部是一个用于对阶的ALU,它将两个浮点数的阶码相减,并将结果存入阶差寄存器中

浮点运算控制器部件根据阶差,选择阶码小的浮点数的位数进行右移操作,同时选择较大的阶码送入阶码加1或减1寄存器中

阶码大的浮点数的尾数和经过右移后的浮点数的尾数,进入尾数运算ALU进行尾数的加减运算,运算的结果送入尾数规格化部件,规格化时对运算结果的尾数进行左移或右移规格化,同时对阶码进行加一或减一操作,规格化的结果又送入舍入部件,控制部件根据规格化后的结果进行舍入操作

基本算术逻辑单元的设计

基本算术、逻辑部件

与门、或门、非门、二路选择器、一位全加器

基本算术逻辑运算单元设计

串行进位加法器

通过之前基本算术逻辑单元的设计,可以拿4个直接构成串行进位的加法器

此加法器的低位进位,直接送到高位,只有拿到低位的进位数据,高位才能进行运算,这种由低位向高位逐步产生进位的方式成为串行进位,也称为行波进位,串行加法器运算速度较慢

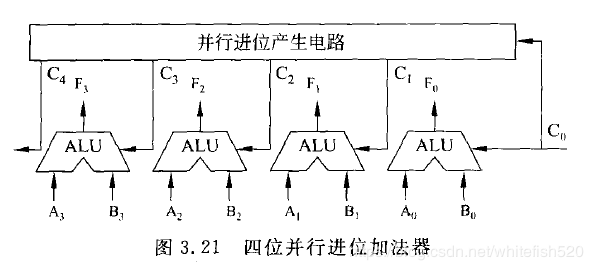

并行加法器

并行进位方式下,高位ALU的进位输入不再直接来自于低位ALU的进位输出,而是来自于并行进位产生电路的相应进位输出