触发器

转发:https://drivingc.com/p/5d6a5100a02ad965d3594912

R-S触发器

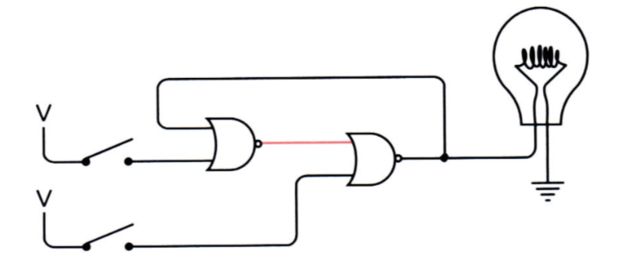

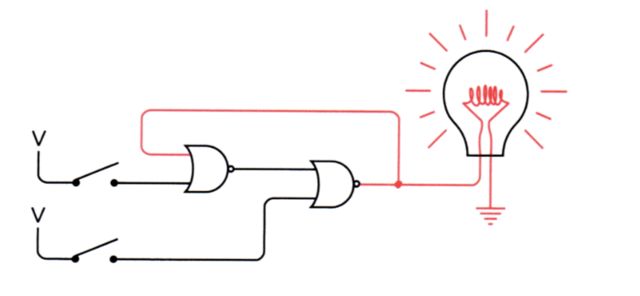

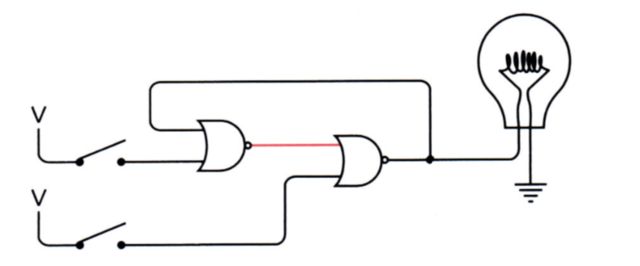

下图是含有两个或非门、两个开关和一个灯泡的电路:

![]() 正在上传…重新上传取消

正在上传…重新上传取消

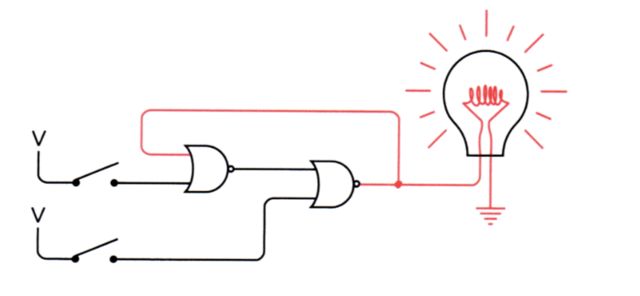

一开始,只有左边或非门的输出有电流,因为它的两个输入均为0。现在闭合上面的开关,左边或非门的输出变为0,于是右边或非门的输出变为1,灯泡点亮:

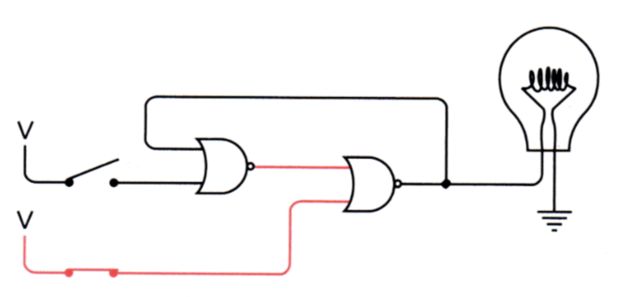

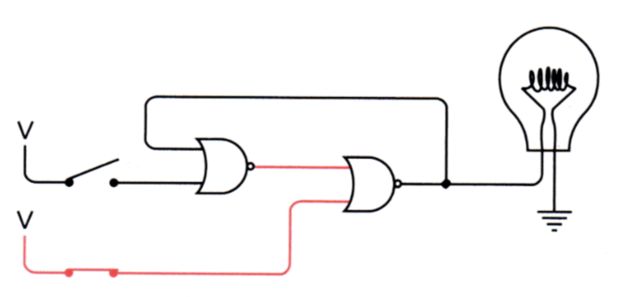

神奇之处在于当你断开上面的开关时,由于或非门的输入中只要有一个为1,其输出就是0,因而左边或非门的输出不变,灯泡仍然亮着:

![]() 正在上传…重新上传取消

正在上传…重新上传取消

![]() 正在上传…重新上传取消

正在上传…重新上传取消

![]() 正在上传…重新上传取消

正在上传…重新上传取消

你不觉得奇怪吗?两个开关都断开着,和第一幅图一样,但灯泡却亮着。这种情形和以前所见到的完全不同。通常,一个电路的输出仅仅依赖于输入,这里的情况却不一样。无论断开或闭合上面的开关,灯泡总是亮着。这里开关对电路没有什么影响,原因是左边或非门的输出一直是0。

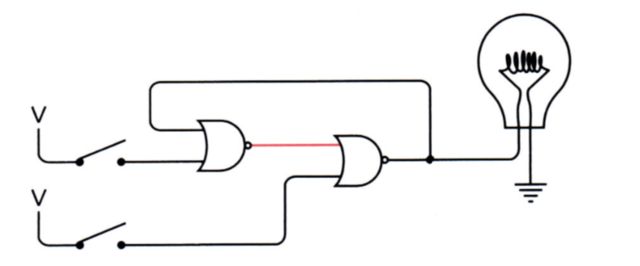

现在闭合下面的开关。由于右边或非门的输入中有一个是 1,则其输出变为0,灯泡熄灭。 左边或非门的输出此刻变为1:

![]() 转存失败重新上传取消

转存失败重新上传取消

![]() 正在上传…重新上传取消

正在上传…重新上传取消

![]() 转存失败重新上传取消

转存失败重新上传取消

现在,再断开下面的开关,灯泡仍旧不亮:

![]() 转存失败重新上传取消

转存失败重新上传取消

![]() 正在上传…重新上传取消

正在上传…重新上传取消

![]() 转存失败重新上传取消

转存失败重新上传取消

此电路和初始电路一样。然而这回却是下面开关的状态对灯泡没有什么影响。总结起来就是:

- 闭合上面的开关使灯泡点亮,当再断开时,灯泡仍然亮着。

- 闭合下面的开关使灯泡熄灭,当再断开时,灯泡仍然不亮。

电路的奇特之处是:有时当两个开关都断开时,灯泡亮着;而有时,当两个开关都断开时,灯泡却不亮。当两个开关都断开时,电路有两个稳定状态,这样的一个电路称为触发器。

触发器是1918年在英国射电物理学家William Henry Eccles(1875-1966)和F.W.Jordan的工作中发明的。触发器电路可以保持信息,换句话说,它有记忆性。它可以“记住”最近一次是哪个开 关先闭合的。如果你遇到这样一个触发器,它的灯泡亮着时,你可以确定最近闭合的是上面 的开关;而灯泡灭着时则是下面的开关。

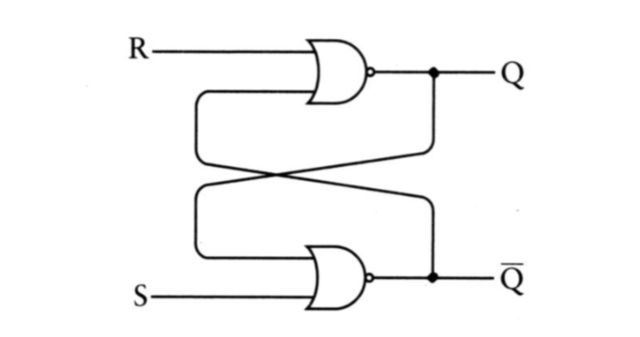

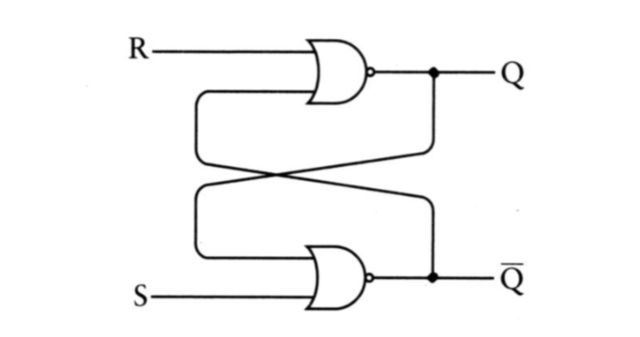

触发器有很多种,刚才所看到的是最简单的一种,称为R-S(或 Reset-Set,复位/置位)触发器。下面以对称的方式把它重新绘出来:

![]() 转存失败重新上传取消

转存失败重新上传取消

![]() 正在上传…重新上传取消

正在上传…重新上传取消

![]() 转存失败重新上传取消

转存失败重新上传取消

用于点亮灯泡的输出称为Q,另一个输出是Q的倒置。如果Q是0,就是1,反之亦然。 两个输入端S(Set)和R(Reset)分别表示置位和复位 。你可以把“置位”理解为把Q设为1,而“复位”是把 Q设为0。当S为1时(对应于前面图中闭合上面开关的情况),Q变为1而变为 0;当R为1时(对应于前面图中闭合下面开关的情况),Q变为0而变为1。当S和R都为0时, 输出保持Q原来的状态。

为什么要用触发器

触发器是十分关键的工具,尽管你现在可能还没看出来。它们赋予电路“记忆”,使其知道以前曾有过的状态。

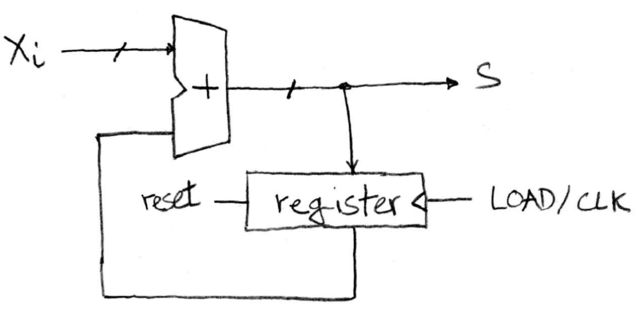

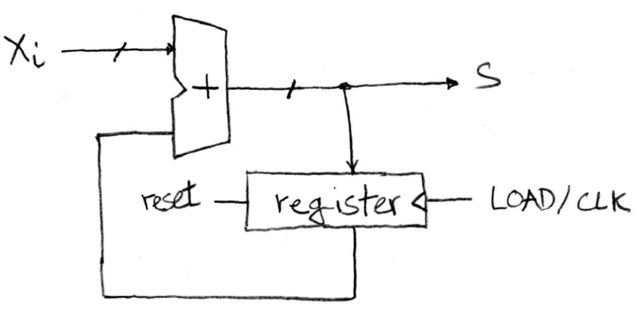

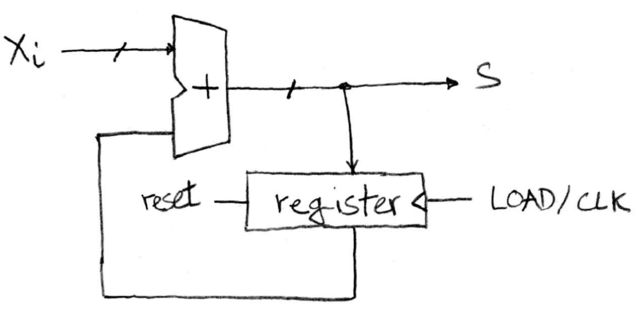

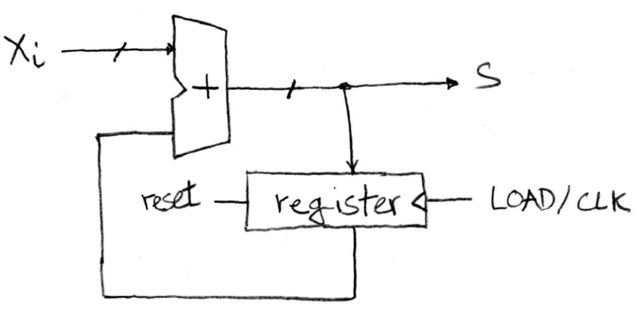

举个例子,我们要设计一个累加的电路,如果不用触发器,只用组合逻辑,设计为下图。但可以看到这个设计有问题,无法实现结果,因为无法存储中间值,无法控制状态转换。

![]() 转存失败重新上传取消

转存失败重新上传取消

![]() 正在上传…重新上传取消

正在上传…重新上传取消

![]() 转存失败重新上传取消

转存失败重新上传取消

所以就需要触发器存储中间值,结构如下:

![]() 转存失败重新上传取消

转存失败重新上传取消

![]() 正在上传…重新上传取消

正在上传…重新上传取消

![]() 转存失败重新上传取消

转存失败重新上传取消

计算机中的寄存器和高速缓冲就是使用触发器来保存0和1的。

电平触发的D触发器

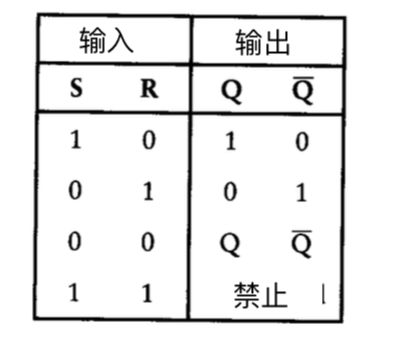

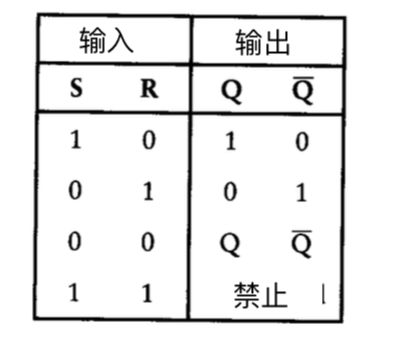

如果把R-S触发器的输入与输出绘制成表是这样的:

![]() 转存失败重新上传取消

转存失败重新上传取消

注意表中倒数第2行中S和R均为零,而输出标识为 Q和。这表示当S和R输入均为零时, Q和端的输出保持S、R同时设为0以前的输出值。表中最后一行说明 S和R输入都为1是非法的、禁止的。这是因为S、R同时为1时,两个输出Q和均为零,这与Q和互为倒置的关系相矛盾。所以,当你用R-S触发器设计电路时,要避免使R、S输入同时为1的情况。

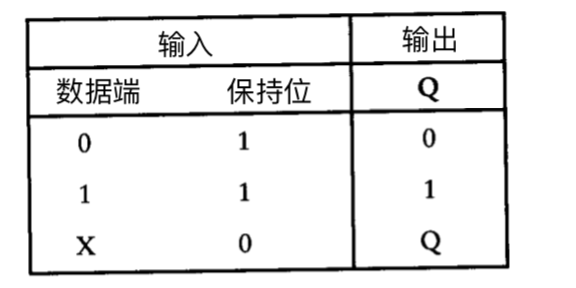

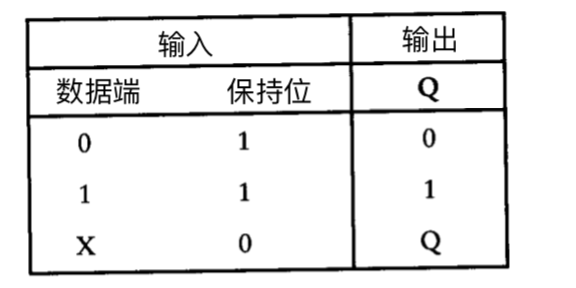

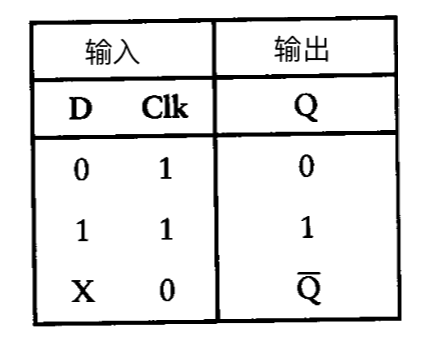

R-S触发器的这种输入输出形式不好控制,而且有非法状态,我们希望使用一个信号来给触发器提供数据,而用另外一根线控制触发器是否存储信息。换句话说,它的功能表可以这样写:

![]() 转存失败重新上传取消

转存失败重新上传取消

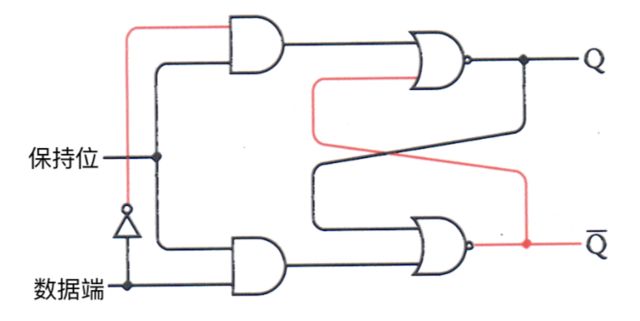

当保持位为1时,触发器会存储数据端的信息,而当保持位为0时,数据端对电路输出没有影响。这些功能可以在R-S触发器的基础上做稍微的修改就可以实现:

这个电路称为电平触发的D型触发器,D(Data)表示数据端输入。所谓电平触发是指当保持位输入为某一特定电平(本例中为“1”)时,触发器才对数据端的输入值进行保存。

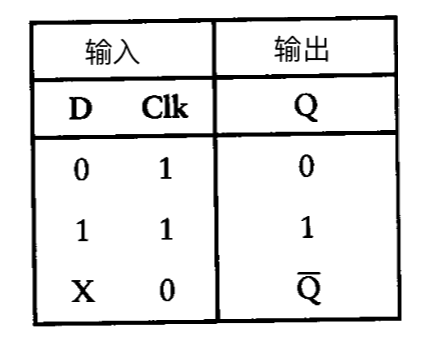

通常情况下,当这样一个电路出现在书中时,输入并不被标为保持位,而是标为“时钟”。 当然,这个信号并不是一个真的时钟,但它有时却具有类似钟一样的属性,即在0和1之是有 规律地来回变化。

把数据端简写为D,时钟端简写为Clk,其功能表如下所示:

![]() 转存失败重新上传取消

转存失败重新上传取消

这个电路就是所谓的电平触发的D型锁存器,它表示电路锁存住一位数据并保持至将来使用。它也可以称为1位存储器 。

边沿触发的D型触发器

对一些应用而言,电平触发时钟输入已经足够用了;但对另外一些应用来说, 边沿触发时钟输入更为适用。对于边沿触发器而言,只有当时钟从0变到1的瞬间,输出才会改变。在电平触发器中,当时钟输入为0时,数据端输入的任何改变都不会影响输出;而在边沿触发器中,当时钟输入为1时,数据端输入的改变也不会影响输出。只有在时钟输入从0变到1的瞬间, 数据端的输入才会影响边沿触发器的输出。

边沿触发的D型触发器是由两级R-S触发器按如下方式连接而成的:

![]() 转存失败重新上传取消

转存失败重新上传取消

![]() 转存失败重新上传取消

转存失败重新上传取消

![]() 转存失败重新上传取消

转存失败重新上传取消

将两个D触发器串联,其中使能端Clk用非门保证互斥,

于是第一个传输数据的时候,第二个D触发器保持;第二个传输数据的时候,第一个触发器保持。最后的结果就是,只在边沿触发的那一刻传输数据!

于是边沿性D触发器诞生了。我们可以在某一时刻同步触发所有读写动作,然后其他时候数据一致可靠保存记忆。

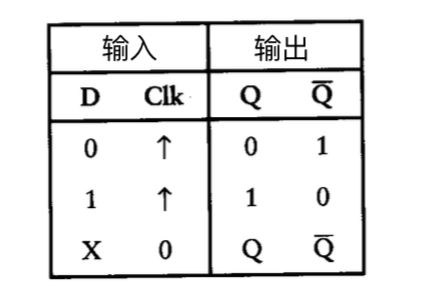

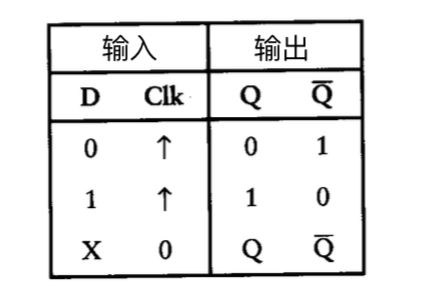

边沿触发的D型触发器的功能表需要一个新符号来表示这种从0到1的瞬时变化,即用一个向上指的箭头(↑)表示:

![]() 转存失败重新上传取消

转存失败重新上传取消

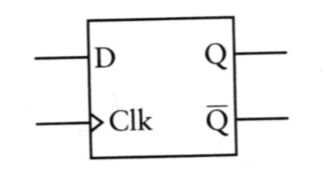

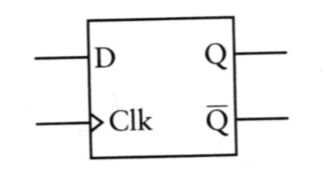

D型触发器在电路中可以由如下符号图表示:

![]() 转存失败重新上传取消

转存失败重新上传取消

分频器与计数器

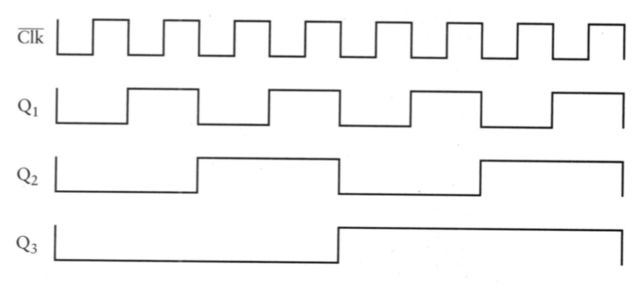

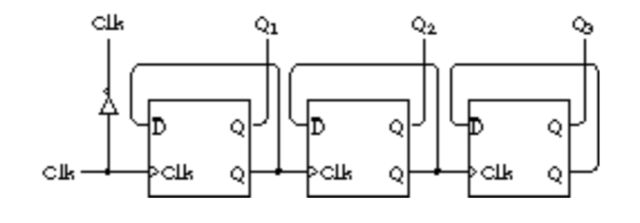

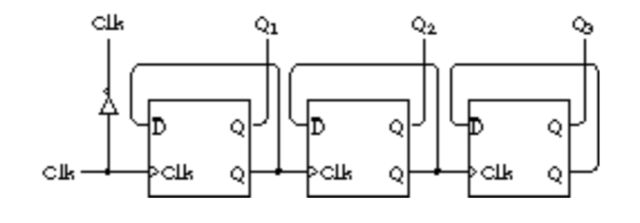

我们把几个D触发器连接起来看看会发生什么?

![]() 转存失败重新上传取消

转存失败重新上传取消

来看一下4个输出信号的变化规律:

频率刚好是倍数关系,其实这就是常用的分频电路。

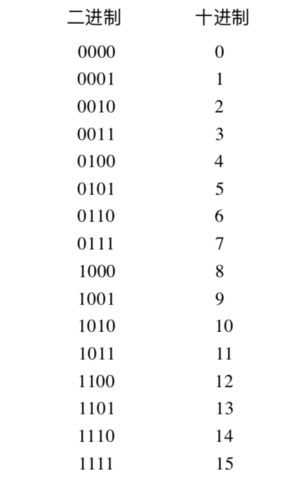

把这些信号标上0和1:

![]() 转存失败重新上传取消

转存失败重新上传取消

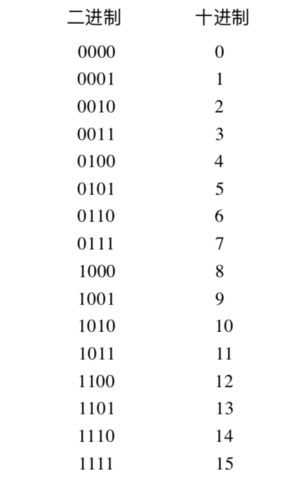

把这个图顺时针旋转90度,读一读横向的4位数字,每一组输出都对应了十进制中0~15中的一个数:

![]() 转存失败重新上传取消

转存失败重新上传取消

这就是计数电路,如果再多加上几个触发器,它就可能计更多的数。

最后推荐一个总结的很精辟的文章-计算机数学小书2-D触发器的进化之路,非常值得一读。

电路为什么要有触发器这种结构? - young cc的回答 - 知乎

https://www.zhihu.com/question/35128735/answer/61319380