一、什么是宏函数?通过宏定义的函数是宏函数。如下,编译器在预处理阶段会将Add(x,y)替换为((x)*(y))#defineAdd(x,y)((x)*(y))#defineAdd(x,y)((x)*(y))intmain(){inta=10;intb=20;intd=10;intc=Add(a+d,b)*2;cout<

C语言如何定义宏函数?

小九格物

c语言

在C语言中,宏函数是通过预处理器定义的,它在编译之前替换代码中的宏调用。宏函数可以模拟函数的行为,但它们不是真正的函数,因为它们在编译时不会进行类型检查,也不会分配存储空间。宏函数的定义通常使用#define指令,后面跟着宏的名称和参数列表,以及宏展开后的代码。宏函数的定义方式:1.基本宏函数:这是最简单的宏函数形式,它直接定义一个表达式。#defineSQUARE(x)((x)*(x))2.带参

微服务下功能权限与数据权限的设计与实现

nbsaas-boot

微服务java架构

在微服务架构下,系统的功能权限和数据权限控制显得尤为重要。随着系统规模的扩大和微服务数量的增加,如何保证不同用户和服务之间的访问权限准确、细粒度地控制,成为设计安全策略的关键。本文将讨论如何在微服务体系中设计和实现功能权限与数据权限控制。1.功能权限与数据权限的定义功能权限:指用户或系统角色对特定功能的访问权限。通常是某个用户角色能否执行某个操作,比如查看订单、创建订单、修改用户资料等。数据权限:

学点心理知识,呵护孩子健康

静候花开_7090

昨天听了华中师范大学教育管理学系副教授张玲老师的《哪里才是学生心理健康的最后庇护所,超越教育与技术的思考》的讲座。今天又重新学习了一遍,收获匪浅。张玲博士也注意到了当今社会上的孩子由于心理问题导致的自残、自杀及伤害他人等恶性事件。她向我们普及了一个重要的命题,她说心理健康的一些基本命题,我们与我们通常的一些教育命题是不同的,她还举了几个例子,让我们明白我们原来以为的健康并非心理学上的健康。比如如果

2021年12月19日,春蕾教育集团团建活动感受——黄晓丹

黄错错加油

感受:1.从陌生到熟悉的过程。游戏环节让我们在轻松的氛围中得到了锻炼,也增长了不少知识。2.游戏过程中,我们贡献的是个人力量,展现的是团队的力量。它磨合的往往不止是工作的熟悉,更是观念上契合度的贴近。3.这和工作是一样的道理。在各自的岗位上,每个人摆正自己的位置、各司其职充分发挥才能,并团结一致劲往一处使,才能实现最大的成功。新知:1.团队精神需要不断地创新。过去,人们把创新看作是冒风险,现在人们

《投行人生》读书笔记

小蘑菇的树洞

《投行人生》----作者詹姆斯-A-朗德摩根斯坦利副主席40年的职业洞见-很短小精悍的篇幅,比较适合初入职场的新人。第一部分成功的职业生涯需要规划1.情商归为适应能力分享与协作同理心适应能力,更多的是自我意识,你有能力识别自己的情并分辨这些情绪如何影响你的思想和行为。2.对于初入职场的人的建议,细节,截止日期和数据很重要截止日期,一种有效的方法是请老板为你所有的任务进行优先级排序。和老板喝咖啡的好

Long类型前后端数据不一致

igotyback

前端

响应给前端的数据浏览器控制台中response中看到的Long类型的数据是正常的到前端数据不一致前后端数据类型不匹配是一个常见问题,尤其是当后端使用Java的Long类型(64位)与前端JavaScript的Number类型(最大安全整数为2^53-1,即16位)进行数据交互时,很容易出现精度丢失的问题。这是因为JavaScript中的Number类型无法安全地表示超过16位的整数。为了解决这个问

如何在 Fork 的 GitHub 项目中保留自己的修改并同步上游更新?github_fork_update

iBaoxing

github

如何在Fork的GitHub项目中保留自己的修改并同步上游更新?在GitHub上Fork了一个项目后,你可能会对项目进行一些修改,同时原作者也在不断更新。如果想要在保留自己修改的基础上,同步原作者的最新更新,很多人会不知所措。本文将详细讲解如何在不丢失自己改动的情况下,将上游仓库的更新合并到自己的仓库中。问题描述假设你在GitHub上Fork了一个项目,并基于该项目做了一些修改,随后你发现原作者对

店群合一模式下的社区团购新发展——结合链动 2+1 模式、AI 智能名片与 S2B2C 商城小程序源码

说私域

人工智能小程序

摘要:本文探讨了店群合一的社区团购平台在当今商业环境中的重要性和优势。通过分析店群合一模式如何将互联网社群与线下终端紧密结合,阐述了链动2+1模式、AI智能名片和S2B2C商城小程序源码在这一模式中的应用价值。这些创新元素的结合为社区团购带来了新的机遇,提升了用户信任感、拓展了营销渠道,并实现了线上线下的完美融合。一、引言随着互联网技术的不断发展,社区团购作为一种新兴的商业模式,在满足消费者日常需

2021-08-26

影幽

在生活中,女人与男人的感悟往往有所不同。人生最大的舞台就是生活,大幕随时都可能拉开,关键是你愿不愿意表演都无法躲避。在生活中,遇事不要急躁,不要急于下结论,尤其生气时不要做决断,要学会换位思考,大事化小小事化了,把复杂的事情尽量简单处理,千万不要把简单的事情复杂化。永远不要扭曲,别人善意,无药可救。昨天是张过期的支票,明天是张信用卡,只有今天才是现金,要善加利用!执着的攀登者不必去与别人比较自己的

消息中间件有哪些常见类型

xmh-sxh-1314

java

消息中间件根据其设计理念和用途,可以大致分为以下几种常见类型:点对点消息队列(Point-to-PointMessagingQueues):在这种模型中,消息被发送到特定的队列中,消费者从队列中取出并处理消息。队列中的消息只能被一个消费者消费,消费后即被删除。常见的实现包括IBM的MQSeries、RabbitMQ的部分使用场景等。适用于任务分发、负载均衡等场景。发布/订阅消息模型(Pub/Sub

高级编程--XML+socket练习题

masa010

java开发语言

1.北京华北2114.8万人上海华东2,500万人广州华南1292.68万人成都华西1417万人(1)使用dom4j将信息存入xml中(2)读取信息,并打印控制台(3)添加一个city节点与子节点(4)使用socketTCP协议编写服务端与客户端,客户端输入城市ID,服务器响应相应城市信息(5)使用socketTCP协议编写服务端与客户端,客户端要求用户输入city对象,服务端接收并使用dom4j

2018-07-23-催眠日作业-#不一样的31天#-66小鹿

小鹿_33

预言日:人总是在逃避命运的路上,与之不期而遇。心理学上有个著名的名词,叫做自证预言;经济学上也有一个很著名的定律叫做,墨菲定律;在灵修派上,还有一个很著名的法则,叫做吸引力法则。这3个领域的词,虽然看起来不太一样,但是他们都在告诉人们一个现象:你越担心什么,就越有可能会发生什么。同样的道理,你越想得到什么,就应该要积极地去创造什么。无论是自证预言,墨菲定律还是吸引力法则,对人都有正反2个维度的影响

回溯 Leetcode 332 重新安排行程

mmaerd

Leetcode刷题学习记录leetcode算法职场和发展

重新安排行程Leetcode332学习记录自代码随想录给你一份航线列表tickets,其中tickets[i]=[fromi,toi]表示飞机出发和降落的机场地点。请你对该行程进行重新规划排序。所有这些机票都属于一个从JFK(肯尼迪国际机场)出发的先生,所以该行程必须从JFK开始。如果存在多种有效的行程,请你按字典排序返回最小的行程组合。例如,行程[“JFK”,“LGA”]与[“JFK”,“LGB

每日一题——第九十题

互联网打工人no1

C语言程序设计每日一练c语言

题目:判断子串是否与主串匹配#include#include#include//////判断子串是否在主串中匹配//////主串///子串///boolisSubstring(constchar*str,constchar*substr){intlenstr=strlen(str);//计算主串的长度intlenSub=strlen(substr);//计算子串的长度//遍历主字符串,对每个可能得

Python数据分析与可视化实战指南

William数据分析

pythonpython数据

在数据驱动的时代,Python因其简洁的语法、强大的库生态系统以及活跃的社区,成为了数据分析与可视化的首选语言。本文将通过一个详细的案例,带领大家学习如何使用Python进行数据分析,并通过可视化来直观呈现分析结果。一、环境准备1.1安装必要库在开始数据分析和可视化之前,我们需要安装一些常用的库。主要包括pandas、numpy、matplotlib和seaborn等。这些库分别用于数据处理、数学

《庄子.达生9》

钱江潮369

【原文】孔子观于吕梁,县水三十仞,流沫四十里,鼋鼍鱼鳖之所不能游也。见一丈夫游之,以为有苦而欲死也,使弟子并流而拯之。数百步而出,被发行歌而游于塘下。孔子从而问焉,曰:“吾以子为鬼,察子则人也。请问,‘蹈水有道乎’”曰:“亡,吾无道。吾始乎故,长乎性,成乎命。与齐俱入,与汩偕出,从水之道而不为私焉。此吾所以蹈之也。”孔子曰:“何谓始乎故,长乎性,成乎命?”曰:“吾生于陵而安于陵,故也;长于水而安于

Python中os.environ基本介绍及使用方法

鹤冲天Pro

#Pythonpython服务器开发语言

文章目录python中os.environos.environ简介os.environ进行环境变量的增删改查python中os.environ的使用详解1.简介2.key字段详解2.1常见key字段3.os.environ.get()用法4.环境变量的增删改查和判断是否存在4.1新增环境变量4.2更新环境变量4.3获取环境变量4.4删除环境变量4.5判断环境变量是否存在python中os.envi

水泥质量纠纷案代理词

徐宝峰律师

贵州领航建设有限公司诉贵州纳雍隆庆乌江水泥有限公司产品质量纠纷案代理词尊敬的审判长、审判员:贵州千里律师事务所接受被告贵州纳雍隆庆乌江水泥有限公司的委托,指派我担任其诉讼代理人,参加本案的诉讼活动。下面,我结合本案事实和相关法律规定发表如下代理意见,供合议庭评议案件时参考:原告应当举证证明其遭受的损失与被告生产的水泥质量的因果关系。首先水泥是一种粉状水硬性无机胶凝材料。加水搅拌后成浆体,能在空气中

腾讯云技术深度探索:构建高效云原生微服务架构

我的运维人生

云原生架构腾讯云运维开发技术共享

腾讯云技术深度探索:构建高效云原生微服务架构在当今快速发展的技术环境中,云原生技术已成为企业数字化转型的关键驱动力。腾讯云作为行业领先的云服务提供商,不断推出创新的产品和技术,助力企业构建高效、可扩展的云原生微服务架构。本文将深入探讨腾讯云在微服务领域的最新进展,并通过一个实际案例展示如何在腾讯云平台上构建云原生应用。腾讯云微服务架构概览腾讯云微服务架构基于云原生理念,旨在帮助企业快速实现应用的容

Pyecharts数据可视化大屏:打造沉浸式数据分析体验

我的运维人生

信息可视化数据分析数据挖掘运维开发技术共享

Pyecharts数据可视化大屏:打造沉浸式数据分析体验在当今这个数据驱动的时代,如何将海量数据以直观、生动的方式展现出来,成为了数据分析师和企业决策者关注的焦点。Pyecharts,作为一款基于Python的开源数据可视化库,凭借其丰富的图表类型、灵活的配置选项以及高度的定制化能力,成为了构建数据可视化大屏的理想选择。本文将深入探讨如何利用Pyecharts打造数据可视化大屏,并通过实际代码案例

ztree设置禁用节点

3213213333332132

JavaScriptztreejsonsetDisabledNodeAjax

ztree设置禁用节点的时候注意,当使用ajax后台请求数据,必须要设置为同步获取数据,否者会获取不到节点对象,导致设置禁用没有效果。

$(function(){

showTree();

setDisabledNode();

});

JVM patch by Taobao

bookjovi

javaHotSpot

在网上无意中看到淘宝提交的hotspot patch,共四个,有意思,记录一下。

7050685:jsdbproc64.sh has a typo in the package name

7058036:FieldsAllocationStyle=2 does not work in 32-bit VM

7060619:C1 should respect inline and

将session存储到数据库中

dcj3sjt126com

sqlPHPsession

CREATE TABLE sessions (

id CHAR(32) NOT NULL,

data TEXT,

last_accessed TIMESTAMP NOT NULL,

PRIMARY KEY (id)

);

<?php

/**

* Created by PhpStorm.

* User: michaeldu

* Date

Vector

171815164

vector

public Vector<CartProduct> delCart(Vector<CartProduct> cart, String id) {

for (int i = 0; i < cart.size(); i++) {

if (cart.get(i).getId().equals(id)) {

cart.remove(i);

各连接池配置参数比较

g21121

连接池

排版真心费劲,大家凑合看下吧,见谅~

Druid

DBCP

C3P0

Proxool

数据库用户名称 Username Username User

数据库密码 Password Password Password

驱动名

[简单]mybatis insert语句添加动态字段

53873039oycg

mybatis

mysql数据库,id自增,配置如下:

<insert id="saveTestTb" useGeneratedKeys="true" keyProperty="id"

parameterType=&

struts2拦截器配置

云端月影

struts2拦截器

struts2拦截器interceptor的三种配置方法

方法1. 普通配置法

<struts>

<package name="struts2" extends="struts-default">

&

IE中页面不居中,火狐谷歌等正常

aijuans

IE中页面不居中

问题是首页在火狐、谷歌、所有IE中正常显示,列表页的页面在火狐谷歌中正常,在IE6、7、8中都不中,觉得可能那个地方设置的让IE系列都不认识,仔细查看后发现,列表页中没写HTML模板部分没有添加DTD定义,就是<!DOCTYPE html PUBLIC "-//W3C//DTD XHTML 1.0 Transitional//EN" "http://www.w3

String,int,Integer,char 几个类型常见转换

antonyup_2006

htmlsql.net

如何将字串 String 转换成整数 int?

int i = Integer.valueOf(my_str).intValue();

int i=Integer.parseInt(str);

如何将字串 String 转换成Integer ?

Integer integer=Integer.valueOf(str);

如何将整数 int 转换成字串 String ?

1.

PL/SQL的游标类型

百合不是茶

显示游标(静态游标)隐式游标游标的更新和删除%rowtyperef游标(动态游标)

游标是oracle中的一个结果集,用于存放查询的结果;

PL/SQL中游标的声明;

1,声明游标

2,打开游标(默认是关闭的);

3,提取数据

4,关闭游标

注意的要点:游标必须声明在declare中,使用open打开游标,fetch取游标中的数据,close关闭游标

隐式游标:主要是对DML数据的操作隐

JUnit4中@AfterClass @BeforeClass @after @before的区别对比

bijian1013

JUnit4单元测试

一.基础知识

JUnit4使用Java5中的注解(annotation),以下是JUnit4常用的几个annotation: @Before:初始化方法 对于每一个测试方法都要执行一次(注意与BeforeClass区别,后者是对于所有方法执行一次)@After:释放资源 对于每一个测试方法都要执行一次(注意与AfterClass区别,后者是对于所有方法执行一次

精通Oracle10编程SQL(12)开发包

bijian1013

oracle数据库plsql

/*

*开发包

*包用于逻辑组合相关的PL/SQL类型(例如TABLE类型和RECORD类型)、PL/SQL项(例如游标和游标变量)和PL/SQL子程序(例如过程和函数)

*/

--包用于逻辑组合相关的PL/SQL类型、项和子程序,它由包规范和包体两部分组成

--建立包规范:包规范实际是包与应用程序之间的接口,它用于定义包的公用组件,包括常量、变量、游标、过程和函数等

--在包规

【EhCache二】ehcache.xml配置详解

bit1129

ehcache.xml

在ehcache官网上找了多次,终于找到ehcache.xml配置元素和属性的含义说明文档了,这个文档包含在ehcache.xml的注释中!

ehcache.xml : http://ehcache.org/ehcache.xml

ehcache.xsd : http://ehcache.org/ehcache.xsd

ehcache配置文件的根元素是ehcahe

ehcac

java.lang.ClassNotFoundException: org.springframework.web.context.ContextLoaderL

白糖_

javaeclipsespringtomcatWeb

今天学习spring+cxf的时候遇到一个问题:在web.xml中配置了spring的上下文监听器:

<listener>

<listener-class>org.springframework.web.context.ContextLoaderListener</listener-class>

</listener>

随后启动

angular.element

boyitech

AngularJSAngularJS APIangular.element

angular.element

描述: 包裹着一部分DOM element或者是HTML字符串,把它作为一个jQuery元素来处理。(类似于jQuery的选择器啦) 如果jQuery被引入了,则angular.element就可以看作是jQuery选择器,选择的对象可以使用jQuery的函数;如果jQuery不可用,angular.e

java-给定两个已排序序列,找出共同的元素。

bylijinnan

java

import java.util.ArrayList;

import java.util.Arrays;

import java.util.List;

public class CommonItemInTwoSortedArray {

/**

* 题目:给定两个已排序序列,找出共同的元素。

* 1.定义两个指针分别指向序列的开始。

* 如果指向的两个元素

sftp 异常,有遇到的吗?求解

Chen.H

javajcraftauthjschjschexception

com.jcraft.jsch.JSchException: Auth cancel

at com.jcraft.jsch.Session.connect(Session.java:460)

at com.jcraft.jsch.Session.connect(Session.java:154)

at cn.vivame.util.ftp.SftpServerAccess.connec

[生物智能与人工智能]神经元中的电化学结构代表什么?

comsci

人工智能

我这里做一个大胆的猜想,生物神经网络中的神经元中包含着一些化学和类似电路的结构,这些结构通常用来扮演类似我们在拓扑分析系统中的节点嵌入方程一样,使得我们的神经网络产生智能判断的能力,而这些嵌入到节点中的方程同时也扮演着"经验"的角色....

我们可以尝试一下...在某些神经

通过LAC和CID获取经纬度信息

dai_lm

laccid

方法1:

用浏览器打开http://www.minigps.net/cellsearch.html,然后输入lac和cid信息(mcc和mnc可以填0),如果数据正确就可以获得相应的经纬度

方法2:

发送HTTP请求到http://www.open-electronics.org/celltrack/cell.php?hex=0&lac=<lac>&cid=&

JAVA的困难分析

datamachine

java

前段时间转了一篇SQL的文章(http://datamachine.iteye.com/blog/1971896),文章不复杂,但思想深刻,就顺便思考了一下java的不足,当砖头丢出来,希望引点和田玉。

-----------------------------------------------------------------------------------------

小学5年级英语单词背诵第二课

dcj3sjt126com

englishword

money 钱

paper 纸

speak 讲,说

tell 告诉

remember 记得,想起

knock 敲,击,打

question 问题

number 数字,号码

learn 学会,学习

street 街道

carry 搬运,携带

send 发送,邮寄,发射

must 必须

light 灯,光线,轻的

front

linux下面没有tree命令

dcj3sjt126com

linux

centos p安装

yum -y install tree

mac os安装

brew install tree

首先来看tree的用法

tree 中文解释:tree

功能说明:以树状图列出目录的内容。

语 法:tree [-aACdDfFgilnNpqstux][-I <范本样式>][-P <范本样式

Map迭代方式,Map迭代,Map循环

蕃薯耀

Map循环Map迭代Map迭代方式

Map迭代方式,Map迭代,Map循环

>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>

蕃薯耀 2015年

Spring Cache注解+Redis

hanqunfeng

spring

Spring3.1 Cache注解

依赖jar包:

<!-- redis -->

<dependency>

<groupId>org.springframework.data</groupId>

<artifactId>spring-data-redis</artifactId>

Guava中针对集合的 filter和过滤功能

jackyrong

filter

在guava库中,自带了过滤器(filter)的功能,可以用来对collection 进行过滤,先看例子:

@Test

public void whenFilterWithIterables_thenFiltered() {

List<String> names = Lists.newArrayList("John"

学习编程那点事

lampcy

编程androidPHPhtml5

一年前的夏天,我还在纠结要不要改行,要不要去学php?能学到真本事吗?改行能成功吗?太多的问题,我终于不顾一切,下定决心,辞去了工作,来到传说中的帝都。老师给的乘车方式还算有效,很顺利的就到了学校,赶巧了,正好学校搬到了新校区。先安顿了下来,过了个轻松的周末,第一次到帝都,逛逛吧!

接下来的周一,是我噩梦的开始,学习内容对我这个零基础的人来说,除了勉强完成老师布置的作业外,我已经没有时间和精力去

架构师之流处理---------bytebuffer的mark,limit和flip

nannan408

ByteBuffer

1.前言。

如题,limit其实就是可以读取的字节长度的意思,flip是清空的意思,mark是标记的意思 。

2.例子.

例子代码:

String str = "helloWorld";

ByteBuffer buff = ByteBuffer.wrap(str.getBytes());

Sy

org.apache.el.parser.ParseException: Encountered " ":" ": "" at line 1, column 1

Everyday都不同

$转义el表达式

最近在做Highcharts的过程中,在写js时,出现了以下异常:

严重: Servlet.service() for servlet jsp threw exception

org.apache.el.parser.ParseException: Encountered " ":" ": "" at line 1,

用Java实现发送邮件到163

tntxia

java实现

/*

在java版经常看到有人问如何用javamail发送邮件?如何接收邮件?如何访问多个文件夹等。问题零散,而历史的回复早已经淹没在问题的海洋之中。

本人之前所做过一个java项目,其中包含有WebMail功能,当初为用java实现而对javamail摸索了一段时间,总算有点收获。看到论坛中的经常有此方面的问题,因此把我的一些经验帖出来,希望对大家有些帮助。

此篇仅介绍用

探索实体类存在的真正意义

java小叶檀

POJO

一. 实体类简述

实体类其实就是俗称的POJO,这种类一般不实现特殊框架下的接口,在程序中仅作为数据容器用来持久化存储数据用的

POJO(Plain Old Java Objects)简单的Java对象

它的一般格式就是

public class A{

private String id;

public Str

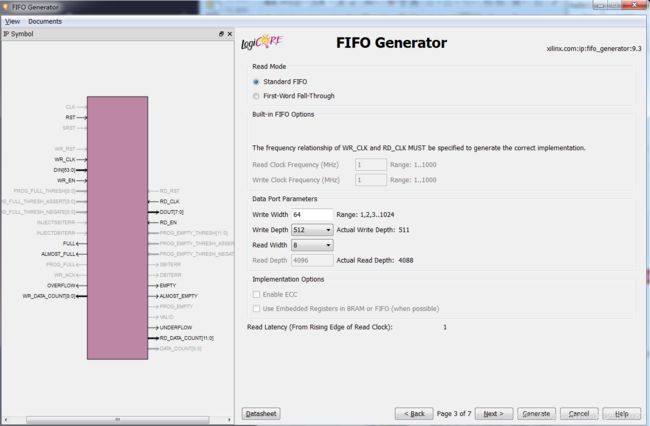

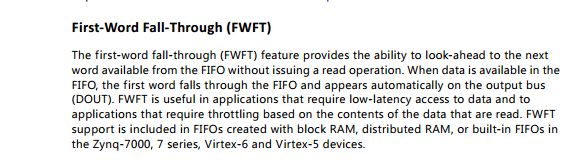

模式的话我比较喜欢使用标准FIFO,明德扬老师喜欢用First-word fall through,这个区别是 FWFT模式是数据先出现在输出总线上,再使能读信号,为了低延迟,只有7系列和 virtex 5系列支持 ,我目前使用的spartan6系列并不支持,英文翻译再下面:

模式的话我比较喜欢使用标准FIFO,明德扬老师喜欢用First-word fall through,这个区别是 FWFT模式是数据先出现在输出总线上,再使能读信号,为了低延迟,只有7系列和 virtex 5系列支持 ,我目前使用的spartan6系列并不支持,英文翻译再下面: 接下来是位宽的设置,因为我的输入为32位的IQ两路信号,因此我的输入位宽为64,输出位宽由UPP输出数据位宽决定,8位传输。最大512的存储空间,本来想设置为读写分时,后面决定阉割版的读写分时没什么意思,此处的空间其实可以将512改成2,但是我懒得改了~

接下来是位宽的设置,因为我的输入为32位的IQ两路信号,因此我的输入位宽为64,输出位宽由UPP输出数据位宽决定,8位传输。最大512的存储空间,本来想设置为读写分时,后面决定阉割版的读写分时没什么意思,此处的空间其实可以将512改成2,但是我懒得改了~ 接下来就是一些控制信号,为了方便大家随便加上。我的读数据速度为

接下来就是一些控制信号,为了方便大家随便加上。我的读数据速度为 同步复位,注意这里的复位,是导致我上次失败的原因,查阅手册也可以看到,复位仅仅是复位FIFO内部的读写地址,并不会清空内部数据。

同步复位,注意这里的复位,是导致我上次失败的原因,查阅手册也可以看到,复位仅仅是复位FIFO内部的读写地址,并不会清空内部数据。 另外两个概念,可编程的满标志上下限和满标志的空上下限一会介绍~

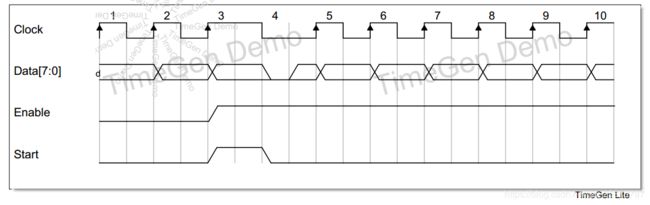

另外两个概念,可编程的满标志上下限和满标志的空上下限一会介绍~ UPP通用并口大概就是这样,Start代表第一个数据,enable使能开始数据传输

UPP通用并口大概就是这样,Start代表第一个数据,enable使能开始数据传输![]() rdy_nege为写时钟,可以看到,rst复位以后,经过三个时钟周期后数据才能写入到FIFO中,但不知道为什么写计数不会增加,当我把读域的代码注释掉以后又会增加,这是目前的问题。

rdy_nege为写时钟,可以看到,rst复位以后,经过三个时钟周期后数据才能写入到FIFO中,但不知道为什么写计数不会增加,当我把读域的代码注释掉以后又会增加,这是目前的问题。![]() 读时钟域比较复杂,因为我设置的

读时钟域比较复杂,因为我设置的 保证数据的中心时钟进行变化,同时start信号只计数一个时钟周期,DSP端成功接收数据~

保证数据的中心时钟进行变化,同时start信号只计数一个时钟周期,DSP端成功接收数据~