- GFPGAN - 腾讯开源的图形修复算法修复算法

小众AI

AI开源开源算法人工智能

GFPGAN是腾讯开源的人脸修复算法,它利用预先训练好的面部修复算法,并且封装了各种丰富多样的先验因素进行盲脸(blindface)修复,可以对老照片进行很好的修复。35800Stars5900Forks345Issues11贡献者ApacheLicensePython语言代码:https://github.com/TencentARC/GFPGAN更多AI开源软件:AI开源-小众AI主要功能盲修

- FPGA在空间领域应用的权衡之道

forgeda

EDA硬件辅助验证fpga开发硬件架构嵌入式硬件EDA硬件辅助验证故障注入测试SEUEmulation商业航天

新官上任,干货较多。去年10月30日,紫光国微在投资者关系活动中表示,对FPGA产品的国产化率以及未来价格压力趋势的答复是,除了个别品类外,FPGA领域已基本完成国产化替代。价格竞争激烈,现有存量市场需求不足,导致产品价格成为重要竞争手段等。价格是市场新进入者的唯一机会,FPGA行业自然也不例外。当下火热的“智算概念”,如果说GPU在数据中心堆算力的方式有多风光,那么在追求性能之外,必须权衡SWa

- QUARTUS使用之2: signaltap笔记

weixin_39274156

signaltapFPGAalteraquatusiisignaltap

signaltap笔记时间:2019年10月23日地点:苏州前言之前一直使用chipscope有四年时间,习惯了ISE的CDC使用,我个人的习惯是当FPGA编译时间小于十五分钟时,更愿意使用在线逻辑分析仪,这样的结果更真实,当然Modelsim仿真是很重要的。但是最近工作需要使用ALTERA的FPGA芯片,这就需要我学会使用quartus,我个人认为signaltap在线逻辑分析仪是必须要掌握的软

- Verilog呼吸灯项目实战指南

酸甜草莓二侠

本文还有配套的精品资源,点击获取简介:本项目“breathLED.zip”详细介绍了利用Verilog硬件描述语言实现呼吸灯效果的完整流程。从Verilog基础到C语言仿真,再到实际的Verilog仿真、工程建立和硬件烧录,详细讲述了在FPGA设计中的每个关键步骤。涵盖了时钟信号定义、计数器和比较器的设计、Testbench编写、编译综合、布局布线以及最终的硬件烧录与调试。本项目不仅提供了实践指南

- 基于FPGA的DDS设计

Squirrels43

verilogfpga

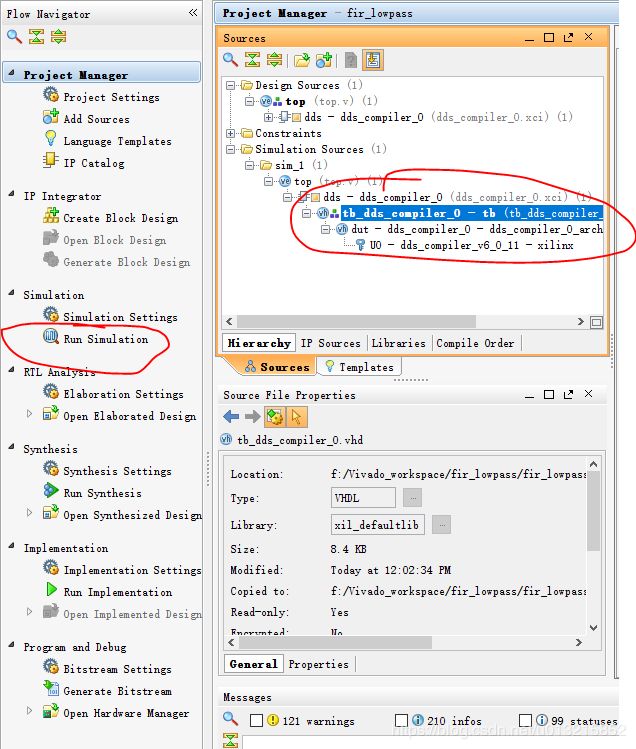

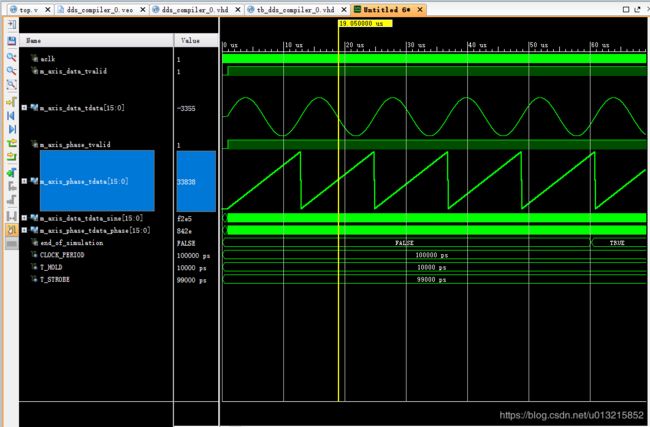

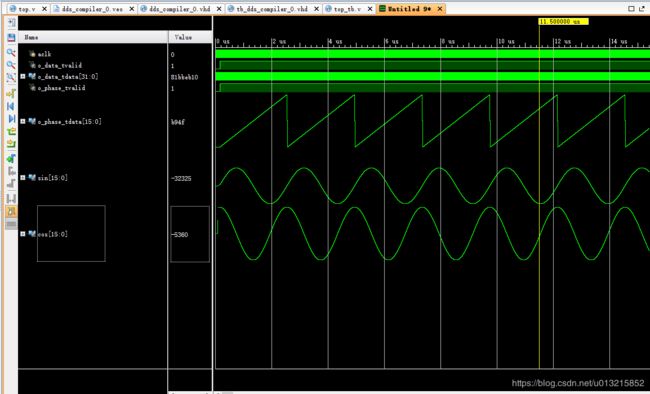

文章目录目标一、DDS电路核心RTL1.设计一个DDS的核心RTL代码。2.使用Matlab生成DDS的波表ROM3.验证目标二、DDS开发板测试平台1.使用Quartus的SignalTAP观察DDS的输出波形2.导出SignalTAP的捕获数据至电脑(生成List文件)3.用UltraEdit的列操作模式编辑数据格式。(matlab变量定义)4.使用Matlab分析DDS生成的正弦信号的频谱纯

- [读书日志]8051软核处理器设计实战(基于FPGA)第六篇:8051软核处理器指令支持添加(verilog)

JoneMaster

JM读书日志系列fpga开发

5.4为主体程序添加指令接下来我们来为主体程序添加指令。在开始之前,我们有必要先把目前的代码展示出来://`defineTYPE8052moduler8051(inputwireclk,inputwirerst,inputwirecpu_en,inputwirecpu_restart,outputregrom_en,outputreg[15:0]rom_addr,inputwire[7:0]rom

- 国内优秀的FPGA设计公司主要分布在哪些城市?

博览鸿蒙

FPGAfpga开发

近年来,国内FPGA行业发展迅速,随着5G通信、人工智能、大数据等新兴技术的崛起,FPGA设计企业的需求也迎来了爆发式增长。很多技术人才在求职时都会考虑城市的行业分布和发展潜力。因此,国内优秀的FPGA设计公司主要分布在哪些城市?以下将对国内FPGA企业集中的城市进行梳理。北京北京在我国FPGA产业发展中有着重要地位,尤其在设计和应用领域有较大优势,形成了完整的研发和产业生态。目前,北京主要的产业

- 基于FPGA的简易RLC测量仪设计与实现

耄先森吖

本文还有配套的精品资源,点击获取简介:RLC测量仪用于检测电路中电阻、电感和电容参数,对于电子工程和电路设计至关重要。本文将详细探讨简易RLC测量仪的设计与实现,特别关注其自动换档测量技术和采用的FPGA技术。FPGA提供并行处理能力和高速运算,能够快速响应测量信号并调整测量范围。本文还提供了测量仪的硬件逻辑设计、测量算法和软件实现,以及技术文档说明,对于理解RLC测量仪的实现细节和使用方法具有重

- FPGA USB2.0串口通信项目设计与实现

瞬泉

本文还有配套的精品资源,点击获取简介:本项目主要围绕FPGA(Field-ProgrammableGateArray)和Verilog语言,实现USB(通用串行总线)2.0标准的串口通信功能。项目涵盖了从时钟配置到物理层接口的全套设计过程,包括UART通信的帧同步、波特率生成、握手协议等。项目文档和代码可能包含Verilog代码文件、测试平台配置、波形记录文件、编译脚本和用户手册,以助于开发者理解

- FPGA开发中的团队协作:构建高效协同的关键路径

whik1194

fpga开发

一、团队成员角色与职责FPGA工程师核心设计:负责FPGA的逻辑设计与代码实现,依据项目需求,运用硬件描述语言(如Verilog或VHDL)完成模块功能编写。例如在设计一个高速数据采集系统时,编写数据采集、缓存及预处理的逻辑代码。功能仿真与验证:使用仿真工具对所编写的代码进行功能验证,确保逻辑设计符合预期。像在完成数字滤波器模块代码后,通过仿真测试不同输入信号下的输出,检查滤波效果。时序分析与优化

- 设计Xnorgate FPGA同或门

CodeWG

fpga开发matlab

设计XnorgateFPGA同或门同或门是一种基本的逻辑门电路,它的输出与输入相反当且仅当所有输入都相同。在这篇文章中,我们将会介绍如何使用FPGA实现Xnorgate同或门电路。首先,我们需要了解FPGA(FieldProgrammableGateArray)是一种可编程的数字逻辑芯片,它可以通过编程来实现各种数字逻辑电路。在本文中,我们将使用Altera公司的QuartusII软件来进行FPG

- FPGA工程师有哪些?(设计、验证与应用)

博览鸿蒙

FPGAfpga开发

随着FPGA技术的发展和应用领域的拓展,FPGA工程师的岗位也越来越细分。FPGA产业链涉及多个环节,每个环节都需要不同类型的工程师协同工作。本文将梳理FPGA领域的主要工程师类型,帮助读者更好地了解该行业。FPGA设计环节系统架构师(SystemArchitect):这是FPGA领域的资深职位,需要对系统架构、FPGA技术、应用场景等有深入的理解。架构师负责定义系统级规范、制定FPGA架构方案、

- FPGA在高速数据采集系统中的应用!!!

FPGA资料库

fpga开发fpgaverilog物联网stm32

FPGA(现场可编程门阵列)在高速数据采集系统中的应用非常广泛,主要得益于其并行处理能力、可编程性和高速接口特性。以下是FPGA在高速数据采集系统中的详细应用,以及一些具体例子:1.应用背景高速数据采集系统通常用于需要高采样率和大数据量处理的场合,如雷达信号处理、医疗成像、高速通信等。FPGA因其独特的硬件架构,能够有效处理高速数据流,因此在这些系统中扮演着关键角色。2.应用内容2.1数据采集接口

- 基于DSP+FPGA高速运动控制器设计

深圳信迈科技DSP+ARM+FPGA

运动控制器国产ARM+FPGAfpga开发运动控制器

基于“PC+运动控制器”结构的开放式机器人运动控制系统能够充分利用PC开放程度高、通用性好、处理能力强等特点以及运动控制器运算速度快、实时性能好、控制能力强等特点,因此得到较快发展,成为目前的研究热点。但目前采用此种结构的开放式机器人运动控制系统中,不管是控制器供应商所提供的运动控制器或者是科研人员自主设计的运动控制器,在通用性、软硬件可重构方面都存在一些问题,影响着机器人运动控制系统的开放性。因

- FPGA与ASIC:深度解析与职业选择

博览鸿蒙

FPGAfpga开发制造

IC(集成电路)行业涵盖广泛,涉及数字、模拟等不同研究方向,以及设计、制造、封测等不同产业环节。其中,FPGA(现场可编程门阵列)和ASIC(专用集成电路)是两种重要的芯片类型,经常让初入行者或转行者面临选择难题。本文将深入剖析FPGA与ASIC的区别,帮助读者更好地理解并做出职业规划。概念辨析FPGA(FieldProgrammableGateArray):本质上是一种芯片,允许用户通过编程配置

- Xilinx FPGA全局时钟和第二全局时钟资源的使用方法

yundanfengqing_nuc

FPGA

“全局时钟和第二全局时钟资源”是FPGA同步设计的一个重要概念。合理利用该资源可以改善设计的综合和实现效果;如果使用不当,不但会影响设计的工作频率和稳定性等,甚至会导致设计的综合、实现过程出错。本文总结了XilinxFPGA全局时钟和第二全局时钟资源的使用方法,并强调了应用中的注意事项。目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更

- FPGA-全局时钟缓冲IBUFG BUFG IBUFGDS ODDR2

kelinnn

FPGAfpga嵌入式buffer

学习内容全局时钟缓冲,输入缓冲,输出缓冲开发环境xilinxspartan6、ISE14.7、modelsim10.5写在前面的话当你用ISE14.7时可能会出现如下的报错Thisdesigncontainsaglobalbufferinstance,,drivingthenet,,thatisdrivingthefollowing(first30)non-clockloadpins.Thisde

- ZYNQ&FPGA 时钟IP核(MMCM PLL)实验

Nadukab

fpgaverilog嵌入式

时钟资源简介:7系列的FPGA使用了专用的全局(Global)和区域(Regional)时钟资源来管理和设计不同的时钟需求。ClockManagementTiles(CMT)提供了时钟合成(Clockfrequencysynthesis),倾斜矫正(deskew),过滤抖动(jitterfiltering)功能。一个CMT包括一个MMCM和一个PLL。7系列FPGA高层次时钟结构视图:ClockR

- FPGA 时钟树缓存布局布线

cckkppll

fpga开发

时钟树缓存布局布线在以下阶段,Vivado布局器确定MMCM/PLL,全局时钟缓存和时钟根的位置,同时遵守物理XDC约束:1.I/O和时钟布局布局器根据连接规则和用户约束布局I/O缓存和MMCM/PLL。布局器将时钟缓存分配给时钟区域,但不分配给单个site位置,除非使用LOC属性进行约束。只有仅驱动非时钟负载的时钟缓存可以基于它们的驱动器和负载的布局移动到该流程中稍后的不同时钟区域。在此阶段的任

- FPGA时钟域处理

cycf

fpga开发

FPGA时钟域处理文章目录FPGA时钟域处理前言一、时钟域的管理1时钟资源二、跨时钟域设计1.1单bit信号跨时钟域1.1.1慢到快1.1.2快到慢1.1.3慢到快1.2多bit(这里指简单的多个控制信号)三、时钟域区域划分四使用衍生时钟的注意事项4.1原则14.2原则24.3原则3总结前言FPGA在代码设计的时候要考虑不同功能会有不同的时钟域,在设计构思的时候就要考虑到框图中的时钟域划分。一般都

- 什么是FPGA开发?

博览鸿蒙

FPGAfpga开发

FPGA(Field-ProgrammableGateArray),即现场可编程门阵列,是一种通过编程方式实现特定功能的集成电路。与传统的ASIC(专用集成电路)相比,FPGA具有灵活性高、开发周期短、成本相对较低等优势,因此在通信、数据中心、汽车、工业控制等领域得到广泛应用。如果按照应用场景给FPGA应用分类,可以分为高速接口、数据处理、逻辑控制等,在实际工作中也可以根据这些方向进行求职。虽然不

- vivado生成ltx文件命令_实验室自研工具Vivado Batch Mode Tool介绍!

电动星球蟹老板

vivado生成ltx文件命令

这里从两个方面分别进行说明,为什么要使用Vivado的Batchmode。1、流程操作效率我所谓的流程操作效率,是指在使用Vivado时,通过键盘输入、鼠标点击以及进行等待等实际外部操作的效率。例如我需要打开一个Vivado工程,并进行Synthesis,那么在GUI下是这样的流程操作:点击打开VivadoGUI并等待----用Vivado点击打开对应的.xpr文件并等待----点击runSynt

- Verilog中阻塞赋值和非阻塞赋值的区别?

张小侃

数字IC知识fpga硬件

阻塞赋值“=”对应组合逻辑电路赋值(无存储功能,立即赋值),并且会阻塞后面的赋值操作,非阻塞赋值“<=”对应时序逻辑电路赋值(有存储功能),所有非阻塞赋值操作在同一时刻进行赋值。下面分别通过vivado综合不同情况赋值的代码。第一种:在时序逻辑电路中使用阻塞赋值,通过综合后的电路可以看出非阻塞赋值综合出来的电路时立即执行赋值操作,和组合逻辑电路特性一致,无缓存功能,out_o直接被优化掉了。alw

- FPGA Verilog 阻塞赋值和非阻塞赋值

杭州秃头程序猿

fpga开发嵌入式硬件

阻塞赋值和非阻塞赋值的区别阻塞赋值阻塞赋值(=)必须是阻塞赋值完成后,才进行下一条语句的执行;赋值一旦完成,等号左边的变量值立即变化。串行,立即生效。如b=a;赋值语句执行完后,块才结束。b的值在赋值语句执行完后立刻就改变的。可能会产生意想不到的结果。非阻塞赋值非阻塞赋值(<=),在赋值开始时计算表达式右边的值,在本次仿真周期结束时才更新被赋值变量,即赋值不是立即生效的;非阻塞赋值允许块中其他语句

- 简单组合逻辑

一条九漏鱼

verilog开发实战指南fpga开发

多路选择器在多路数据传输过程中,能够将任意一路选出来的电路叫做数据选择器,也称多路选择器。对于一个具有2^n个输入和一个输出的多路选择器,有n个选择变量,多路选择器也是FPGA内部的一个基本资源,主要用于内部信号的选通。简单的多路选择器还可以通过级联生成更大的多路选择器。译码器译码是编码的逆过程,在编码时,每一种二级制都有特定的含义,都表示一个确定的信号。把代码状态的含义翻译出来的过程叫做译码,实

- ARM、DSP和FPGA技术浅析

mosquito88881

嵌入式ARMDSP和FPGA技术浅析

摘要:本文简要的介绍了ARM、DSP和FPGA的区别和发展趋势。1、ARM与DSP和FPGA简介ARM(AdvancedRISCMachines)是微处理器行业的一家知名企业,设计了大量高性能、低价、低功耗的RISC处理器,研究微处理器相关技术,以及开发工具等。ARM架构是面向低预算市场设计的第一款RISC微处理器,基本是32位单片机的行业标准,它提供一系列内核、体系扩展、微处理器和系统芯片方案,

- 工程师思维是什么?FPGA工程师要有哪些思维习惯?

博览鸿蒙

FPGAfpga开发

芯片工程师(包括FPGA工程师)仅仅拥有知识基础和工作技能是不够的。思维方式同样至关重要。正如柏拉图所说,“思维是灵魂的自我谈话”。在FPGA行业,良好的思维习惯对工程师来说尤为重要。那么,FPGA工程师应该具备哪些核心思维习惯呢?全局思维全局思维是指考虑问题时能够由点及线,由线及面地进行系统性思考。简单来说,就是要有大局观。以FPGA设计为例,一个模块代码的修改并非简单地修改代码就完成了。工程师

- 零中频接收机探讨

xfaxisss

技术分享硬件架构

随着信息技术的发展,数字及模拟对信号带宽要求越来越高,传统超外差结构复杂,成本高昂,且带宽增加对带内平坦度带来巨大挑战,大规模数字FPGA的发展,使得采用零中频技术可实现大带宽信号处理,降低硬件成本。图1传统超外差接收机结构需要考虑镜像抑制,预选滤波,中频滤波,设计结构复杂;可能需要采用多个高中频,带来带内不平坦、杂散等问题。图2模拟零中频接收机架构没有镜像抑制要求;采用相同ADC情况下,带宽是超

- xilinx vivado PULLMODE 设置思路

坚持每天写程序

fpga开发

1.xilinx引脚分类XilinxIO的分类:以XC7A100TFGG484为例,其引脚分类如下:1.UserIO(用户IO):用户使用的普通IO1.1专用(Dedicated)IO:命名为IO_LXXY_#、IO_XX_#的引脚,有固定的特定用途,多为底层特定功能的直接实现,如差分对信号、关键控制信号等,不能随意变更。1.2多功能(Multi-Function)IO:命名为IO_LXXY_ZZ

- (179)时序收敛--->(29)时序收敛二九

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛二九(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)

- Enum用法

不懂事的小屁孩

enum

以前的时候知道enum,但是真心不怎么用,在实际开发中,经常会用到以下代码:

protected final static String XJ = "XJ";

protected final static String YHK = "YHK";

protected final static String PQ = "PQ";

- 【Spark九十七】RDD API之aggregateByKey

bit1129

spark

1. aggregateByKey的运行机制

/**

* Aggregate the values of each key, using given combine functions and a neutral "zero value".

* This function can return a different result type

- hive创建表是报错: Specified key was too long; max key length is 767 bytes

daizj

hive

今天在hive客户端创建表时报错,具体操作如下

hive> create table test2(id string);

FAILED: Execution Error, return code 1 from org.apache.hadoop.hive.ql.exec.DDLTask. MetaException(message:javax.jdo.JDODataSto

- Map 与 JavaBean之间的转换

周凡杨

java自省转换反射

最近项目里需要一个工具类,它的功能是传入一个Map后可以返回一个JavaBean对象。很喜欢写这样的Java服务,首先我想到的是要通过Java 的反射去实现匿名类的方法调用,这样才可以把Map里的值set 到JavaBean里。其实这里用Java的自省会更方便,下面两个方法就是一个通过反射,一个通过自省来实现本功能。

1:JavaBean类

1 &nb

- java连接ftp下载

g21121

java

有的时候需要用到java连接ftp服务器下载,上传一些操作,下面写了一个小例子。

/** ftp服务器地址 */

private String ftpHost;

/** ftp服务器用户名 */

private String ftpName;

/** ftp服务器密码 */

private String ftpPass;

/** ftp根目录 */

private String f

- web报表工具FineReport使用中遇到的常见报错及解决办法(二)

老A不折腾

finereportweb报表java报表总结

抛砖引玉,希望大家能把自己整理的问题及解决方法晾出来,Mark一下,利人利己。

出现问题先搜一下文档上有没有,再看看度娘有没有,再看看论坛有没有。有报错要看日志。下面简单罗列下常见的问题,大多文档上都有提到的。

1、没有返回数据集:

在存储过程中的操作语句之前加上set nocount on 或者在数据集exec调用存储过程的前面加上这句。当S

- linux 系统cpu 内存等信息查看

墙头上一根草

cpu内存liunx

1 查看CPU

1.1 查看CPU个数

# cat /proc/cpuinfo | grep "physical id" | uniq | wc -l

2

**uniq命令:删除重复行;wc –l命令:统计行数**

1.2 查看CPU核数

# cat /proc/cpuinfo | grep "cpu cores" | u

- Spring中的AOP

aijuans

springAOP

Spring中的AOP

Written by Tony Jiang @ 2012-1-18 (转)何为AOP

AOP,面向切面编程。

在不改动代码的前提下,灵活的在现有代码的执行顺序前后,添加进新规机能。

来一个简单的Sample:

目标类:

[java]

view plain

copy

print

?

package&nb

- placeholder(HTML 5) IE 兼容插件

alxw4616

JavaScriptjquery jQuery插件

placeholder 这个属性被越来越频繁的使用.

但为做HTML 5 特性IE没能实现这东西.

以下的jQuery插件就是用来在IE上实现该属性的.

/**

* [placeholder(HTML 5) IE 实现.IE9以下通过测试.]

* v 1.0 by oTwo 2014年7月31日 11:45:29

*/

$.fn.placeholder = function

- Object类,值域,泛型等总结(适合有基础的人看)

百合不是茶

泛型的继承和通配符变量的值域Object类转换

java的作用域在编程的时候经常会遇到,而我经常会搞不清楚这个

问题,所以在家的这几天回忆一下过去不知道的每个小知识点

变量的值域;

package 基础;

/**

* 作用域的范围

*

* @author Administrator

*

*/

public class zuoyongyu {

public static vo

- JDK1.5 Condition接口

bijian1013

javathreadConditionjava多线程

Condition 将 Object 监视器方法(wait、notify和 notifyAll)分解成截然不同的对象,以便通过将这些对象与任意 Lock 实现组合使用,为每个对象提供多个等待 set (wait-set)。其中,Lock 替代了 synchronized 方法和语句的使用,Condition 替代了 Object 监视器方法的使用。

条件(也称为条件队列或条件变量)为线程提供了一

- 开源中国OSC源创会记录

bijian1013

hadoopsparkMemSQL

一.Strata+Hadoop World(SHW)大会

是全世界最大的大数据大会之一。SHW大会为各种技术提供了深度交流的机会,还会看到最领先的大数据技术、最广泛的应用场景、最有趣的用例教学以及最全面的大数据行业和趋势探讨。

二.Hadoop

&nbs

- 【Java范型七】范型消除

bit1129

java

范型是Java1.5引入的语言特性,它是编译时的一个语法现象,也就是说,对于一个类,不管是范型类还是非范型类,编译得到的字节码是一样的,差别仅在于通过范型这种语法来进行编译时的类型检查,在运行时是没有范型或者类型参数这个说法的。

范型跟反射刚好相反,反射是一种运行时行为,所以编译时不能访问的变量或者方法(比如private),在运行时通过反射是可以访问的,也就是说,可见性也是一种编译时的行为,在

- 【Spark九十四】spark-sql工具的使用

bit1129

spark

spark-sql是Spark bin目录下的一个可执行脚本,它的目的是通过这个脚本执行Hive的命令,即原来通过

hive>输入的指令可以通过spark-sql>输入的指令来完成。

spark-sql可以使用内置的Hive metadata-store,也可以使用已经独立安装的Hive的metadata store

关于Hive build into Spark

- js做的各种倒计时

ronin47

js 倒计时

第一种:精确到秒的javascript倒计时代码

HTML代码:

<form name="form1">

<div align="center" align="middle"

- java-37.有n 个长为m+1 的字符串,如果某个字符串的最后m 个字符与某个字符串的前m 个字符匹配,则两个字符串可以联接

bylijinnan

java

public class MaxCatenate {

/*

* Q.37 有n 个长为m+1 的字符串,如果某个字符串的最后m 个字符与某个字符串的前m 个字符匹配,则两个字符串可以联接,

* 问这n 个字符串最多可以连成一个多长的字符串,如果出现循环,则返回错误。

*/

public static void main(String[] args){

- mongoDB安装

开窍的石头

mongodb安装 基本操作

mongoDB的安装

1:mongoDB下载 https://www.mongodb.org/downloads

2:下载mongoDB下载后解压

- [开源项目]引擎的关键意义

comsci

开源项目

一个系统,最核心的东西就是引擎。。。。。

而要设计和制造出引擎,最关键的是要坚持。。。。。。

现在最先进的引擎技术,也是从莱特兄弟那里出现的,但是中间一直没有断过研发的

- 软件度量的一些方法

cuiyadll

方法

软件度量的一些方法http://cuiyingfeng.blog.51cto.com/43841/6775/在前面我们已介绍了组成软件度量的几个方面。在这里我们将先给出关于这几个方面的一个纲要介绍。在后面我们还会作进一步具体的阐述。当我们不从高层次的概念级来看软件度量及其目标的时候,我们很容易把这些活动看成是不同而且毫不相干的。我们现在希望表明他们是怎样恰如其分地嵌入我们的框架的。也就是我们度量的

- XSD中的targetNameSpace解释

darrenzhu

xmlnamespacexsdtargetnamespace

参考链接:

http://blog.csdn.net/colin1014/article/details/357694

xsd文件中定义了一个targetNameSpace后,其内部定义的元素,属性,类型等都属于该targetNameSpace,其自身或外部xsd文件使用这些元素,属性等都必须从定义的targetNameSpace中找:

例如:以下xsd文件,就出现了该错误,即便是在一

- 什么是RAID0、RAID1、RAID0+1、RAID5,等磁盘阵列模式?

dcj3sjt126com

raid

RAID 1又称为Mirror或Mirroring,它的宗旨是最大限度的保证用户数据的可用性和可修复性。 RAID 1的操作方式是把用户写入硬盘的数据百分之百地自动复制到另外一个硬盘上。由于对存储的数据进行百分之百的备份,在所有RAID级别中,RAID 1提供最高的数据安全保障。同样,由于数据的百分之百备份,备份数据占了总存储空间的一半,因而,Mirror的磁盘空间利用率低,存储成本高。

Mir

- yii2 restful web服务快速入门

dcj3sjt126com

PHPyii2

快速入门

Yii 提供了一整套用来简化实现 RESTful 风格的 Web Service 服务的 API。 特别是,Yii 支持以下关于 RESTful 风格的 API:

支持 Active Record 类的通用API的快速原型

涉及的响应格式(在默认情况下支持 JSON 和 XML)

支持可选输出字段的定制对象序列化

适当的格式的数据采集和验证错误

- MongoDB查询(3)——内嵌文档查询(七)

eksliang

MongoDB查询内嵌文档MongoDB查询内嵌数组

MongoDB查询内嵌文档

转载请出自出处:http://eksliang.iteye.com/blog/2177301 一、概述

有两种方法可以查询内嵌文档:查询整个文档;针对键值对进行查询。这两种方式是不同的,下面我通过例子进行分别说明。

二、查询整个文档

例如:有如下文档

db.emp.insert({

&qu

- android4.4从系统图库无法加载图片的问题

gundumw100

android

典型的使用场景就是要设置一个头像,头像需要从系统图库或者拍照获得,在android4.4之前,我用的代码没问题,但是今天使用android4.4的时候突然发现不灵了。baidu了一圈,终于解决了。

下面是解决方案:

private String[] items = new String[] { "图库","拍照" };

/* 头像名称 */

- 网页特效大全 jQuery等

ini

JavaScriptjquerycsshtml5ini

HTML5和CSS3知识和特效

asp.net ajax jquery实例

分享一个下雪的特效

jQuery倾斜的动画导航菜单

选美大赛示例 你会选谁

jQuery实现HTML5时钟

功能强大的滚动播放插件JQ-Slide

万圣节快乐!!!

向上弹出菜单jQuery插件

htm5视差动画

jquery将列表倒转顺序

推荐一个jQuery分页插件

jquery animate

- swift objc_setAssociatedObject block(version1.2 xcode6.4)

啸笑天

version

import UIKit

class LSObjectWrapper: NSObject {

let value: ((barButton: UIButton?) -> Void)?

init(value: (barButton: UIButton?) -> Void) {

self.value = value

- Aegis 默认的 Xfire 绑定方式,将 XML 映射为 POJO

MagicMa_007

javaPOJOxmlAegisxfire

Aegis 是一个默认的 Xfire 绑定方式,它将 XML 映射为 POJO, 支持代码先行的开发.你开发服 务类与 POJO,它为你生成 XML schema/wsdl

XML 和 注解映射概览

默认情况下,你的 POJO 类被是基于他们的名字与命名空间被序列化。如果

- js get max value in (json) Array

qiaolevip

每天进步一点点学习永无止境max纵观千象

// Max value in Array

var arr = [1,2,3,5,3,2];Math.max.apply(null, arr); // 5

// Max value in Jaon Array

var arr = [{"x":"8/11/2009","y":0.026572007},{"x"

- XMLhttpRequest 请求 XML,JSON ,POJO 数据

Luob.

POJOjsonAjaxxmlXMLhttpREquest

在使用XMlhttpRequest对象发送请求和响应之前,必须首先使用javaScript对象创建一个XMLHttpRquest对象。

var xmlhttp;

function getXMLHttpRequest(){

if(window.ActiveXObject){

xmlhttp:new ActiveXObject("Microsoft.XMLHTTP

- jquery

wuai

jquery

以下防止文档在完全加载之前运行Jquery代码,否则会出现试图隐藏一个不存在的元素、获得未完全加载的图像的大小 等等

$(document).ready(function(){

jquery代码;

});

<script type="text/javascript" src="c:/scripts/jquery-1.4.2.min.js&quo