STM32F10XX 硬件入门 阅读笔记一:电源供应

1.1介绍

1. 独立ADC转换器可以在VREF+单独供电,供电电压范围从2.4V到VDDA(仅在100pin,140pin封装中可用;在64pin及小于64pin的封装中不可用,VREF+和VREF-已在内部连接VDDA和VssA)

2. 后备电池

为了保持备份寄存器中的数据,当VDD变低时,VBAT作为待机电压连接到备份电路(包含RTC电路)。连接VBAT电源的开关由(PDR)电源下降复位电路控制。

3. 电压整流器

电压整流器在复位之后被使能。它根据应用模式工作在三种模式下:

运行模式:电压整流器为1.8V区域(核心,内存,数字外围)

停止模式:电压整流器为1.8V区域提供部分电源(保留SRAM和寄存器中的内容)

待机模式:电压整流器关断。SRAM和寄存器中的内容(除了与备份电路相关的)将丢失。

1.2能量供应计划

1. 电路供电电压范围为2.0~3.6V,当ADC电路启用时,供电电压范围为2.4V~3.6V。

2. VDD引脚在连接电源时,每一个VDD引脚需要连接外部去耦电容100nF陶瓷电容+1个钽电容或陶瓷电容(最小4.7uF,典型值10uF)。

3. VBAT可以连接外部电池(大于1.8V,小于3.6V),如果没有,可以将VBAT连接至VDD。

4. VDDA引脚必须连接两个外部去耦电容(100nF的陶瓷电容+1uF的钽电容或陶瓷电容)

5. VREF+可以分离供电,但都保持电压在2.4V~VDDA

6. 额外的降低模拟噪声的措施:VDDA可以通过一个磁珠与VDD相连;VREF+可以通过一个电阻(典型值47Ω)与VDDA相连。

1.3复位和供电监视

1.POR(Power onreset)/PDR(Power down reset)

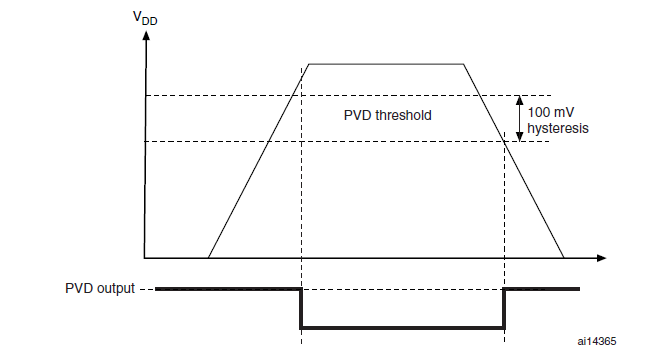

2. PVD(Programmable voltage detector)

3. 系统复位

系统复位将重置(除了在时钟控制状态寄存器(CSR)中的复位标志,和在备份域中的寄存器)

复位产生:在NRST引脚的低电平(外部复位);窗口看门狗有效计数条件(窗口看门狗);独立看门狗有效计数条件(独立看门狗复位);软件复位(SW复位);低功耗管理复位。

复位源可以通过检查在时钟控制状态寄存器(CSR)中的复位标志判断。

4. 复位电路:复位引脚已经内部上拉,不需要外部上拉。。为了改善EMS(电磁干扰)避免设备寄生复位,需要一个下拉电容。。下拉电容充放电过程通过内部电阻增加了设备的能量损耗,电容建议值100nF(可以减小至10nF以限制能量损耗)