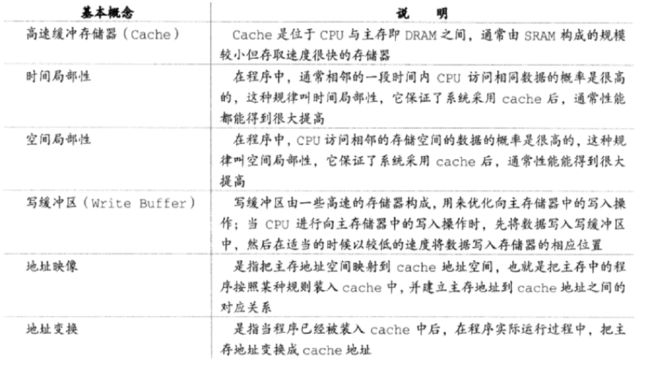

ARM处理器的Cache之cortex a8

原文地址:http://blog.chinaunix.net/uid-28458801-id-3494289.html

Cache 是位于 CPU与主存储器DRAM(Dynamic RAM,动态存储器)之间的少量超高速静态存储器 SRAM(static RAM),其是为了解决 CPU 与 主存之间速度匹配问题而设置的,不能由用户直接寻址访问。

具有 Cache 的计算机,当 CPU 需要进行存储器存取时,首先检查所需数据是否在 Cache中。如果存在,则可以直接存取其中的数据而不必插入任何等待状态,这是最佳状态,称为高速命中;当 CPU 所需信息不在 Cache 中时,则需切换存取主存储器,由于速度较慢,需要插入等待,这种情况称为 高速未命中;在CPU存取主存储器的时候,按照最优化原则将存储信息同时写入到 Cache 中以保证下次可能的高速缓存命中。因此,同一数据可能同时存储在主存储器和 Cache 中。

传统的 Socket 架构通常采用两级缓冲结构,即在 CPU 中集成了 一级缓存(L1 Cache),在主板上装二级缓存(L2 Cache)。

CPU 首先在 L1 Cache 中查找数据,如找不到,则在 L2 Cache 中查找,如果数据在 L2 Cache 中,控制器在传输数据的同时,修改 L1 Cache;若数据既不在 L1 Cache中,也不在 L2 Cache中,控制器则从主存储器中获取数据,将数据提供给CPU的同时修改两级 Cache。

在主存储器--Cache存储体系中,所有的指令和数据都存在主存储器中,Cache只是存放主存储器中的一部分程序块和数据块的副本,只是一种以块为单位的存储方式。Cache 和 主存储器被分为块,每块有多个字节组成。

CPU访问存储器时,送出访问单元的地址,由地址总线传送到 Cache 控制器中的主存储器地址寄存器 MA 中,主存储器 -- Cache 地址转换机从 MA 获取地址并判断该单元内容是否已在 Cache中存在副本,如果副本已存在于Cache 中,即命中。当命中时,立即把访问地址变换成其在Cache 中的地址,然后访问Cache。

如果CPU要访问的内容不再 Cache 中,即不命中,则CPU转去直接访问主存储器,并将包含此存储单元的整个数据块(包括该块数据的地址信息)传到 Cache 中,使得以后的若干次对内存的访问可转化为对 Cache 的访问。若 Cache 存储器已满,则需在替换控制部件的控制下,根据某种替换算法/策略,用此块信息替换掉 Cache 原有的某块信息。

ARM处理器中的 Cache 和 Write Buffer:

Cache 分类

根据不同的分类标准可以按以下 3 种方法对 Cache 进行分类。

1,数据 cache 和 指令 cache

* 指令 cache :指令预取时使用的 cache。

* 数据 cache :数据读写时使用的 cache。

如果一个存储系统中指令 cache 和 数据 cache 是同一个 cache,称系统使用了统一的cache。反之,如果是分开的,那么称系统使用了独立的cache;如果系统中只包含指令cache或者数据cache,那么在配制系统时可以作为独立的cache使用。

使用独立的数据 cache 和指令 cache,可以在同一个时钟周期中读取指令和数据,而不需要双端口的 cache,但这时要注意保证指令和数据的一致性。

2,写通(write-throught)cache 和 写回(write-back)cache

*写回 cache

CPU在执行写操作时,被写的数据只写入 cache,不写入主存储器中,仅当需要替换时,才把已经修改的cache块写回到主存储器中。

在使用这种更新算法的cache 块表中,一般有一个修改位,当一块中的任何一个单元被修改,这一块的修改位被设置为 1,否则这一块的修改位仍保持为 0;在需要替换这一块时,如果对应的修改位为 1,则必须先把这一块写到主存储器中去之后,才能调入新的块,否则,只要用新调入的块覆盖该块即可。

*写通 cache

CPU 在执行写操作时,必须把数据同时写入 cache 和主存储器中,这样,在 cache的块表中就不需要“修改位”,当某一块需要替换时,也不必把这一块写回到主存储器中,新调入的块可以立即直接把这一块覆盖掉。

3,读时分配(read-allocate)cache 和 写时分配(write-allocate)cache

* 读时分配 cache

当进行数据写操作时,如果cache没命中,只是简单的将数据写入到主存储器中,主要在数据读取时,才进行 cache 内容预取。

* 写时分配 cache

在进行数据写操作时,如果cache没命中,cache 系统将会进行 cache 内容预取,从主存储器中将相应的块读取到 cache 中相应的位置,并执行写操作,把数据写入到 cache 中。对于写通类型的cache,数据将会同时写入到主存储器中,对于写回类型的 cache,数据将在合适的时候写回到主存储器中。

ARM 处理器中的 Cache 和 Write Buffer 操作是通过 CP15 的 C7 寄存器来实现的。访问 CP15 的 C7 寄存器的指令格式如下:

mcr p15, 0,

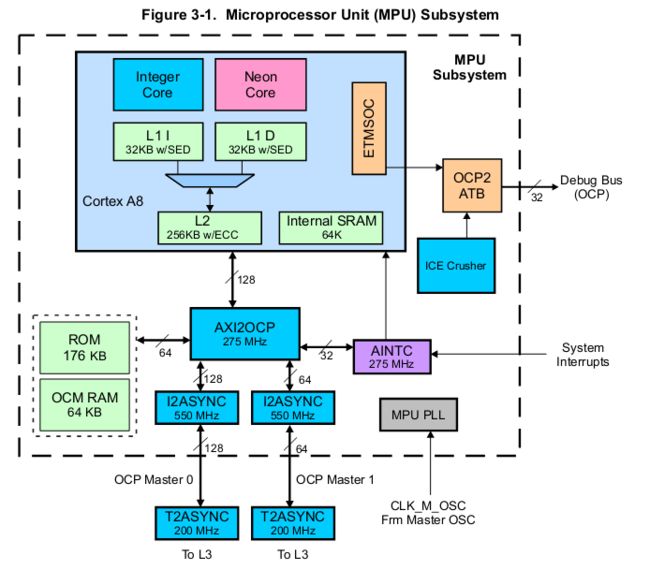

以 am335x 为实例:

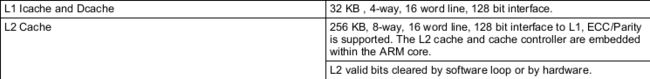

am335x arm cortex a8 中 Cache :

Cache

|------L1 Cache

| |------L1 Icache (32 KB 独立的指令 cache)

| |------L1 Dcache (32 KB 独立的数据 cache )

|------L2 Cache (256KB)

L1 C ac h e

一级高速缓存,其容量一般为几十~ 几百K B ,频率与C P U 相同。 L 1 C ac h e 可以提

高C P U 的运行效率,它的容量和结构对C P U 的性能影响较大。 L 1 C ac h e 越大,系统性

能提高越明显。

L2 C ac h e

二级高速缓存,其容量一般相当于L 1 C ac h e 的4 ~ 8 倍。 L 2 C ac h e 的容量和频率对

C P U 的性能影响也较大,L 2 C a c h e 的时钟频率一般为C P U 主频的1 /2 、2 /5 和1 /3