MYIR-ZYNQ7000系列-zturn教程(26):自定义axi_lite IP点亮LED灯

开发板环境:vivado 2017.4 ,开发板型号xc7z020clg400-1,这个工程主要功能是自定义一个axi_lite IP然后

在SDK中控制LED闪烁

工程链接:https://pan.baidu.com/s/1W2p50NZP6hKMQEdFbTcLDA 提取码:r5kn

step1 新建一个vivado工程和自定义一个axi_lite IP核

然后在这个工程路径下新建一个IP文件夹用于存放自定义IP所产生的文件

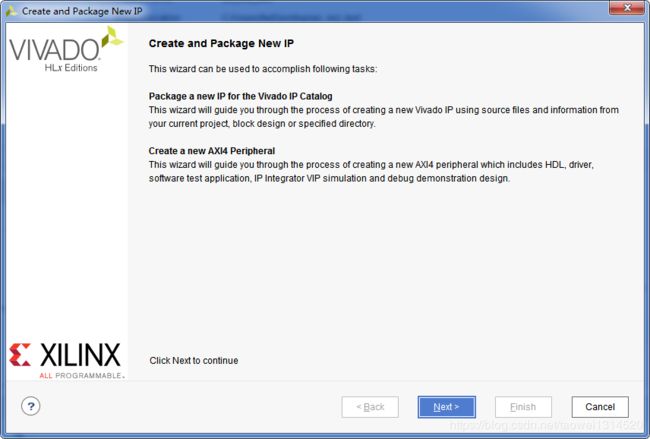

点击Tools-->Create Interface Definition New IP

点击Next

选择这个AXI4,然后点击Next

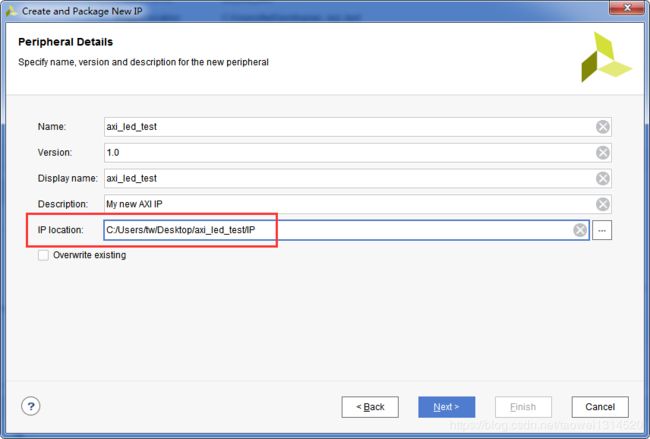

这里的显示名称可以随便取名

这里IP存放路径,选择我们刚刚新建IP文件夹的路径,然后点Next

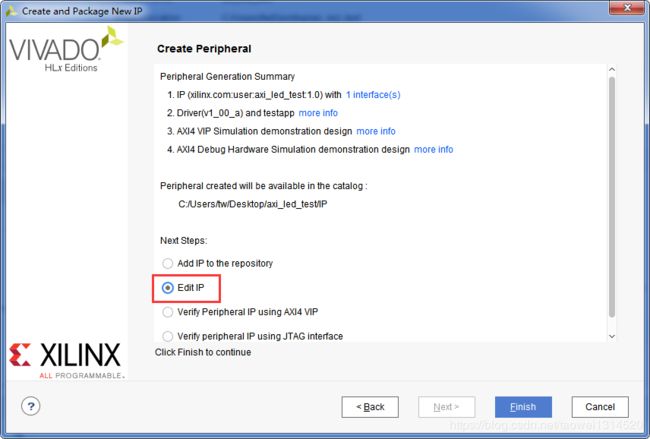

这里都选择默认,点击Next

选择Edit IP,点击Finish

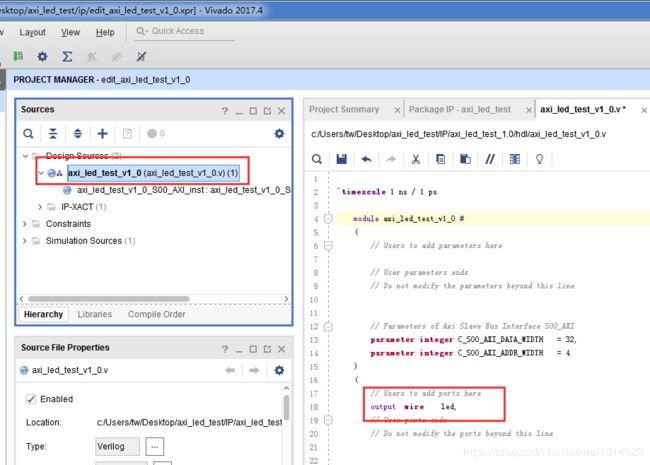

在弹出的对话框中选择axi_led_test_v1_0 ,然添加一个led输出端口

将led端口例化进来

在axi_led_test_v1_0_S00_AXI_inst中添加led端口如下图所示

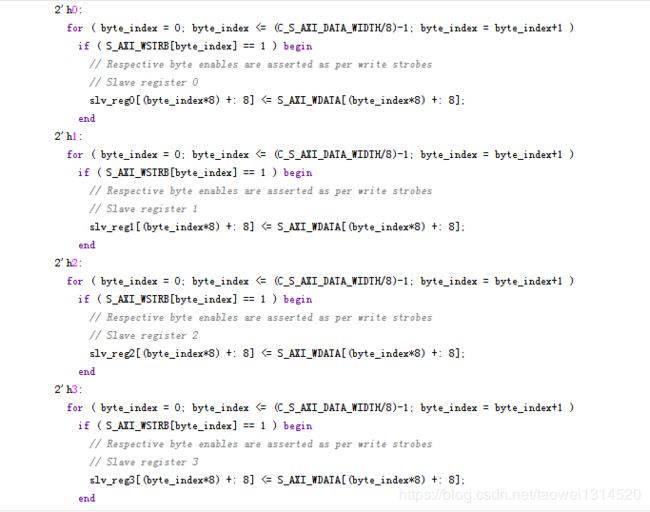

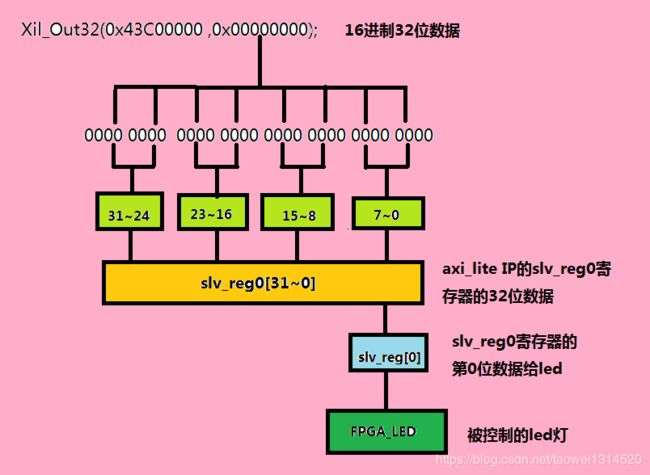

axi_lite一共32数据位宽,有四个32位寄存器,下面就是对四个寄存器进行写,每一个寄存器32位,

我这里只对slv_reg0进行操作

这里读取四个寄存器的值

我们这个自定义IP做为一个输出口,一般只会用到写功能,也就是对相应位写值来控制电平,

所以这里的读其实可以屏蔽,这里我就不屏蔽,因为后面的SDK程序我只会进行写不会进行读

下面这个截图是将第一个32位寄存器slv_reg0的最低位的电平给led,只要在SDK里对第一个寄存器

进行操作就可以控制led闪烁

点击Merge changes from File Groups Wizard

点击Merge changes from File Groups Wizard

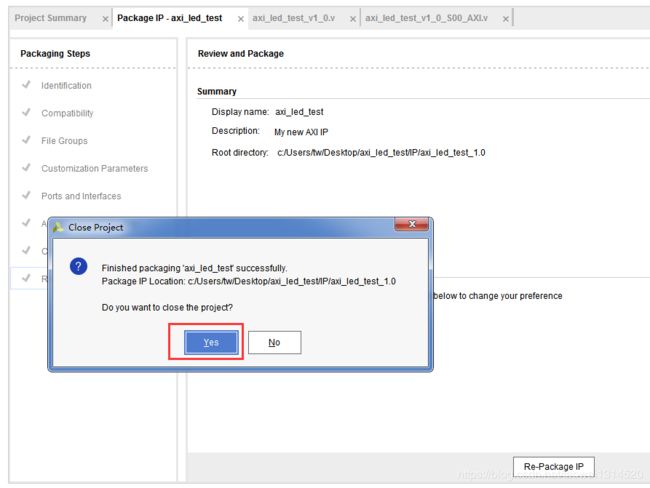

点击Re-Package IP 生成自定义axi_lite IP

点击Yes

生成的自定义IP如下图所示

step2 添加自定义IP

点击Settings

我这里直接自动添加进来了,如果你自己生成的IP这里没有,可以点击+将自己新建的IP添加进来

step3 添加zynq核将自定义IP挂接到zynq上

点击Create Block Design

点击OK

添加ZYNQ核并配置参数,不同的开发板设置不同,只要根据自己的开发板进行设置就可以了

双击axi_led_test添加自定义的IP

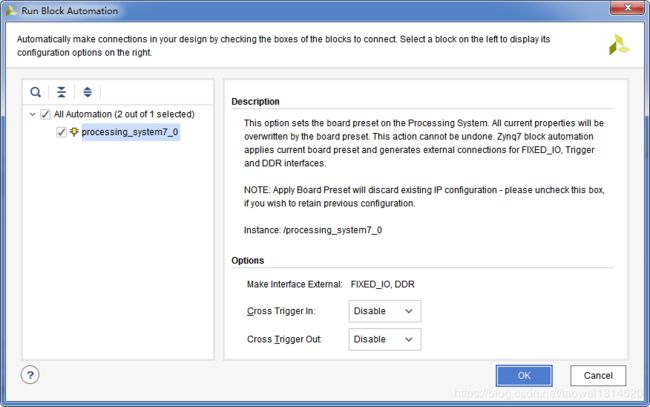

点击Run Block Automation

点击OK

点击Run Connection Automation

点击OK

自动连线完成如下图所示

右击--> Make Extemal 引出led管脚

引出的led管脚如下图所示

这个0x43C00000 就是这个自定义IP的地址,我们在SDK中给这个地址写值就可以控制led

step4 综合、生成顶层文件,生成bit文件

综合

生成顶层文件

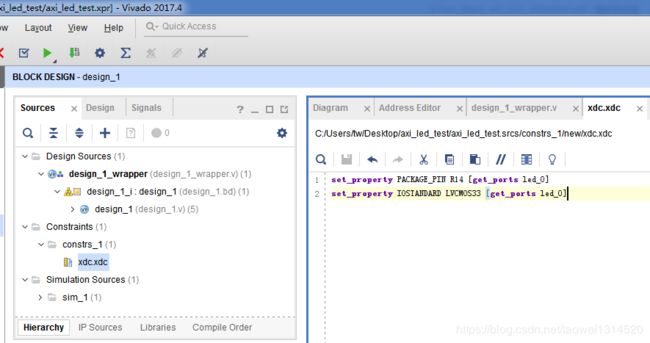

添加管脚约束,这里的自定义led管脚接的fpga上的led

生成bit文件

step5 导出硬件配置,打开SDK,新建fsbl

导出硬件配置

点击OK

打开SDK

点击OK

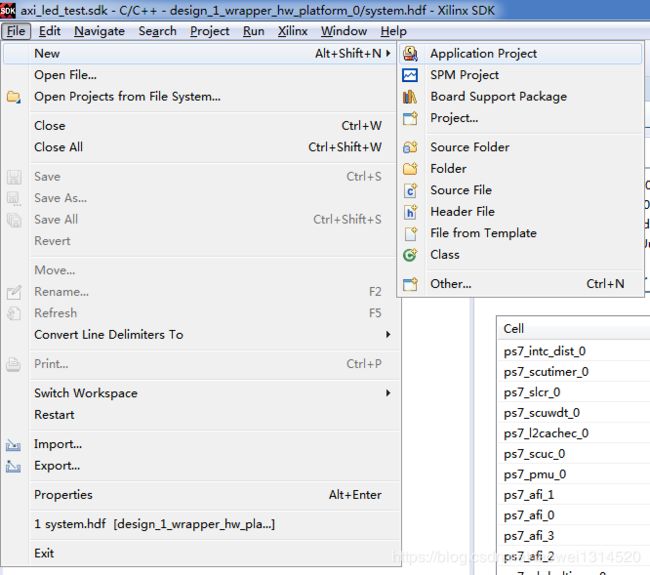

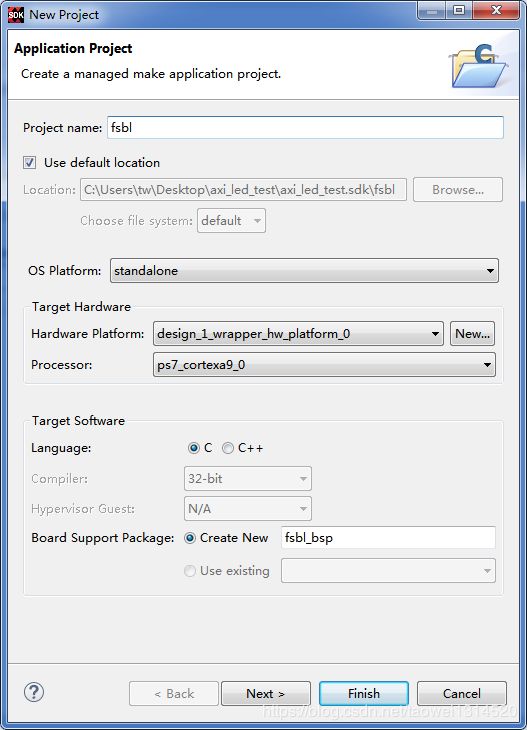

点击File--> Application Project新建工程

新建一个fsbl,点Next

选择Zynq FSBL,点Finish

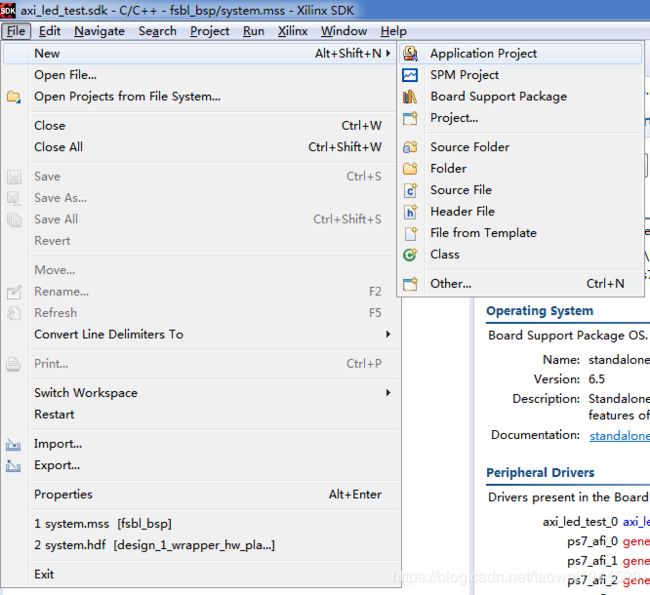

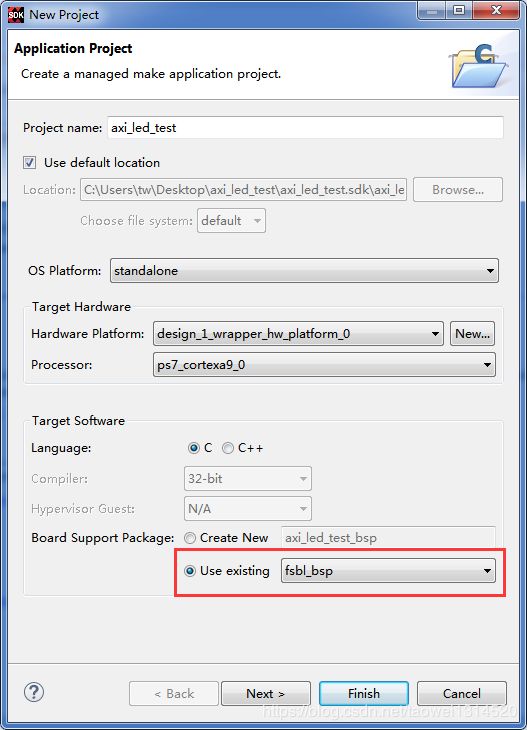

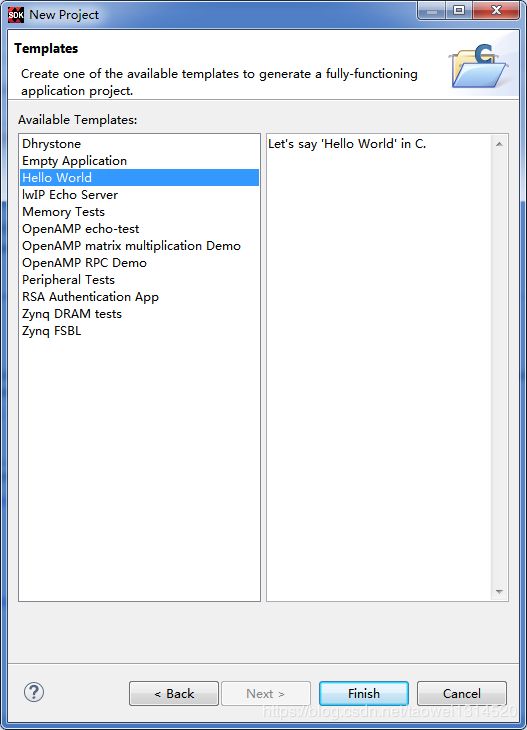

step6 新建axi_led_test工程

新axi_led_test工程,选择fsbl_bsp,然后点击Next

选择hello_world工程模板,点击Finish

主程序

/******************************************************************************

*

* Copyright (C) 2009 - 2014 Xilinx, Inc. All rights reserved.

*

* Permission is hereby granted, free of charge, to any person obtaining a copy

* of this software and associated documentation files (the "Software"), to deal

* in the Software without restriction, including without limitation the rights

* to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

* copies of the Software, and to permit persons to whom the Software is

* furnished to do so, subject to the following conditions:

*

* The above copyright notice and this permission notice shall be included in

* all copies or substantial portions of the Software.

*

* Use of the Software is limited solely to applications:

* (a) running on a Xilinx device, or

* (b) that interact with a Xilinx device through a bus or interconnect.

*

* THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

* IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY,

* FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL

* XILINX BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY,

* WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, OUT OF

* OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE

* SOFTWARE.

*

* Except as contained in this notice, the name of the Xilinx shall not be used

* in advertising or otherwise to promote the sale, use or other dealings in

* this Software without prior written authorization from Xilinx.

*

******************************************************************************/

/*

* helloworld.c: simple test application

*

* This application configures UART 16550 to baud rate 9600.

* PS7 UART (Zynq) is not initialized by this application, since

* bootrom/bsp configures it to baud rate 115200

*

* ------------------------------------------------

* | UART TYPE BAUD RATE |

* ------------------------------------------------

* uartns550 9600

* uartlite Configurable only in HW design

* ps7_uart 115200 (configured by bootrom/bsp)

*/

#include

#include "platform.h"

#include "xil_printf.h"

#include "sleep.h"

int main()

{

while(1)

{

Xil_Out32(0x43C00000 ,0x00000000);

sleep(1);

Xil_Out32(0x43C00000 ,0x00000001);

sleep(1);

}

}

我这里分配的是三色灯中的一个,手机拍出来的看起来不太明显,我这里可以看到led不停闪烁说明这个工程没有问题

axi_lite IP的整体控制流程(这个图如果看懂了,这个axi_lite自定义IP也就理解差不多了)