Verilog HDL Coding Style Proposal

一、写在前面的话

话说Bingo触摸FPGA也有几年了,一开始学的VHDL,后来跟上了时代的潮流,又自学了Verilog,一直保持到了今天,似乎早已淡忘了VHDL的身影。

一开始的模仿,接下来不懂就查,直到最后掌握基本的代码规范,到此刻为止,从来没有看过altera官方的Verilog Coding Style。终于,此刻,下定决心,来规范一下自己的代码。

好的代码不仅是写给自己看的,更是为了让别人欣赏。一段完美代码,每一个毛孔都是那么的无懈可击。严格的规范,唯美的风格,赏心悦目,窥一斑可见整体。作为一个优秀的工程师,不管是软件工程是还是硬件工程师,养成良好的代码规范,于己于人,都将会有事半功倍的好处,因此,“唯美”,从此刻开始!

Altera_Verilog_Coding_Style.pdf

下载地址:

1) www.altera.com

2) www.chinaaet.com

二、规范我们的代码

1. 命名规范

我谨代表altera_verilog_coding_style.pdf,摘要了一些一般人不太注意甚至不知道的规则,希望那些不明真相的群众,能够从此看到自己的灵魂。

1) Use uppercase letters for all parameter names

2) Clock name should be clk or prefixed with clk

3) Active high reset signal should be prefixed with rst; Active low reset should be named rst_n

4) Three state signal name should have suffix _z

5) Instance names should begin with ‘U_’

6) Use a separate line for each HDL statement

7) Use four space code indentation

8) Operand sizes should match

2. 推介文件头格式

对于一段称得上“唯美”的代码,切不可少了龙头。所谓文件头,很多人不曾注意,这不仅仅是在于表面的注释自己,更重要的是能够养成规范的团队代码规范,让第三方能够更好的认知,修改,移植。

/*-------------------------------------------------------------------------

/*-------------------------------------------------------------------------

This confidential and proprietary software may be only used as authorized

by a licensing agreement from CrazyBingo.

(C) COPYRIGHT 2012 CrazyBingo. ALL RIGHTS RESERVED

Filename : led_matrix_display.v

Author : CrazyBingo

Data : 2012-01-18

Version : 0.1

Description : This file has the module of led_matrix_display top.

Modification History :

Data By Version Change Description

===========================================================================

12/01/18 CrazyBingo 0.1 Original

--------------------------------------------------------------------------*/

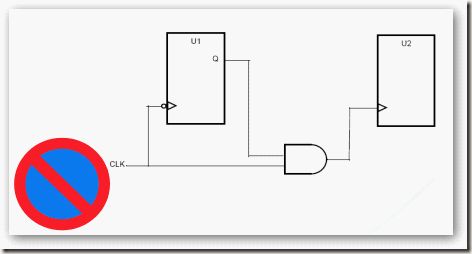

3. 时钟设计规则

很多时候,一个稍大的工程,一段自以为完美的代码,往往死在时钟之上,或是同步异步时钟,或是门控使能时钟,多半不明真相的群众,还是不能够掌握Verilog的时钟设计规则。

1) Buffers should not be explicitly added to clock path

2) Gated clocks are not allowed in the design(just use enable clock)

3) Clock should be visible from top unit. We recommend that designer can use block PLL/DLL to generate the internal clocks which can be distinguished by compile tool better

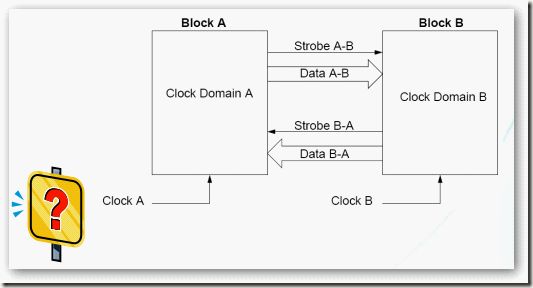

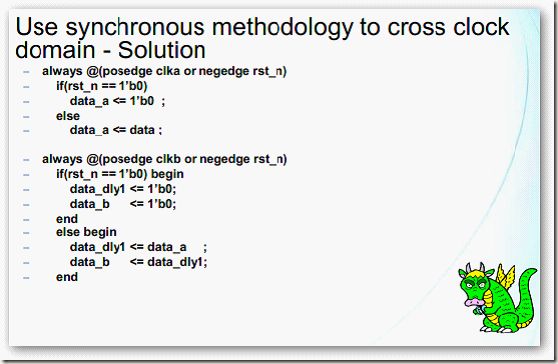

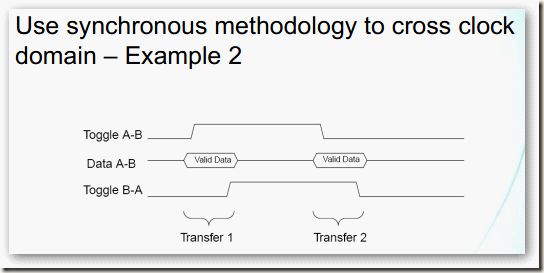

4) Use synchronous methodology to cross clock domain

5) Use synchronous methodology to cross clock domain

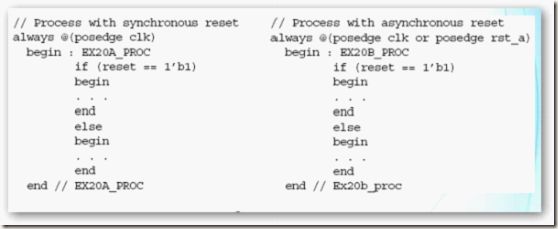

Asynchronous reset,synchronous release 异步复位,同步释放

6) Avoid internally generated reset/set/load

7) There should be at most one synchronous reset/set/load signal in a sequential block

4. 可综合之设计

1) Use 'if(<%context> == 'b1)' for rising edge asynchronous reset/set/load expressions

2) Use 'if(<%context> == 'b0)' for falling edge asynchronous reset/set/load expressions

3) Do not use initial constructs to initialize signals

4) Avoid inferring latches in design(case,if...else...)

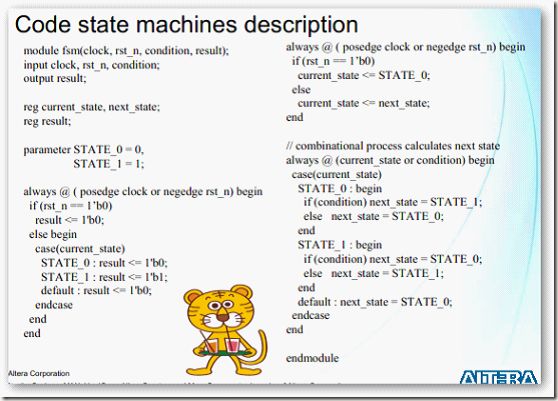

5) Code state machines description with two or there blocks

6) Use parameter statements to define the state vector of a state machine(推介三段式)

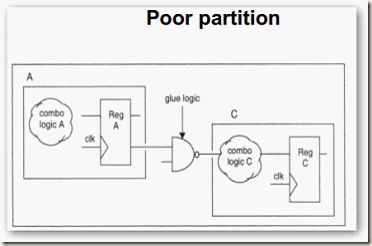

5. 基本划分规则

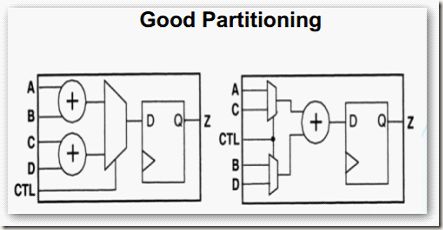

1) Locate related combinational logic in a single module

2) Separate Modules That Have Different Design Goals

3) Partition asynchronous logic from synchronous logic

4) Arithmetic operators: Merging resources

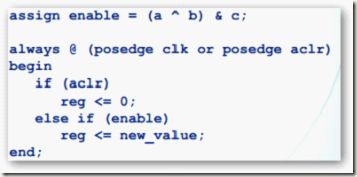

5) Eliminate glue logic at the top level(粘合逻辑:两个例化模块中间的logic)

6) If equation is needed to evaluate clock enable, use separate statement