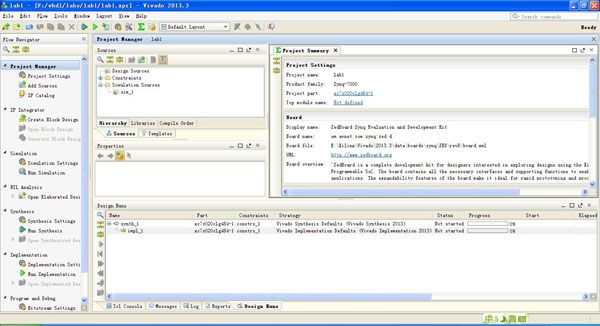

Vivado主界面

Vivado套件,相当于把ISE、ISim、XPS、PlanAhead、ChipScope和iMPACT等多个独立的套件集合在一个Vivado设计环境中,在这个集合的设计流程下,不同的设计阶段我们采用不同的工具来完成,此时Vivado可以自动变化菜单、工具栏,可以显著提高效率:因为不需要在多个软件间来回切换、调用,白白浪费大量的时间。基于Vivado IP集成器(IPI),则把我们对硬件的配置更好地集成到我们的设计中,既极大地提高了对IP的使用和管理,也帮助我们减小了软件和硬件(例如ZYNQ器件的PS)之间的隔阂。Vivado HLS则可以把现有的C代码,在一些特定的规范下直接转换为可综合的逻辑,这也将极大地提高我们实现和移植现有算法的速度。

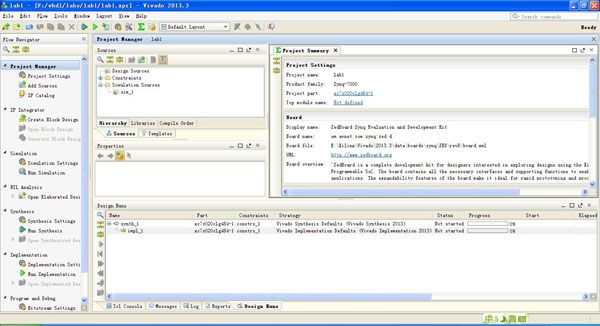

主界面主要包括:

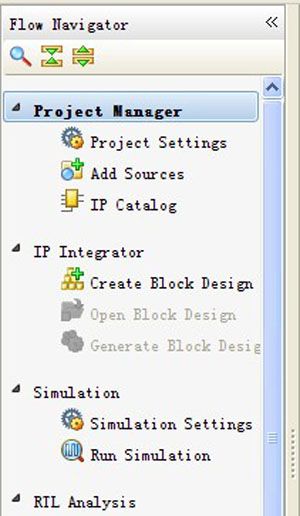

Flow Navigator: 在此可以找到整个设计过程中涉及到的所有流程

Sources: 工程包含的设计源文件,源码、约束等

Properties: 所选中对象的属性信息

Project Summary: 在此可以查看工程信息

Design Runs: 在此可以查看提示信息、警告、错误、也可以输入tcl命令

Vivado 新建工程时选中:do not specify(指定) sources at the time

对应器件xc7a200tfbg

IOB是可编程输入输出单元,英文缩写

显示查找表(Look-Up-Table)简称为LUT,LUT本质上就是一个RAM。它把数据事先写入RAM后,每当输入一个信号就等于输入一个地址进行查表,找出地址对应的内容,然后输出。

MSB最高有效位

LSB 最低有效位

Catalog 目录

Software:ZedBoard users:

o Cypress CY7C64225 USB-to-UART Bridge Driver

§ www.zedboard.org à Documentation à ZedBoard

Cypress USB-to-UART Setup Guide

Second USB cable (Type A to Micro-USB Type B)

AC/DC 12V Power Adapter

关于vivado的操作提示位于路径:

F:\Zedboard资料\zedboard_org资料form魏\ZynqHW\2014_4\Lab_instructions

同时参考vivado简明教程。

The_Zynq_Book_Tutorials

Synthesis 综合

设计步骤:创建工程——createblock design——add IP

Validate 验证

Implement 实施,生效

Create HDL Wrapper (包装):这将为我们的系统生成顶级HDL包装

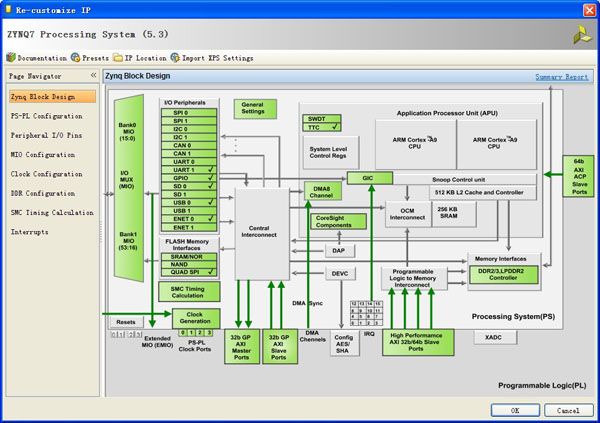

解Zedboard的核心ZYNQ:ZYNQ系列是赛灵思公司(Xilinx)推出的行业第一个可扩展处理平台,旨在为视频监视、汽车驾驶员辅助以及工厂自动化等高端嵌入式应用提供所需的处理与计算性能水平。该系列四款新型器件得到了工具和IP 提供商生态系统的支持,将完整的 ARM® Cortex™-A9 MPCore 处理器片上系统 (SoC) 与 28nm 低功耗可编程逻辑紧密集成在一起,可以帮助系统架构师和嵌入式软件开发人员扩展、定制、优化系统,并实现系统级的差异化。

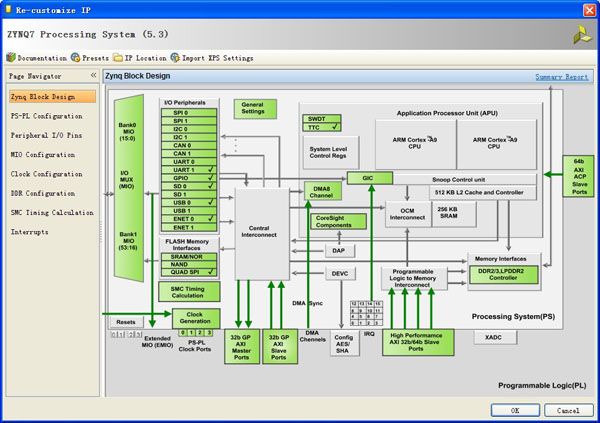

ZYNQ7 Processing System模块的配置,点击相应的模块进行配置。。。更为简便的方式是Diagram顶端的Run Block Automation设计协助链接来完成对ZYNQ7 Processing System IP核的配置并将DDR与FIXED_IO Make External

AXI GPIO IPcore:该IP核被放在PL端,通过AXI总线同ARM相连接,并通过GPIO接口控制ZedBoard上的8个LED小灯。

Processor System Reset: 这个IP提供一个定制化的Reset功能,包括所有外设,互联以及处理器生。

AXI Interconnect:提供AXI 总线互联控制,它将PL端外设同PS端连接起来。

由于ARM是统一编址的,所以在编写ARM程序的时候就可以像读写内存一样直接对该地址进行读写,从而实现对该IP核的控制。

Validate Design 按钮检测设计的有效性

Generate Output Products… 生成设计综合、仿真、实现的相关文件

Create HDL Wrapper: Vivado会为IP子系统生成一个顶层文件,这样我们就可以对该系统进行综合、实现并生成bit流了

当bit流生成完成后,在Vivado中最后的工作就是要将设计导入到SDK中,然后对ARM进行编程

Vivado之嵌入式系统设计一---Vivado高效设计案例分享

据说,ISE之后会停止更新(事实还是谣言无从考证)。但是,掌握Vivado开发工具势在必行。缘由一,此处省略一万字……

Vivado提供了直观的具有强大功能的图形用户接口。所有的工具和工具选项栏使用原生的工具命令语言格式编写,这使得既能使用Vivado集成开发环境又能使用Tcl shell。相应地,Vivado有两种设计模式:Project模式和Non-Project模式。两种模式大同小异,一种是使用图形用户界面,另一种是使用Tcl脚本。除此之外,一些特性在Non-Project下不支持,具体参考UG893。相信大多网友跟我一样,习惯了windows下的图形化操作方式,所以如何使用Tcl脚本命令就不在本博文所述之列了。接下来,我会用几篇博客的篇幅跟大家一起学习一下Vivado之嵌入式系统设计。

目标:搭建一个最小的ZYNQ嵌入式系统

首先,先打开Vivado IDE,N种方法任你选;

新建工程,工程名为lab1,存储路径自定义,选中创建工程子目录(所有工程文件存放于此目录,便于管理);

选择RTL工程类型,不选中下面的选项(选中本次不指定源文件选项,跳过创建、添加源文件页面);

目标语言选择VHDL,仿真语言选择Mixed,连续两次Next,跳过添加已存在的IP和约束文件页面,然后选择Xilinx器件或是支持的板卡,此处选择Zedboard板卡选项;

这是建完工程以后,默认显示的界面。略显复杂,但是逻辑清晰,仔细分析,你会豁然开朗,其实就是ISE的升级版本。如果想要了解每个面板的功能,可以参考UG893;

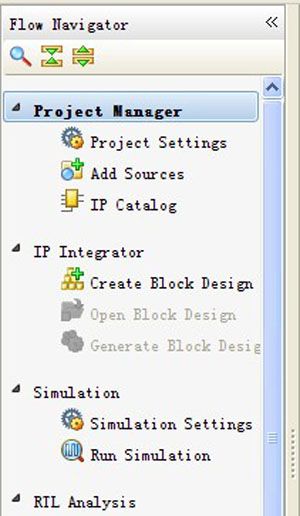

Flow Navigator面板下选择IP Integrator—Create Block Design,输入设计名称system;

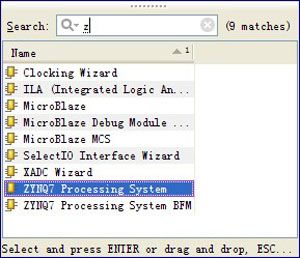

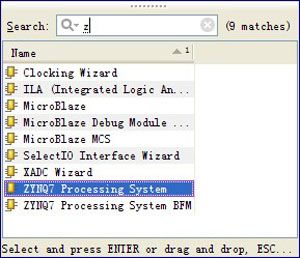

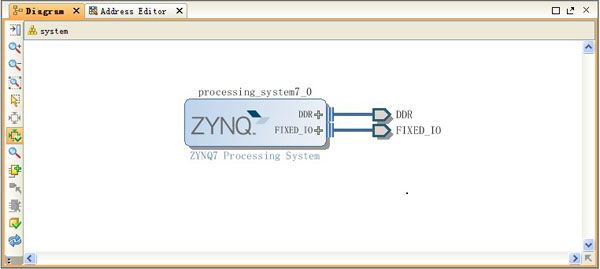

接下来,添加Zynq Processing System到设计中,a、点击Diagram面板上方的Add IP;b、点击Diagram面板左侧的Add IP工具图标;c、在Diagram面板空白处点击右键,在弹出的选项中选择Add IP。在弹出的IP目录中,搜索找到ZYNQ7 Processing System,双击该IP将其添加到设计中;

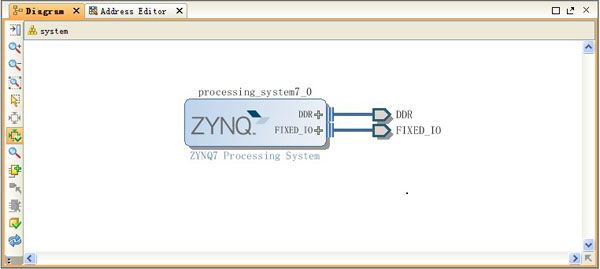

在Diagram面板顶部,运行Run Block Automation,选择processing_system7_0,配置FIXED_IO和DDR接口,此时,我们无法定制ARM核。运行完成后,一个默认配置的Zynq系统已经添加到设计中了。双击ZYNQ系统视图,用户可定制自己的Zynq系统;

配置Zynq系统,只保留UART1;

最后生成的视图如下所示:

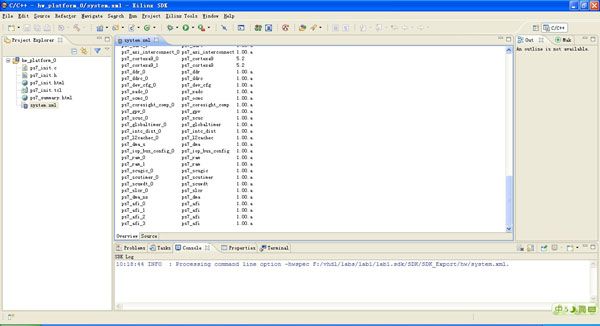

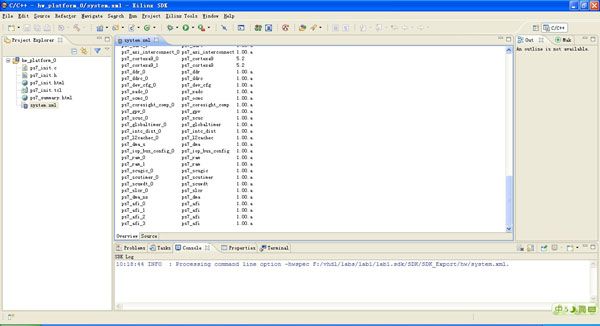

在Sources面板,右击system.bd,选择Generate Output Products,生成设计综合、仿真、实现的相关文件。再次点击system.bd,选择Create HDL Wrapper,生成VHDL顶层模型。接下来,将硬件设计导入到SDK中(注意:导出前,处于Open Block Design模式下)File > Export > Export hardware for SDK…

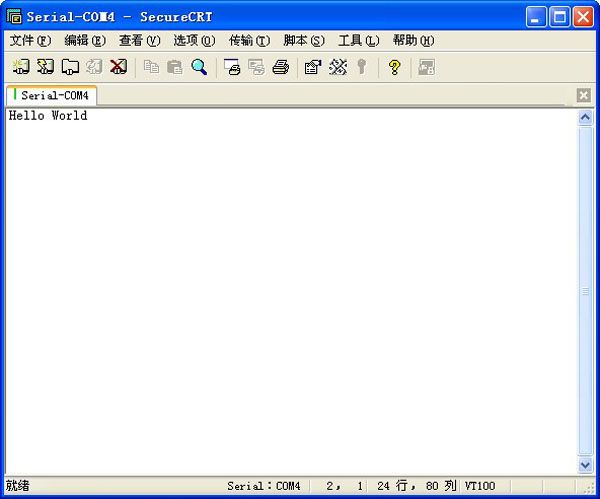

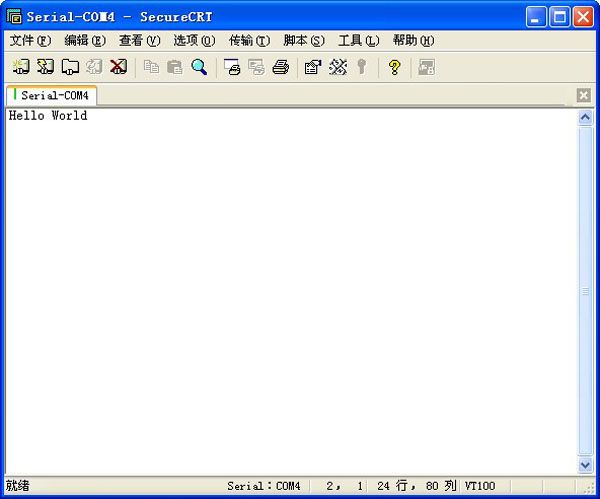

接下来,就是新建应用程序工程、板级支持包等,就不详细介绍了。设置好串口,搭建好Zedboard硬件平台,就能板级测试了,最后结果如下图所示: