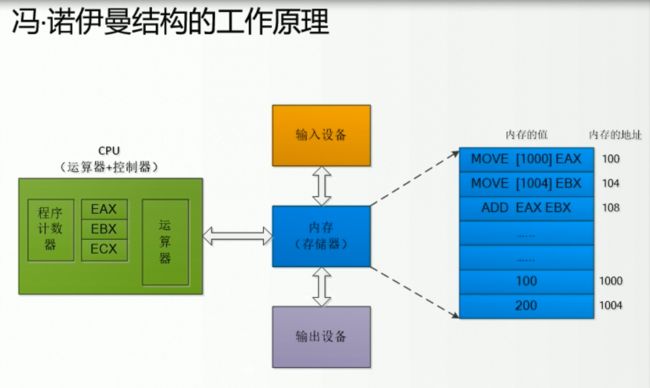

一,冯诺伊曼结构的计算机

1,计算机的五大组成部分

运算器 + 控制器(CPU),存储器(内存),输出设备(显示器),输入设备(鼠标和键盘)。

2,数据和指令以二进制形式,不加区别的存放在存储器中。

数据和指令存储在一块,存储在一个存储器中是风诺伊曼结构的重要标志

内存是一个线性结构,并且内存是有地址的。注意数据和指令是不分的,他们都在一个内存中。

比如,现在要把100和200加起来,那么计算机是如何工作的呢?

第一条指令:MOVE [1000] EAX ,表示把地址为1000处的数据放到寄存器中(EAX)

第二条指令:MOVE [1004] EAX ,表示把地址为1004处的数据放到寄存器中(EBX)

cpu先执行第一条指令,把100放到寄存器中。然后再执行第二条指令,把200放到寄存器中。

第三条指令:ADD EAX EBX

最后cpu执行第三条指令,把两个寄存器中的值加起来,放到EBX中。

4,计算机各个部件是怎么连接起来的?

南桥--北桥:上面的I/O桥就是对南桥和北桥的抽象

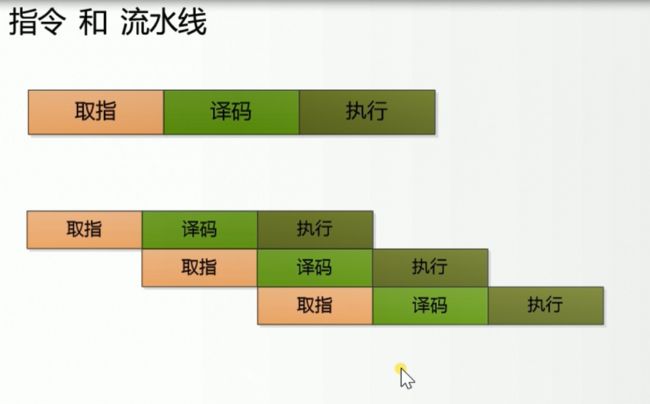

5,指令和流水线

5.1,指令分为:

单操作数指令,比如加1操作

两个操作数指令,比如 MOV [1000] AX

三个操作数指令,非常少

5.2,cpu执行指令是按照流水线的思想来执行的。cpu的一条指令在执行中分为很多步骤。以三步为例:

取指令:从内存中把指令取出来

译码:看看这条指令是做什么的

执行:执行指令

cpu为了做这三件事,分为三个部件。一个部件负责取指令,一个部件负责译码,一个部件负责执行指令。

所以在执行其中一个步骤时,其他两个步骤也没有闲着,可以做自己对应的操作。这样大大提高了cpu的效率。

比如第一条指令执行到 执行这个步骤时,cpu还可以执行第二条指令的译码工作。

5.3,速度对比

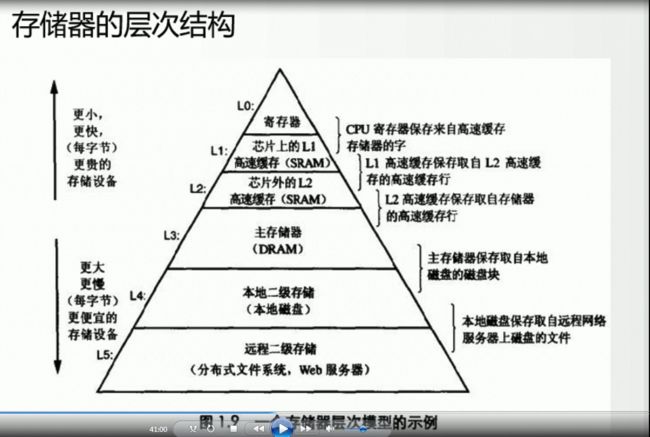

内存访问速度比cpu执行速度慢几百倍,传统磁盘IO访问速度比cpu执行速度慢几十万倍。网络比cpu慢千万倍。速度不匹配问题是计算机的核心问题。

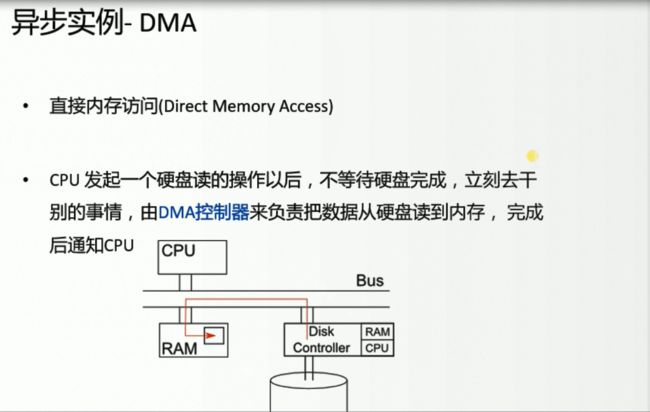

6,如何解决速度不匹配问题?

方案一:提升硬盘等设备的速度,和cpu匹配 ---- 现阶段不可能

方案二:承认局限,但充分压榨cpu的能力。思路如下:

同步 ---->异步

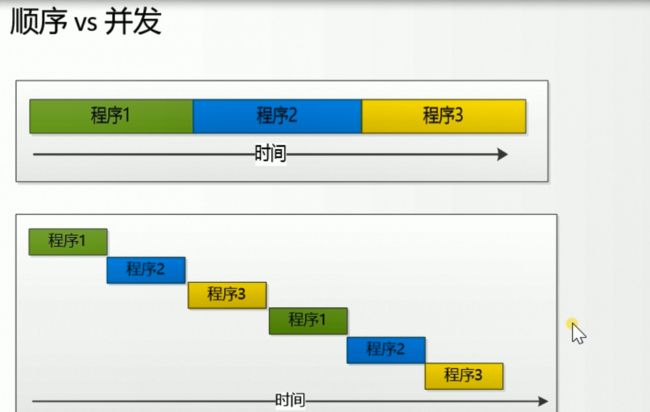

顺序 ---->并发

增加中间层(缓存)

6.1,异步实例

6.2,顺序和并发

顺序:一个时间只能执行一个程序。

并发:通过时间片分配的形式,把cpu分为若干个时间片,让多个程序在一个cpu上分时运行。操作系统负责切换。切换时间片的时间非常短,造成程序并发执行的假象。(这里假定只有一个cpu,多个程序在一个cpu上轮换执行)。

注意:这里是并发,只有一个cpu。由于时间片非常短,看起来是同时执行的。如果有多个cpu,那就是并行了。

并发的实现:时间片的切换

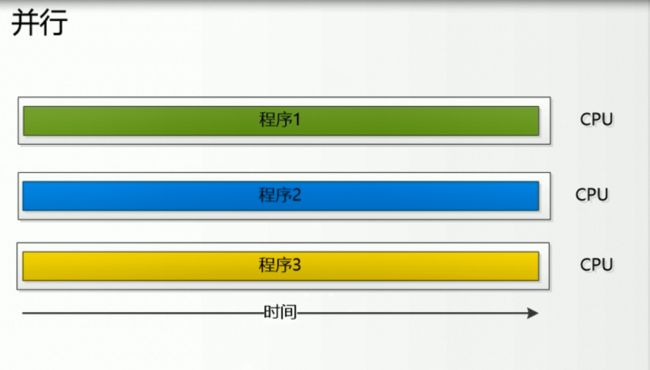

补充:并行

对于多核cpu,多核是每个核都对应一个线程,所以多核就可以同时执行多个线程。那么并行是真的有多个指令在同时执行了。

程序中的一行代码,编译成汇编语言可能就有多条指令了,比如 i = i+1 ;执行的时候会有多条指令,这多条指令如果在多线程情况下没有协调好,执行时可能就会出错。

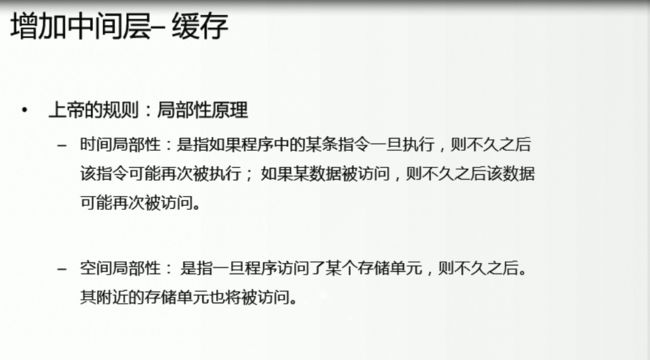

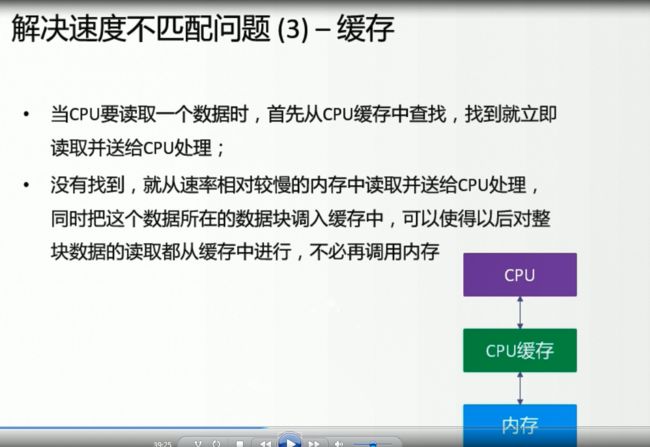

6.3,增加中间层--缓存

时间局部性原理 和 空间局部性原理

解决了速度不匹配的问题。

cpu有一级缓存,二级缓存,三级缓存。从缓存中读取比从内存中读取快的多。

7,存储器的层次结构

二,编程语言

1.解释和编译

解释执行:

解释器读入高级语言写的指令,然后解释执行。比如:Basic

编译:

使用编译器把高级语言编程目标代码,或者是可执行的程序。比如:C语言,C++

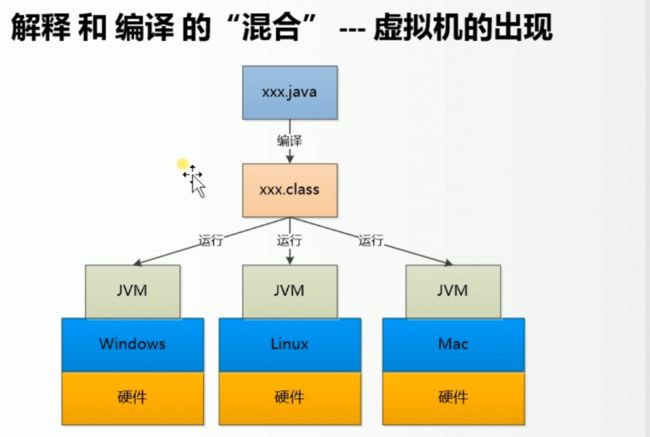

2.虚拟机:解释和编译的混合

Java编译器先把java编译成 .class 文件。然后在各个JVM上解释执行。JVM在每个平台都有版本。由于28原则的存在,如果JVM发现这个 .class文件经常执行,就编译成本地平台的代码。

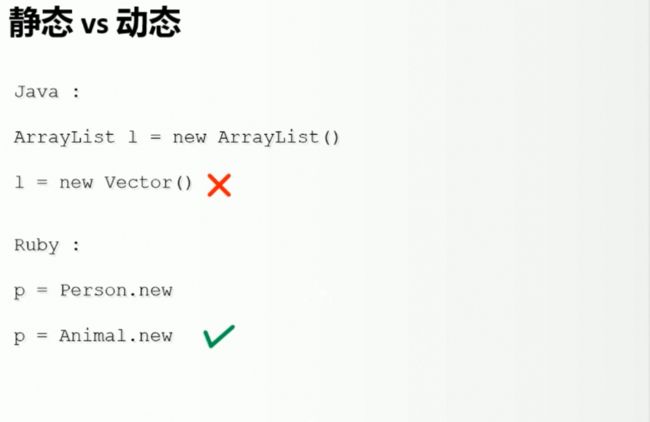

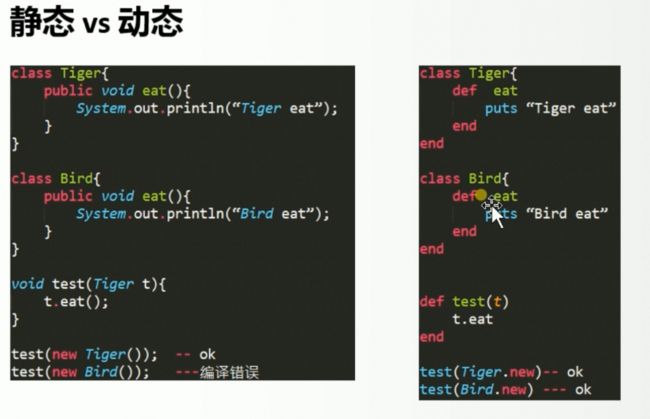

3.静态和动态语言

动态语言比较灵活,但是编译器无法检查。小项目适合快速开发

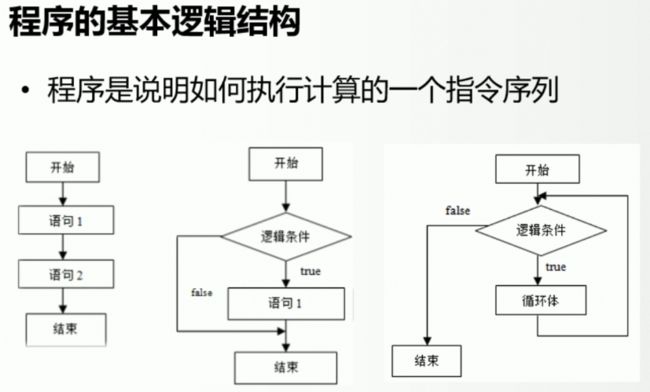

4.程序的基本逻辑结构

这三种结构理论上可以表达一切计算机程序。

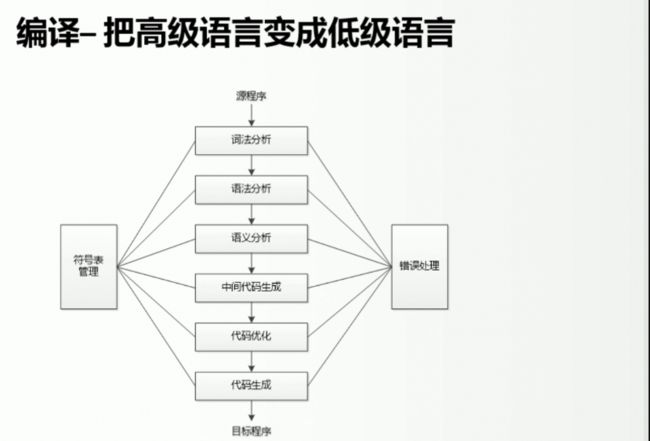

5.编译- 把高级语言变成低级语言

例子:pasic语言代码

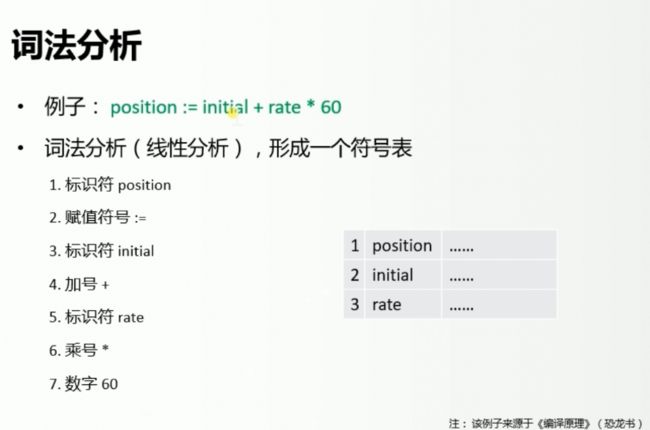

第一步:词法分析

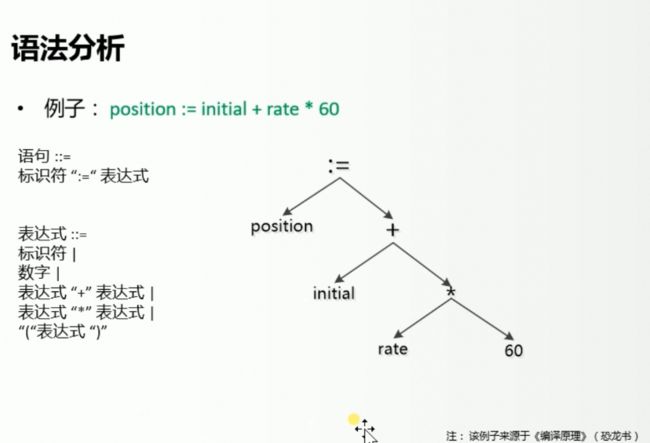

第二步:语法分析

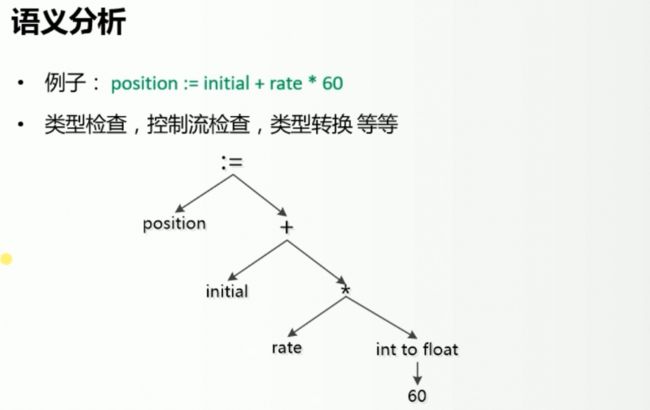

第三步:语义分析

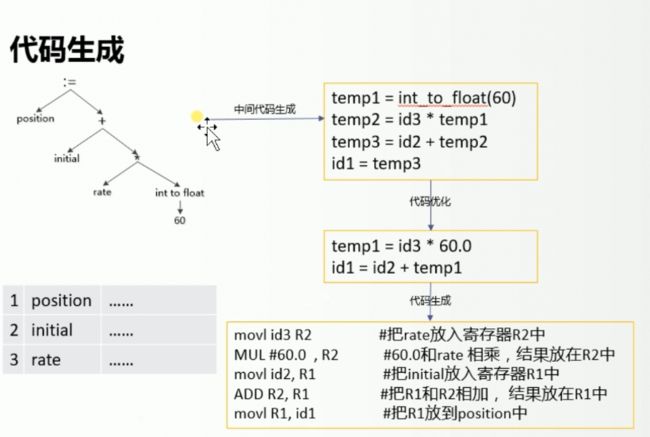

第四步:代码生成

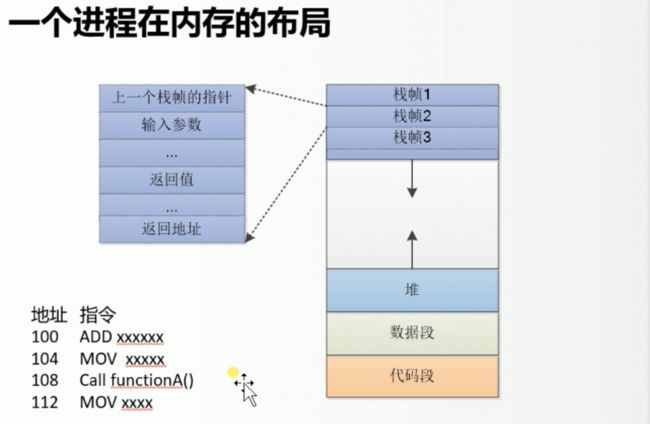

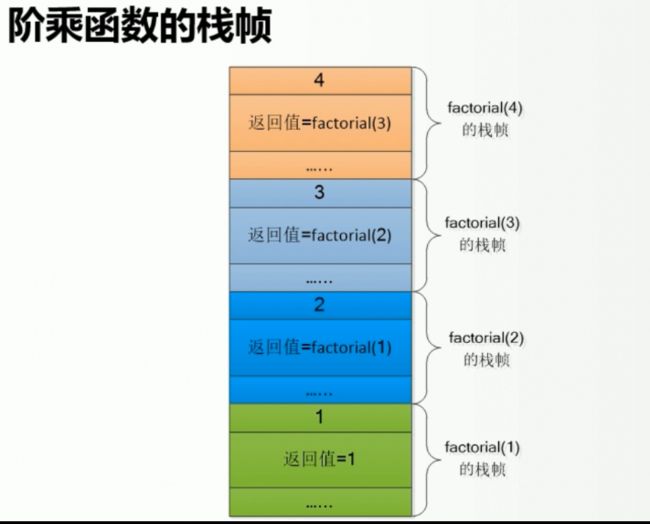

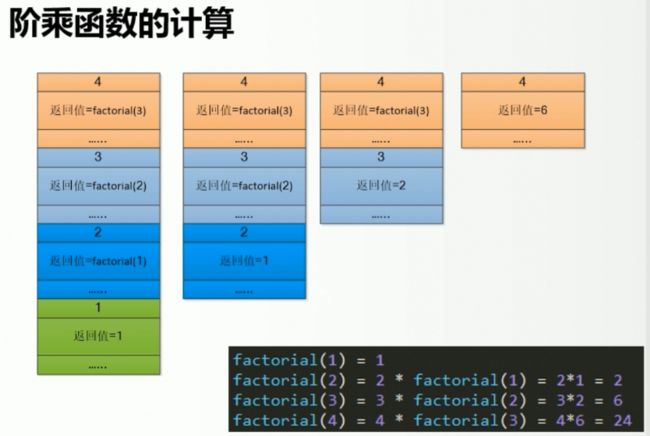

7,递归

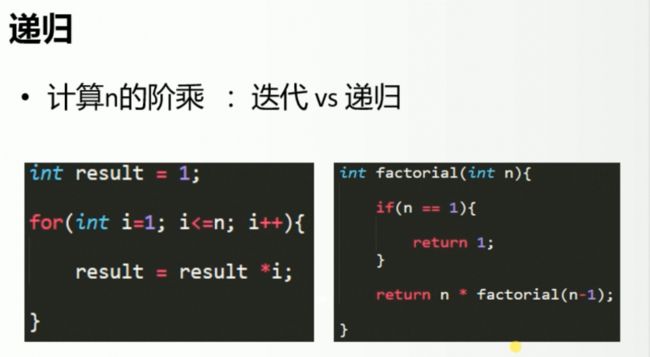

左边是迭代的代码,右边是递归

理解:

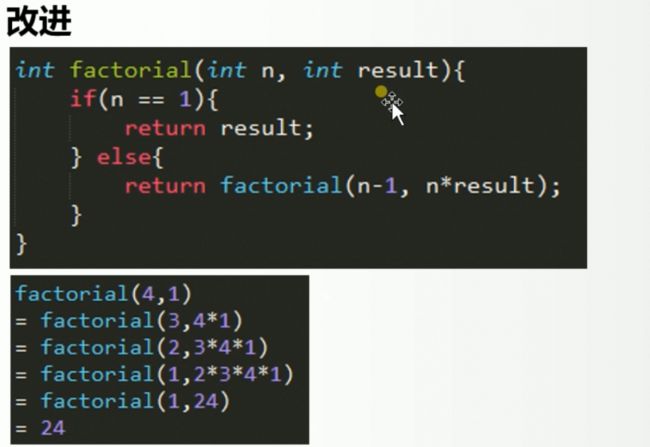

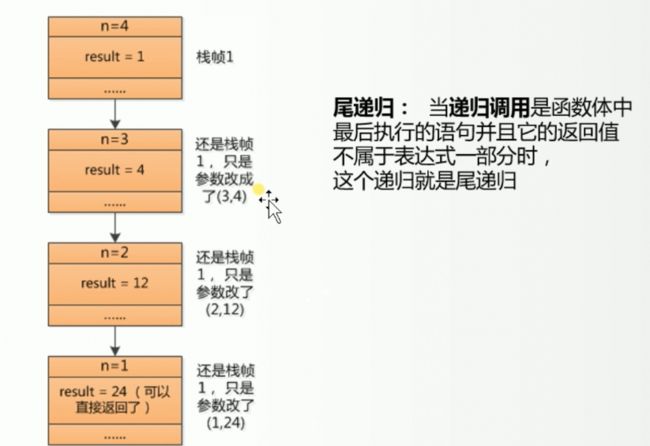

改进:尾递归