Verilog HDL小练习(二)简单的比较器&&三态驱动器

道路是漫长的,学习是一个不断积累的过程,持之以恒最难,有志者事竟成百二秦关终属楚,苦心人天不负三千越甲可吞吴,谨以此与那些朋友们共勉。

1一个二位比较器 ------功能描述-------

构造一个比较器,输入两个2位的量,相等时输出1,不相等时输出0。

module compare(a,b,out);

input [1:0]a,b;

output out;

assign out=(a==b)?1:0;

/*?1:0 表示如if前面a==b,输出1,else,输出0!!!这里?:等同于if else 语句*/

endmoduleNetList如下图所示:

门级电路描述如下:

module compare(a,b,out);

input [1:0]a,b;

output out;

xor(result1,a[0],b[0]);//xor表示异或,相同为0,不同为1

xor(result2,a[1],b[1]);

and(out1,result1,result2);

not(out,out1);

endmodule

2简单三态驱动器

module trist2(out,in,enable);

output out;

input in,enable;

bufif1 mybuf(out,in,enable);//三态就是1,0,高阻

/*!!调用原语库bufif 创建自己的三态驱动器模型也就是库文件的实例化*/

endmoduleNetList如下图所示:

另一种调用形式

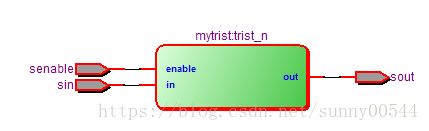

主模块

module trist1(sout,sin,senable);

output sout;

input sin,senable;

mytrist trist_n(.out(sout),.in(sin),.enable(senable));

//实例化自己的mytrist “.”表示引用的模块的端口,“()”表示端口连线

/*!!调用原语库bufif 创建自己的三态驱动器模型也就是库文件的实例化*/

endmodule子模块mytrist

module mytrist(out,in,enable);

output out;

input in,enable;

assign out=enable?in:1'bz;

//当使能为1,时out=in,否则out=bz;!!注意此处高阻表述前要加位数1

endmodule这些通过综合工具都可以转化成与门,或门,非门组成的加法器,比较器,三态门等,设计人员不必纠结于细节逻辑,底层已经可以映射了。只需要关注系统结构的考虑上,从而提高设计效率。

- 不积跬步无以至千里,今天就讲到这,不足之处,请多指教!欢迎提问我*_*.